引 言

跟着片上体系(SoC,System on Chip)年代的到来,包含杂乱可编程逻辑器材(CPLD,Complex ProgrammableLogic Devi(e)和现场可编程门阵列(FPGA,Field Programmable Gate Array)的可编程逻辑器材(具有在体系可再编程的共同长处),运用越来越广泛。这给用于可编程逻辑器材编程的下载电缆提出了更高的要求。

本文研讨根据IEEEll49.1规范的USB下载接口电路的规划及完结。针对Altera公司的FPGA器材Cy-ckone,经过剖析它的鸿沟扫描测验结构和各种JTAG指令,研讨它的编程进程和编程特色,并提出规划方案。在接口电路硬件规划中,选用FTDI公司的USB操控芯片FT2蛎BM,完结USB物理层和链路层协议的解析;Altera公司的可编程逻辑器材EPM7064完结接口逻辑。与传统的根据PC并口的下载电缆比较,本规划的USB下载接口电路具有支撑热插拔、体积小、便于带着、下降对PC硬件损伤、编程速度快等显着长处。

现在已开发的USB下载线一般需求在主机端另行规划软件来操控与下载线及方针器材之间的通讯和数据传送;可是这样不只繁琐,而且或许由于PC机操作体系的不同而影响兼容性。本文评论的USB下载线能在A1tera公司的QuartusII开发环境下直接运用,无须在主机端另行规划通讯软件。

1 体系结构及作业原理

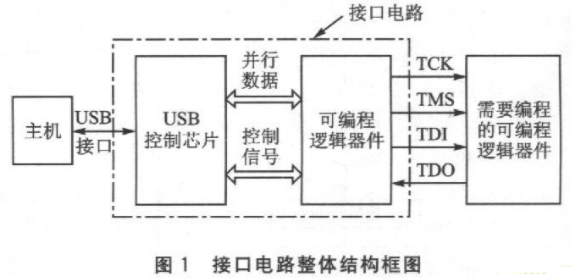

接口电路的全体结构框图如图l所示。由于USB下载电路触及了IEEEll49.1规范和USB协议,所以接口电路首要包含两大部分。一部分是USB接口,它衔接主机和可编程逻辑器材,首要功能是进行USB和并行I/O口之间的数据格式转化,用USB操控芯片完结。另一部分是JTAG接口,它衔接USB操控芯片和需求编程的逻辑器材,首要功能是进行并行I/O口和JTAG之间数据的转化,转化逻辑经过对可编程逻辑器材进行规划来完结。其他还包含一些必要的时钟电路和电压转化电路。

从主机传来的USB数据,由USB操控芯片转化为8位并行数据,经数据总线送到CPLD的可编程I/O引脚。CPLD的数据也可以经过数据总线送回USB操控芯片,然后转化为USB的数据格式传回主机。CPLD收到USB操控芯片传送来的数据后,对数据进行解析,然后转化为契合IEEEll49.1规范的编程数据和指令,从TCK、TMS和TDI串行输出到要编程的可编程逻辑器材。从可编程逻辑器材回来的契合IEEEll49.1规范的校验数据从TDO串行输入到CPLD,转化为8位并行数据传送给USB操控芯片,最终回来主机进行校验。[page]

USB操控芯片FT245BM担任解说USB协议,完结两边数据通讯。其内部有USB协议引擎,而且集成的电平转化器使FIFO和操控信号能与电压为5 V、3.3 V的逻辑器材接口。USB接口电路原理如图2所示。

2 对方针器材的装备进程

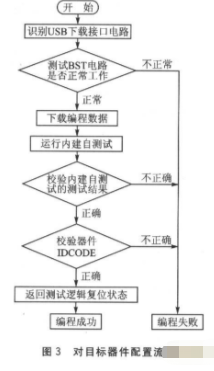

对方针器材的装备流程如图3所示。

(1)辨认USB下载接口

Quanus II编程器经过PC的USB接口向FT245BM顺次发7e、7f、7c三个数据。FT245BM经PC的USB接口向编程器顺次回来3个数据03。在编程器收到回来的3个03今后,编程器就辨认此USB下载接口电路为它的下载硬件渠道。

(2)测验BST电路

测验包含以下几个方面:

复位测验;

指令寄存器移位测验;

标志寄存器移位测验。

(3)下载编程数据

这个进程把一切的编程数据从PC下载进可编程逻辑器材的装备存储器。由于这一进程下载的编程数据巨大,所以下载时选用特快形式,而且不进行校验,防止影响下载速度。下载选用的指令是Ahcra公司自己界说的DOWNLOAD指令(00 0000 0010)。

(4)内建自测验

内建自测验是在电路内部树立测验生成、施加、剖析和测验操控结构,使得电路可以测验自己。

(5)校验器材的IDCODE

在整个编程流程完毕曾经,再一次校验器材的ID—CODE,承认器材的BST电路在下载编程数据后足否作业正常。这一步的进程和标志寄存器移位测验完全相同。

(6)回来测验逻辑复位状况

坚持TMS为高6个TCK周期,使TAP操控器进入测验逻辑复位状况,而且让TMS坚持为高电平,以坚持测验逻辑复位状况。这样器材的测验逻辑失效,器材的中心逻辑开端正常作业。

结语

本文所评论的USB数据下载线能在Altera公司的QuartusII开发环境下直接运用,无须另行开发主机端通讯程序。与传统并几的编程方法比较,优势非常显着:支撑热插拔,运用更便利;体积更小,带着便利;编程速度更快,节省时刻。为世界数字体系规划领域内正繁荣鼓起的在线编程(ISP)技能的推行与开展供给了有力的支撑。

责任编辑:gt