1 布景介绍

在日益信息化的社会中,各式各样的嵌入式体系现已全面渗透到日常日子的每一个旮旯。嵌入式体系的功用越来越杂乱,这就使得一个嵌入式体系产品从市场需求立项到计划挑选、样机研发、定型量产所需求的开发费用越来越多,所需开发时刻越来越长。因而,高效的嵌入式体系规划办法就显得尤为重要。

1.1 传统的嵌入式体系规划办法

嵌入式体系开发的要害便是对中心部分进行功用验证。传统的验证办法是建模模仿和制造方针板评价。

经过建模来进行功用验证存在缺乏。首要便是耗时和精确性互相矛盾。树立高层次的模型需求的时刻短,可是模仿不行精确。相反,低层次的模型能够到达满足的评价作用,可是建模耗时长。其次,建模模仿是静态的进程,不能很好地反映体系实践运转的状况。好的方针板,各部分衔接现已固定。假如需求改动部分衔接,只能从头规划制版。这样一来就会大大延伸产品的上市时刻,还会添加开发费用。新推出的嵌入式体系产品,开端规划时比较难把一切的技术细节考虑清楚,有时乃至是边规划边修正性能指标,因而直接制造专用的方针板原型现已不太合适杂乱的嵌入式体系产品的规划。

1.2 嵌入式体系模块化规划办法

嵌入式体系规划要求做到可测性、高效性和灵敏性。现在,嵌入式体系物理尺度越来越小,功用越来越杂乱。为了便利调试、保护体系,彻底可测显得极为重要。另一方面,模块化的规划办法越来越引起人们的重视。模块化规划办法将杂乱的体系合理地划分出不同的功用模块,然后充分运用已有的模块,规划新的模块,最终将这些模块衔接起来组成方针体系。模块化的规划办法削减全新的规划、下降开发难度、节约开发本钱、缩短开发时刻,是一种高效的嵌入式体系规划办法。别的,各个模块衔接的灵敏性是十分重要的,它直接决议模块的组合才能。

2 根据ARM核的快速原型化渠道

嵌入式体系硬件有如下特色:

1、嵌入式硬件以嵌入式处理器为中心。嵌入式处理器的品种许多,功用各异。

2、相对嵌入式处理器,嵌入式体系外设的品种较少,接口标准也比较一致。

3、跟着EDA的开展,SOC(system on Chip)的运用越来越广泛。

2.1 ARM核处理器的特色

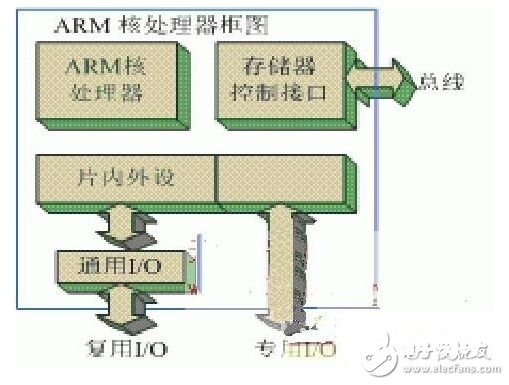

ARM核处理器由于其低本钱、低功耗、高性能的长处广泛运用于嵌入式体系。根据ARM核处理器是高度集成的SOC,包含ARM核和各式各样的外设。图1是根据ARM核处理器的常见结构。存储器操控接口为外接存储器供给了总线接口。该总线接口支撑不同品种的存储器芯片以及不同的存储操作。此外,还能够用该总线来扩展外设。片表里设包含中止操控器.html“ target=”_blank“》操控器、OS定时器、UART、I2C、PWM和AC97等等。在这些片表里设中,有些信号是复用的,这样做的优点是便运用户运用。用户如需求片表里设,只需求装备相关的存放把片表里设衔接到通用I/O即可,十分灵敏,例如USB接口的服务器/客户端。有些片表里设有专用的信号。用户经过衔接或许扩展这些通用I/O和专用I/O来运用片表里设。当片表里设不能完结方针体系的功用时,需求经过总线来扩展特别的外设芯片。

图1(ARM核处理器框图)

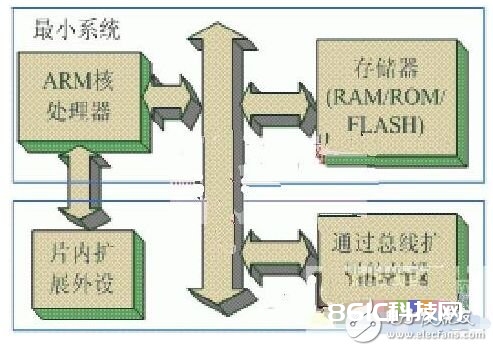

图2 (ARM核处理器的嵌入式体系的框图)

2.2 根据ARM的快速原型化渠道的完结

图2是根据ARM核处理器的嵌入式体系的框图。该体系分红两个部分,一部分是最小体系,由嵌入式ARM核处理器和存储器组成;别的一部分包含从嵌入式处理器片表里设接口直接扩展的外设和经过总线扩展的外设。为了充分运用模块化规划办法,这些部分应该能够经过灵敏的互连组成一个渠道。灵敏的互连功用由互连模块完结。

可编程器材如CPLD和FPGA,能够在体系编程,修正衔接只需求修正相应的操控程序即可,十分便利灵敏。CPLD本钱低,运转速度快,可是集成度比较低。FPGA集成度高,能够完结CPLD很难完结的杂乱的逻辑功用,例如内嵌逻辑剖析仪程序,获取必要的信号,完结体系在线测验。FPGA别的一个优势便是能够动态装备,例如体系上电时装备自检程序,自检经往后再装备实践作业的程序。最终,在FPGA里边嵌入CPU软核,进行SOC的开发。所以可编程互连模块选用FPGA来组成。

为了确认可编程互连模块的刺进方位,再来剖析图2嵌入式体系的结构。

最小体系决议了整个体系的处理才能,是整个体系的中心。常用的嵌入式处理器的时钟周期现已高达400MHz,并且会进一步开展。衔接处理器的总线速度和存储器芯片的速度也超过了100MHz。FPGA引脚到引脚的延时是几个纳秒的数量级,所以FPGA模块的刺进会下降整个体系的处理速度。故在处理器和存储器之间不能刺进FPGA模块。外设能够使得嵌入式体系和实践运用环境进行通讯和交互操作。一般外设现已高度模块化并且彼此独立,在外设之间简直不会有柔性衔接的要求,并且处理器和外设之间的数据通讯速度比最小体系的运转速度要慢许多。因而,用互连模块替代最小体系和外设之间的直接物理衔接是切实可行的。

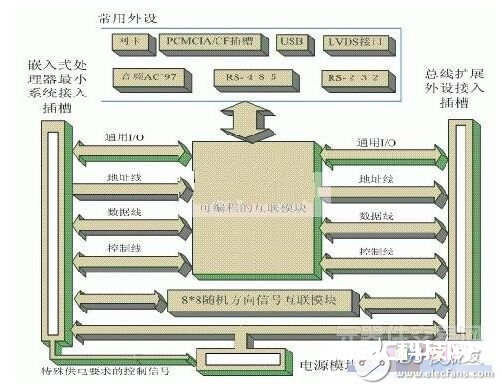

依照这种思路,规划出了如图3所示的快速原型化渠道。

图3(快速原型化渠道)

图3中,可编程互连模块是快速原型化渠道的中心部分。常用的外设部分包含:网卡,USB接口,LVDS接口,RS-232接口,rs-485/’ target=’_blank’>RS-485接口,音频AC`97接口,PCMCIA/CF卡接口。这些常用外设便是前文说到的可重复运用的模块。由于嵌入式处理器的总线、通用I/O、专用I/O和各种外设都衔接在可编程互连模块上,因而不同的嵌入式处理器只需求规划最小体系即可,然后将该最小体系接入快速原型化渠道,运用这个渠道供给的外设进行体系调试。

以上规划的快速原型化渠道,不只考虑了当时嵌入式硬件体系的开展特色即嵌入式处理器品种多,外设品种相对较少,接口标准趋于一致,一起又充分体现了可测性、灵敏性、模块化的规划思维。

3 随机方向信号的可装备互连

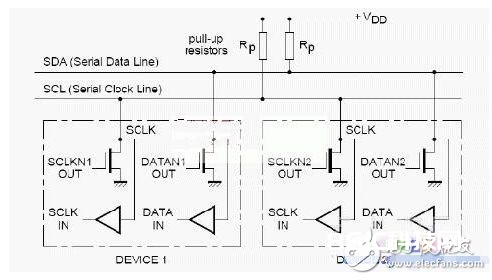

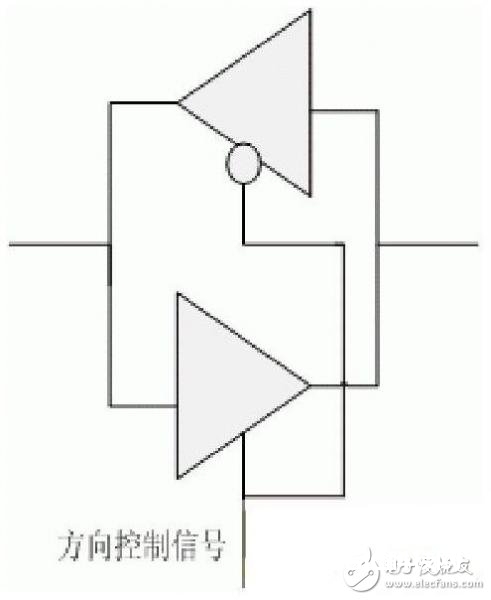

常见的信号传输方向不管是单向的仍是双向的,都能够预先确认。例如,数据总线是双向的,读或许写是彻底确认的,能够经过读写信号来操控数据的传输的方向。可是有一类特别的总线,例如I2C,它是多主/从的通讯总线。如图4所示,假如设备1建议通讯,则SCL上的信号传输方向是从设备1到设备2,假如是设备2作主设备建议通讯,则SCL的上的信号传输方向刚好相反。体系规划中要求总线上能够双向传输信号。FPGA内部由一系列的逻辑门组成,假如I2C 信号经过FPGA来衔接的话,就不能正常作业。这是由于,双向传输能够等效视为由两个反并联的门来完结(如图5,用方向操控信号来确认实践的传输方向)。可是,I2C信号,没有清晰的方向操控信号,也就无法正确地经过图5 所示结构的电路。

图4(I2C总线)

图5(双向信号传输)

假如直接布线或许跳线来衔接I2C信号,就能够确保I2C正常作业,可是,这就和快速原型化渠道可装备互连的灵敏性相违反,所以提出以下计划。 I2C信号不经过FPGA来装备衔接,而是经过根据MOSFET的数据开关。现在,市场上常用的点到点恣意方向的MOSFET开关并不能直接运用。由于常见的结构是一路到多路或许多路到一路。运用CPLD来操控选通,多路并联就能够组成8X8的点到点的随机方向的可装备衔接。是一路到八路的数据开关的内部结构。