0 导言

卫星通讯体系中,在信号发射前需要对频谱较宽的基带信号进行成形滤波处理,以改进其频谱特性,在消除码间搅扰(Inter Symbol Interference,ISI)与到达最佳检测接纳的前提下,进步信道的频带使用率。通讯体系中选用发送端的成形滤波器和接纳端的匹配滤波器一起完成升余弦滤波的作用,对信号进行滤波处理。因为平方根升余弦(Square Root Raised Cosine,SRRC)具有较快的衰减特性和较好的可完成性,一般选用SRRC滤波器完成通讯体系的基带成形滤波[1]。

多速率改换常用于通讯体系中的信号处理,经过内插(上采样)或抽取(下采样)改动信号的采样频率,并对信号滤波处理。卫星通讯的高带宽通讯事务及AD转化率的进步,促进了通讯体系发射端对不同符号率信号采样率的进步。在通讯体系的接纳端,过高的采样率和数据吞吐量不利于数据的实时处理,需要对信号降采样处理。

FPGA以其并行处理及灵敏可编程特性,广泛用于基带信号处理[2]。本文依据FPGA规划一种多速率改换器进步信号的采样率,完成恣意倍数的符号率改换(本文首要完成了上采样改换,下采样完成办法相同)。选用SRRC滤波与半带(Half-band,HB)滤波器、级联积分梳状(Cascade Integrator Comb,CIC)滤波器、Farrow滤波级联进行上采样,完成平方根升余弦滤涉及信号恣意倍数的上变频处理。其间,针对不同的滚降系数,SRRC滤波器的滤波系数可重载;CIC及Farrow滤波器上采样倍数在线可重载。该多速率改换模块有用节省了FPGA资源,高效、完成简略,并可以完成恣意倍数的多速率改换。

1 SRRC滤涉及各变速率模块

1.1 SRRC滤波

1.1.1 SRRC的完成原理

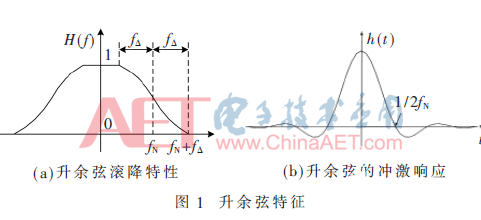

当信道传输函数的幅频特性满意滚降系数为a的升余弦滤波器特征时,可以完成无码间串扰传输[3],如图1所示。

图1(a)为升余弦滤波器的滚降特性,fN是奈奎斯特带宽。图1(b)是升余弦特性的时域特征,图中箭头所指为最佳采样点,可以看出:满意无码间串扰的最大传输速率为2fN。

其间a是滚降系数,决议升余弦的滚降特性。当a=1时具有理性低通特性,a越大,旁瓣衰减越快,信号成形滤波后的波形对位守时精度要求越低。

在通讯体系的发射端和接纳端一起运用SRRC滤波器可以完成升余弦滤波的作用,消除码间搅扰。SRRC滤波器在发射端用做成形滤波,在接纳端用做匹配滤波。成形滤波能有用战胜码间搅扰,减小误码率,进步整个通讯体系的功能。匹配滤波则能批改码间搅扰带来的信号畸变,完成最佳接纳。

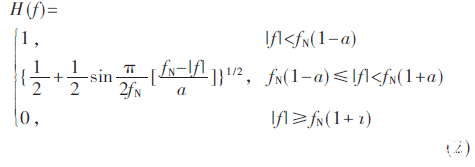

SRRC滤波器传输函数如式(2)所示[4]:

式中,fN为奈奎斯特带宽,a为滚降系数。

1.1.2 SRRC的滚降系数重载

本文中选用Xilinx IP核完成系数可重载式SRRC滤波,滚降系数有0.25和0.35两种,可以在线重载。

选用IP核完成系数重载时,可以将几组verctor合并为一组,也可将几组滤波器系数放到一个coe文件中,经过IP核中config端口来重载Fir IP核的滤波系数[5]。

在生成IP核时,将Number of coefficient sets设置为N(假设有N组滤波器系数),经过装备s_axis_config_tdata端口值为M(M≤N-1),可以挑选第M+1组系数进行SRRC滤波,便于工程使用时滤波系数的批改。

本文中选用MATLAB的Fdatool东西生成SRRC滤波器系数,只需装备好滚降系数a、信号传输速率、奈奎斯特速率等,操作简洁、高效。

Fdatool装备页面中,信号传输速率应至少等于传输带宽B的两倍,即:

式中,FS为信号传输速率,FC为奈奎斯特速率。

1.2 CIC滤波

1.2.1 CIC滤波的完成原理

CIC滤波器是零极点相消的滤波器,结构简略,功率高。当采样频率的改换较大时,因为抗混叠的优越性,选用CIC滤波作用更好。

CIC滤波器的一级阻带衰减为13.36 dB,M级阻带衰减为13.36M dB[6]。M增大可以增大阻带衰减和旁瓣按捺,但受通带带内容限的约束,M一般不大于5。上采样因子D决议CIC滤波器的主瓣宽度和CIC滤波后的采样频率,实践使用中应依据需求设定。

CIC滤波器完成简略,不需要滤波系数。装备CIC滤波器IP核时,滤波器体系时钟要为输入数据时钟的3倍。

1.2.2 CIC滤波器多速率改换倍数在线重载

本文中CIC滤波器选用CIC IP核完成。在完成过程中,装备CIC滤波器IP核为内插倍数可编程[7],能增强代码的可重用性,有用进步FPGA的资源使用率。

具体完成办法:装备采样率改换为programmable,采样率改换的规模为Minimum Rate,Maximum Rate。则在S_axis_config_tvalid上升沿有用的前提下,经过批改S_axis_config_tdata[7:0]为N,可以完成CIC滤波器的N倍上采样,然后完成CIC滤波器上采样倍数的在线重载。

1.3 HB滤波

HB滤波是偶对称,奇次线性相位的高效数字滤波器,可用于完成2N的抽取或内插,具有运算复杂度低、实时性强的特色。HB滤波器级联在CIC滤波器后,HB可以对CIC滤波器的主瓣增益进行批改,对其间含有较大混叠能量的频率区域进行按捺[8]。

HB的冲击呼应h(k)为实数。HB滤波器的系数具有偶对称特性,如式(4)所示,偶次系数为零,运算量可以削减一半,具有很高的完成功率[9]。

其间:N为滤波器阶数,为奇数。

HB滤波器是一种特别FIR滤波器,选用FIR IP核完成。由FDATOOL东西生成滤波系数,保存为coe文件加载到IP核中。

1.4 Farrow滤波器

Farrow滤波器则可以完成小数倍的速率改换。Farrow滤波器选用3次内插滤波器的Farrow结构,可经过调制数字推迟改动频率转化的份额。Farrow结构的滤波器用于内插时,具有去镜像的性质。

1.4.1 Farrow滤波器的完成原理

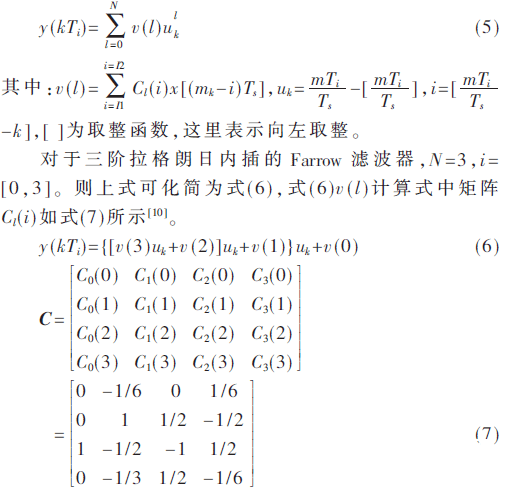

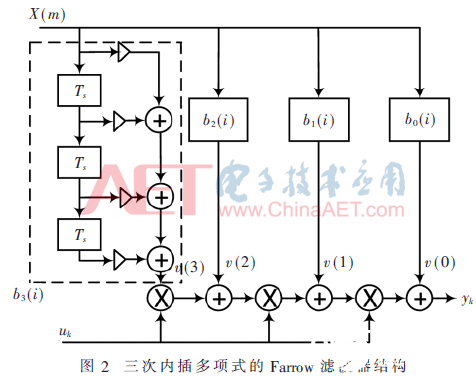

本文经过Verilog编程可以完成三阶内插Farrow滤波器。依据Farrow滤波器的输入输出数据频率,经过调制数字推迟uk改动频率转化的份额。

设输入信号周期为Ts,输出信号的周期为Ti。则:

则三次内插多项式的Farrow滤波器结构如图2所示。

1.4.2 Farrow滤波器上采样倍数在线重载

由Farrow滤波器的完成原理可知:在输入信号周期为Ts时,调制数字推迟uk可以完成,可以调整输出信号的周期为Ts,终究完成信号采样率的改换。也即完成Farrow滤波器上采样倍数在线重载。在工程完成过程中,经过扩大uk来进步精度。

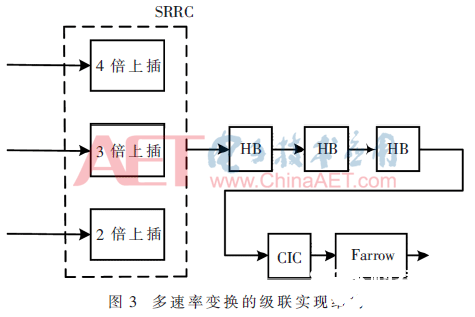

2 SRRC滤涉及多速率改换的完成

在本文中的多速率改换模块,选用3个SRRC滤波器可选,3个级联2倍内插HB滤波器,1个9种内插倍数的CIC滤波器,以及1个3阶内插的Farrow滤波器级联完成。该多速率改换模块的级联结构如图3所示,经过Verilog编程能完成输入信号恣意倍数的上采样改换。

多速率改换的倍数由参数fir_array[16:0]操控。

fir_array[16]=1表明选用Farrow滤波器;fir_array[16]=0表明不选用Farrow滤波器。Farrow滤波器内插倍数由uk操控。

fir_array[15:6]表明CIC滤波器内插倍数。CIC内插倍数共有4、5、6、7、8、9、10、14、21几个等级,与SRRC、HB、Farrow级连可以满意恣意符号率改换的需求。fir_array[15:6]=0则表明不选用CIC滤波器。

fir_array[5:3]操控选用级联的2倍内插HB滤波器的个数(共有3个级联HB滤波器可选)。

fir_array[2:0]操控SRRC滤波器选用的内插倍数,fir_array[2:0]别离表明4倍、3倍、2倍内插。

当输入信号为2 MHz,要上采样到168 MHz,则经过fir_array设置为{1′b1,10′b0001000000,3′b001,3′b100},经过4倍内插的SRRC滤波,一个2倍HB内插滤波,10倍CIC内插滤波,一级160 MHz到168 MHz的Farrow内插滤波完成。

在ISE平台中,采样IP核fir_compiler 6.3与MATLAB的FDATOOL东西一起完成了系数可重载式SRRC滤波器和HB滤波器的规划,选用依据AXI总线的cic_compiler 3.0 IP核完成插值倍数可重载的CIC滤波器,Farrow滤波器则依据三阶内插结构选用Verilog言语编程完成。

其间,SRRC滤波和HB滤波系数均选用FDATOOL东西发生,48阶,汉明窗。HB滤波器采样率为100 MHz,截止频率为25 MHz。SRRC滤波器的采样率为100 MHz,截止频率为25 MHz。

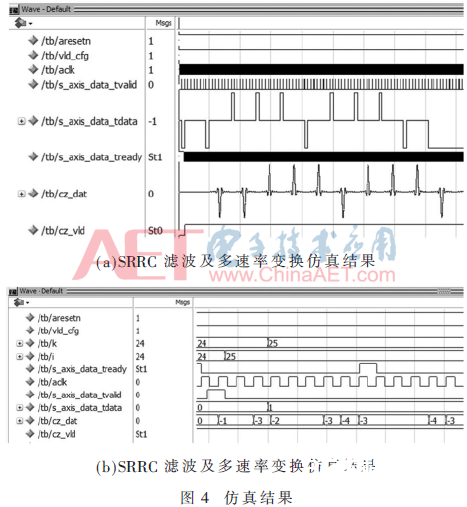

设置仿真时钟为168 MHz,输入信号的速率为2 MHz。数据源为10个随机数X(-1,-1,1,1,1,-1,1,1,1,-1)8倍内插,插值为0得到的。经过ModelSim仿真东西进行仿真验证,仿真成果如图4所示。

从图4(a)可以看出:SRRC滤波并变速率后,仿真波形为升余弦波形,和输入信号根本共同,且具有较好的滑润性。体系时钟aclk为168 MHz,则从图4(b)可以看出:对输入信号SRRC滤波并进行多速率改换后,信号速率上采样到168 MHz。

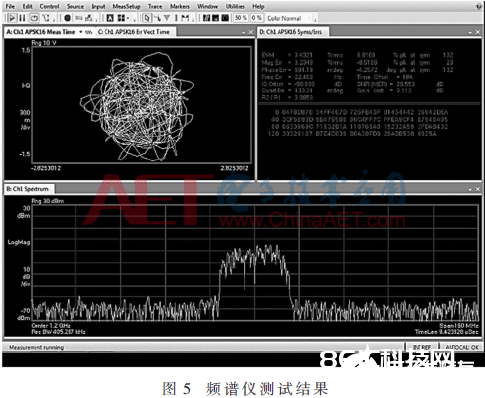

3 试验验证

在试验板上,将20 MHz符号率的16APSK调制信号经SRRC滤涉及多速率改换模块(上采样到168 MHz)、DA转化模块及射频输出后,用频谱仪调查射频输出信号的星座图、信号质量及带宽,如图5所示。

频谱仪测验成果表明:16APSK调制信号经SRRC滤波处理及多速率改换后,输出信号的带宽有用约束到了20 MHz,且能正常解出16APSK星座图,信号EVM约为3%,即有用消除了码间搅扰。其间,EVM(0%~100%)越小,表明输出调制信号的质量越好。

4 定论

本文具体介绍了一种依据FPGA完成SRRC滤涉及多速率改换模块的办法。该模块经过级联SRRC、HB、CIC、Farrow滤波器完成,经过在线重载SRRC滤波系数,CIC、Farrow滤波器插值倍数,可以完成不同滚降系数的升余弦滤涉及多速率改换,有用节省了FPGA资源。经过仿真剖析和试验验证了该模块SRRC滤涉及多速率改换特性。该模块易于工程完成,能有用消除码间搅扰,进步频带使用,较好地满意了现代通讯与数字体系处理中的实时性要求。

参考文献

[1] SREEVIDYA N,SATEESHKUMAR H C.SRRC filter implementaTIon as per DVB-S2 standard[J].InternaTIonal Journal of InnovaTIve Research and Development,2013,2(5):1148-1161.

[2] 冯佳梅,邹刚,朱南,等。依据可变带宽多速率处理算法的规划与完成[J]。数字通讯国际,2015(8):21-25.

[3] 樊昌信,曹丽娜。通讯原理[M]。北京:国防工业出版社,2012.

[4] VANUKURU H R,YOGESH P K R,RAVICHANDRAN V,et al.Performance analysis of root raised cosine filtering in CCSDS ACM[C].InternaTIonal Conference on Wireless Communications,Signal Processing and Networking,2016.

[5] Xinlinx Inc.LogiCORE IP FIR Compiler V6.3 DS795[Z],2011.

[6] cic滤波器的FPGA完成[EB/OL].2016-06-04].http://blog.sina.com.cn/s/blog_4b1046f80102wjrh.html.

[7] Xinlinx Inc.LogiCORE IP CIC Compiler V3.0 DS845[Z].2011.

[8] 曹检飞,文双春,刘昱,等。多速率软件无线电数字中频体系的研讨与完成[J]。计算机工程与科学,2017,39(6):1079-1086.

[9] 娄阳,王中训,快乐龙,等。数字下变频DDC的规划与FPGA完成[J]。我国集成电路,2017,26(Z1):52-56.

[10] 陈沁.QAM信号的位同步与盲均衡完成技术研讨[D]。成都:电子科技大学,2014.