一、根据乘积项(Product-Term)的PLD结构

选用这种结构的PLD芯片有:Altera的MAX7000,MAX3000系列(EEPROM工艺),Xilinx的XC9500系列(Flash工艺)和LatTIce,Cypress的大部分产品(EEPROM工艺)

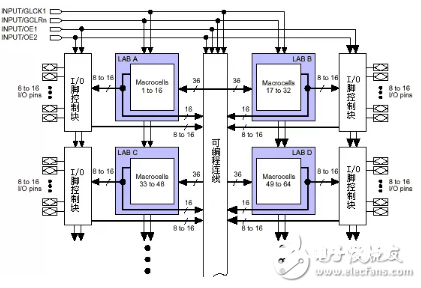

咱们先看一下这种PLD的整体结构(以MAX7000为例,其他类型的结构与此都十分类似):

图1 根据乘积项的PLD内部结构

这种PLD可分为三块结构:宏单元(Marocell),可编程连线 (PIA)和I/O操控块。 宏单元是PLD的根本结构,由它来完结根本的逻辑功用。图1中兰色部分是多个宏单元的调集(由于宏单元较多,没有逐个画出)。可编程连线担任信号传递,连 接一切的宏单元。I/O操控块担任输入输出的电气特性操控,比方能够设定集电极开路输出,摆率操控,三态输出等。 图1 左上的INPUT/GCLK1,

INPUT/GCLRn,INPUT/OE1,INPUT/OE2 是大局时钟,清零和输出使能信号,这几个信号有专用连线与PLD中每个宏单元相连,信号到每个宏单元的延时相同而且延时最短。

宏单元的详细结构见下图:

图2 宏单元结构

左边是乘积项阵列,实践便是一个与或阵列,每一个交叉点都是一个可编程 熔丝,假如导通便是完结“与”逻辑。后边的乘积项挑选矩阵是一个“或”阵列。两者一同完结组合逻辑。图右侧是一个可编程D触发器,它的时钟,清零输入都可 以编程挑选,能够运用专用的大局清零和大局时钟,也能够运用内部逻辑(乘积项阵列)发生的时钟和清零。假如不需要触发器,也能够将此触发器旁路,信号直接 输给PIA或输出到I/O脚。

二、乘积项结构PLD的逻辑完结原理

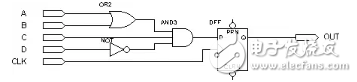

下面咱们以一个简略的电路为例,详细阐明PLD是怎么使用以上结构完结逻辑的,电路如下图:

图3

假定组合逻辑的输出(AND3的输出)为f,则f=(A+B)*C*(!D)=A*C*!D + B*C*!D ( 咱们以!D表明D的“非”)

PLD将以下面的方法来完结组合逻辑f:

图4

A,B,C,D由PLD芯片的管脚输入后进入可编程连线阵列 (PIA),在内部会发生A,A反,B,B反,C,C反,D,D反8个输出。图中每一个叉表明相连(可编程熔丝导通),所以得到:f= f1 + f2 = (A*C*!D) +

(B*C*!D) 。这样组合逻辑就完结了。 图3电路中D触发器的完结比较简略,直接使用宏单元中的可编程D触发器来完结。时钟信号CLK由I/O脚输入后进入芯片内部的大局时钟专用通道,直接衔接 到可编程触发器的时钟端。可编程触发器的输出与I/O脚相连,把成果输出到芯片管脚。这样PLD就完结了图3所示电路的功用。(以上这些过程都是由软件自 动完结的,不需要人为干涉)

图3的电路是一个很简略的比如,只需要一个宏单元就能够完结。但关于一个杂乱的电路,一个宏单元是不能完结的,这时就需要经过并联扩展项和同享扩展项将多个宏单元相连,宏单元的输出也能够衔接到可编程连线阵列,再做为另一个宏单元的输入。这样PLD就能够完结更杂乱逻辑。

这种根据乘积项的PLD根本都是由EEPROM和Flash工艺制作的,一上电就能够作业,无需其他芯片合作。