I2C(Inter Integrated Circuit)双向二线制串行总线,是由飞利浦公司拟定的。I2C总线是一个多主机的总线,运用串行数据线(SDA)和串行时钟线(SCL)在总线上传递信息。每个器材都有一个仅有的辨认地址,并且都能够作为一个发送器或接纳器。当衔接在I2C总线上的多个主机器材一同传输数据时,经过裁定来防止抵触。SDA和SCL都是双向线路,经过一个电流源或上拉电阻衔接到电源。器材输出级有必要是漏极开路或集电极开路,当总线空闲时,两条线路处于高电平,履行线与的功用。

Actel公司免费供给I2C IP核——Core I2C。Core I2C是根据APB总线方式的,它的长处是能够衔接到Core 8051或者是Cortex M1处理器上,便利用户进行SoC规划,本文将首要介绍Core I2C的原理与运用。

1. Core I2C介绍

(1)I2C协议简介

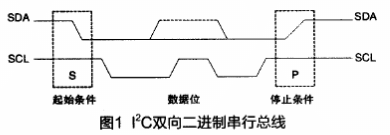

I2C总线协议界说如下:只需在总线处于“非忙”状况时,才干开端数据传输。在数据传输期间,只需时钟线为高电平,数据线都有必要保持稳定,不然数据线上的任何改变都被当作“发动”或“中止”信号。图1所示为总线状况的界说。

I2C总线的作业方式为:当SCL为高电平时,假如检测到SDA的下降沿,则发动数据的传输;在数据传输时,只需SCL为高电平时,SDA数据有必要保持稳定,SDA数据能够在SCL的低电平时发生改变;当SCL为高电平时,假如检测到SDA的上升沿,则中止数据的传输。

(2)Core I2C内部结构

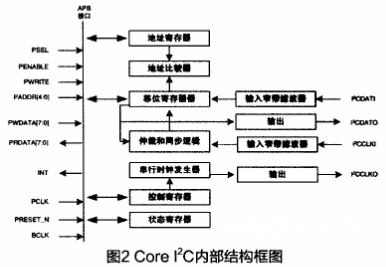

Core I2C的内部结构框图如图2所示。它首要由串行时钟发生器、地址寄存器、操控寄存器、状况寄存器和APB总线接口等组成的。

● 串行时钟发生器模块:供给SCL时钟脉冲。

● 地址寄存器模块:包括了内核编程的地址信息。

● 操控寄存器模块:操控串行传输的发动、重启、中止、位速率、地址辨认和应对等功用。

● 状况寄存器模块:包括了Core I2C内部寄存器作业的状况信息。

● APB总线接口:供给了I2C和APB总线通讯的接口。

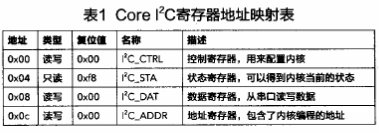

(3)Core I2C内部寄存器

Core I2C的寄存器的地址映射如表 1所示。

● 操控寄存器——I2C_CTRL

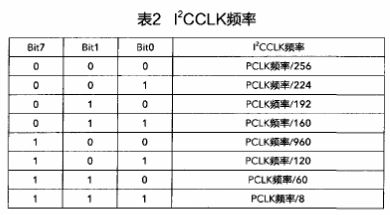

Bit7:串行时钟位2,和第0位、第1位一同决议分频系数。

Bit6:I2C使能位,1表明I2C被使能,不然被制止。

Bit5:开始标志位,1表明开始标志位有用,总线在空闲时将会发生一个开始状况位。

Bit4:中止标志位,1表明中止标志位有用,总线将会发生一个中止状况位。

Bit3:串行中止标志位,在状况寄存器的值被更新今后,这位有必要被清零。

Bit2:主/从机设置位,1表明作业在从机形式,0表明作业在主机形式。

Bit1:串行时钟位1,和第7位、第0位一同决议分频系数。

Bit0:串行时钟位0,和第7位、第一位一同决议分频系数。

Core I2C时钟频率的界说如表 2所示。

● 状况寄存器——I2C_STA

状况寄存器取出一切内部状况位并将它们压缩成一个5位的代码,该代码与每个I2C总线状况位一一对应,5位代码可用于发生向量地址,以便快速处理不同的服务程序,每个服务程序处理一个特定的总线状况。假如I2C模块的一切形式都被运用,则有26种或许的总线状况。

● 数据寄存器——I2C_DAT

数据寄存器包括要发送或刚接纳的数据,当它没有处理字节的移位时,APB操控器能够对其进行读写。

● 地址寄存器——I2C_ADDR

Bit7~Bit1:本身从机地址。

Bit0:通用调用位,该位设置为1,通用调用地址有用,不然无效。

(4)Core I2C的根本操作

Core I2C能够装备成主机或从机,总线时钟速率可调整,最高可支撑400kb/s的总线传输速率。运用I2C总线时,在总线上要衔接两个上拉电阻,阻值为1~10k欧姆。

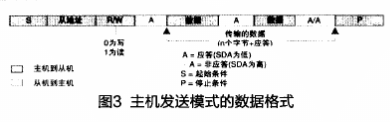

● 主机发送形式

主机发送形式的数据发送格局如图 3所示。先发送开始条件,然后发送从机地址和写方向位,这时从时机发生一个应对,主机在接纳到应对位后,顺次发送n个数据,每个数据发送后,从机都会发生一个应对位,发送完n个数据后,主机发送中止位。

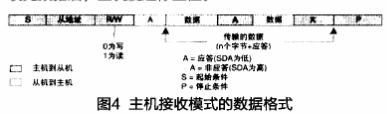

● 主机接纳形式

主机接纳形式的数据接纳格局如图4所示。主机先发送开始条件,然后发送从机地址和读方向位,这时从时机发生一个应对,主机在接纳到应对位后,顺次读出n个数据,主机在接纳到每个数据后,都会发生一个应对位,接纳完数据后,主机发送中止位。

(5)运用场合

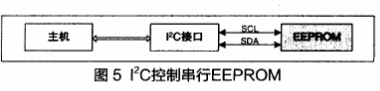

I2C协议首要运用于对串行设备的操控,如各种串行的存储器等。图5所示为运用I2C接口操控EEPROM。

2.小结

本文首要介绍了Actel FPGA的Core I2C IP核,除了Core I2C,Actel公司还供给了UART、SPI、PWM、Timer等IP核,请重视周建功公司的网站取得更多的信息。咱们有着一个挨近30人的FPGA团队供给强有力的售后服务,处理用户在产品运用和研制过程中遇到的困难。若有更多的需求能够与咱们联络,咱们将会诚挚为您服务,并能重视下期的FPGA专题技能讲座。