ASIC的杂乱性不断进步,一起工艺在不断地改善,如安在较短的时刻内开发一个安稳的可重用的ASIC芯片的规划,而且一次性流片成功,这需求一个老练的ASIC的规划办法和开发流程。本文结合NCverilog,DesignCompile,Astro等ASIC规划所用到的EDA软件,从工艺独立性、体系的安稳性、杂乱性的视点比照各种ASIC的规划办法,介绍了在编码规划、归纳规划、静态时序剖析和时序仿真等阶段常常忽视的问题以及避免的办法,然后使得整个规划具有可控性。

1根本的ASIC规划流程

ASIC规划流程能够粗分为前端规划和后端规划,假如需求更细的区分,能够分红如下几个进程:

1.包含体系结构剖析规划、RTL编码以及功用验证;

2.逻辑归纳、PreLayoutSTA以及办法验证(RTL代码与逻辑归纳生成的Netlist之间);

3.Floorplan、Placement、ClockTree刺进以及大局布线(GlobalRouTIng)

4.办法验证(逻辑归纳的Netlist与带有CT信息的Netlist之间)、STA;

5.DetailedRouTIng,DRC;

6.PostlayoutSTA,带有反标推迟信息的门级仿真;

7.Tape-Out

当然,这仍是一个比较粗的流程,其间每个进程还能够分得更细,一般所说的前端规划首要包含上述流程中的1,2,4,6这几个部分。一起,这个流程是一个迭代的进程。关于一些一般的问题以及其间的一些办法,现已有许多的文献中说到,本文将不再赘述,因而本文着力于评论在规划各个阶段中一些简略被忽视的或许或许带来潜在危险的当地。

2结构剖析规划、RTL编码

这一阶段在整个ASIC规划中占十分重要的位置,结构剖析规划阶段首要是从产品的功用界说动身,对产品选用的工艺、功耗、面积、功用以及价值进行开始的评价,然后拟定相应的规划规划,关于规划很大的ASIC规划,在这一阶段预算芯片的功耗面积十分困难。

在这里引进一个ASIC规划中很重要的概念:区分(ParTITIoning),在不同的规划阶段这个概念都将说到。首要,有必要在芯片的Top-1级进行功用区分,Top-1级一般能够分为4个大的功用模块,IOPads、鸿沟扫描逻辑、中心功用逻辑,以及PLL时钟模块,然后再对中心功用逻辑根据功用进一步细化。中心功用部分将是RTL编码规划的要点部分,下面就这一部分打开阐明。

2.1杰出的编码风格

编码风格对芯片的正确性、可读性、可维护性以及归纳后芯片的功用、面积都有很大的影响。天然,关于编码中遇到的一切问题逐个论述不是一篇论文所能做到的,下面只对一些常常遇到的或许发生过错的当地进行要点阐明。

不管从可重用规划的视点仍是代码仿真行为与实践芯片的行为一致性的视点来说,选用工艺独立的规划是必要的,一些工程师在编码时或许用到一些推迟单元或许推迟线,来生成一个脉冲来操作,因为推迟单元对温度、电压以及制作工艺灵敏,这些要素的改动也会改动生成的脉冲的宽度,因而,或许在仿真的时分没有问题,或许在某些操作条件下没有问题,而实践芯片作业时或许作业条件改动时芯片就没有依照规划方针作业了。

在RTL级编码时应该尽量避免选用例化标准单元门的办法编码,这不只下降代码的可读性,当选用新的单元库或许新的工艺时,这些代码就需求重复的修正,归纳东西也不会对这些代码进行逻辑优化。

其他问题如:因为没有对一切的条件分支赋值引起潜在的Latch问题、always块中的灵敏列表问题,以及堵塞赋值与非堵塞赋值的挑选问题许多文献中都说到,就不再赘述。下面说到一个简略被忽视的问题,在界说时序块时,有些信号是需求复位的,有些不需求复位,假如编码时把它们写在一个always块中,归纳出来的电路就不是咱们想象的。关于那些不需求复位的信号,归纳后或许把复位信号连到对应的触发器使能端,这样导致RTL代码和Netlist的行为不一致,而这类问题在办法验证时也无法发现,需求经过许多的门级仿真才或许发现。

ASIC规划应该尽量避免选用Latch作为时序单元,Latch规划潜在的问题,如:假如使能输入端有Glitch,就会导致锁存噪声数据。或许你能够确保数据安稳时刻能够包住使能信号,可你很难确保在使能封闭的瞬间D输入端没有Glitch,尤其在接纳总线数据的时分。一起,Latch规划还带来STA和DFT的困难,而选用触发器的规划,经过Setup/Hold时刻的查看报出这些问题。因而,尽管Latch规划有面积、低功耗等方面的优势,因为这些潜在的危险使得规划变得不行控,因而不引荐运用。

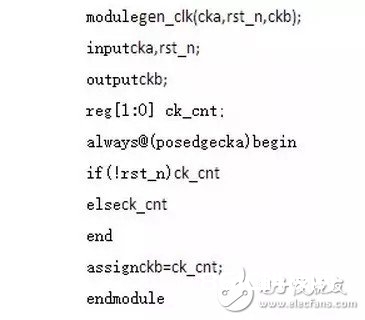

尽量避免把时钟当作信号运用,在RTL验证时不会呈现什么问题,可是,假如在后端规划的时分疏忽了对这些点的时钟skew操控,就会发生意想不到的成果。例如:

例1:

这个代码在RTL级仿真时是不会有任何问题的,其间潜在的问题留下后边评论。

2.2同步规划和跨时钟域数据传输

尽管异步体系有许多优势,如低功耗,也没有同步体系中让工程师头疼的时钟散布以及skew问题,可是其杂乱的各种握手协议,以及异步电路在测验上的困难,使得同步体系仍是数字电路规划的首选。同步规划的一个特色便是一切的时序单元都是对一致的时钟边缘灵敏。要使整个芯片只选用一个时钟并不实际,因而,异步时钟域之间的数据传输以及其间的一些问题将是本节评论的要点。

一般,为了能够更好的归纳和STA,需求对规划进行区分,一般的原则是将异步时钟域之间有数据交换的部分独立出来独自处理,其他的模块都在单一的同步时钟域中作业。关于这些模块如安在归纳进程中特别处理鄙人面的章节中评论,本节首要评论在代码规划中需求考虑的问题。

异步时钟之间的亚稳态(Metastability)问题,亚稳态首要是因为被采样数据的改变十分接近采样时钟的边缘引起的,这样接纳(采样)触发器的输出便是亚稳态,并在传输进程中发散而引发逻辑过错,也便是一般所说的同步失利。在同步时钟域中的这种问题是Hold问题,能够经过EDA东西或刺进buffer消除,因为EDA东西能够检测到这种问题。那么在异步接纳规划中经过两级Flipflop来消除这种或许呈现的亚稳态。现在也有东西检测代码中或许呈现的亚稳态问题。多位接纳操控信号之间的skew引起的问题如图1,假如其间一位如C2推迟大于C1,Ck采样的数据就变成了C2=1,C1=0,假如依照无skew传输的波形是C2’的姿态,应该是00才对。而skew是不行避免的,或许是因为C2C1信号的Launch时钟自身的skew引起,也或许是传输推迟引起。关于简略的状况,咱们能够经过简化逻辑,尽量让操控信号是1位宽。而这样的问题相同呈现在多位宽的数据接纳状况。这时一般引荐运用异步FIFO接纳,或许经过握手协议接纳。有的体系规划数据交换协议约好,异步接纳进程中,当某个事情发生后(如图1中采样到V信号为1后)的1个Cycle后(也能够约好多个Cycle)数据肯定是正确的;也能够消除这种skew问题,可是,这种完结需求后端规划时确保这些相关信号的skew不会超越约好的周期,一起发送方的数据也要坚持满意的周期数。如图1中C2”信号,假如skew2>Period(一个CKCycle),则收到V信号一个Cycle后采样数据仍是过错的。

2.3复位战略

复位信号中最首要的问题是Removal,也便是要确保一切的触发器有必要在同一节拍内脱离Reset状况,别的,Reset信号完结的时刻不能与时钟边缘太接近,以避免触发器进入亚稳态(Metastability)。同步复位和异步复位各有利弊,很难说哪种更有优势。除了在编码风格时讲到的一个问题,在这里再对两种战略中或许呈现的问题进行剖析阐明。

同步复位有一个长处便是复位的时刻发生在时钟的边缘,这样能够避免复位信号的Glitch。假如是内部出产的Reset信号,就有必要确保Reset脉冲有满意的宽,至少2个Cycles,能够让时钟采样到。一起,这也是它的缺陷,因为它需求一个活动的时钟,在加电时无法对一些电路发生复位。别的,归纳或许把同步复位的逻辑移到触发器的D输入端,作为一般的信号处理,因为Reset信号一般有传输负载和推迟,这样处理睬导致DataPath上较长的推迟。

异步复位的最大长处便是不需求活动的时钟,关于一些需求加电复位的电路,如总线,是很必要的;一起,不像同步复位那样,复位信号会被用作D端的输入逻辑,使得整个DataPath十分洁净。假如异步复位有Glitch或许使芯片进入复位状况,这时能够经过两级DFF接纳Reset,再经过tree给复位触发器运用,这样能够消除输入引起的Glitch,假如规划中有多个时钟域,能够对每个时钟分配两个DFF接纳Reset信号。

2.4门控时钟

GatedClock首要的长处在于能够下降功耗面积,也能够简化逻辑然后进步频率。在编码时需求考虑无Glitch的门控信号规划。一起,在DFT规划时,因为触发器的时钟是前一级逻辑的输出(其他派生时钟也有相同的问题),为了测验这类触发器,需求为时钟添加一级Mux,在正常作业形式下,选用派生时钟,在扫描测验时选用正常的时钟。门控时钟的首要问题呈现在归纳、CTS刺进以及STA剖析的时分,在后边将进行特别的剖析评论。

2.5总线完结

在这里只评论总线完结的办法,不触及总线的协议。在规划总线时将面临着两种根本办法的挑选,是选用三态总线仍是选用多路挑选结构的总线。在全定制规划时,规划者好像更喜爱选用三态,挂在总线上的各个部件能够散布在芯片的各个部分。一起,因为能够削减连线的数量,它有必要确保在任何时分,不发生总线抵触,假如多个驱动总线或许导致严峻的过错,需求经过一些办法消除这种危险,比方三态的使能经过解码器发生Onehot的编码,避免多驱动引起的逻辑过错和对芯片的危害;一起,三态总线需求连到上拉电阻上,以避免在一段时刻内不驱动总线发生总线数据不确定,而DC等归纳并不支撑。别的,三态总线的%&&&&&%负载也是一个不行忽视的问题,对功用和面积形成晦气的影响,其负载首要来自总线衔接的多个电路单元,总线布局自身带来必定的负载;最终,三态总线给DFT规划也带来困难。根据这些理由,在非定制AS%&&&&&%规划时,咱们真实不必要挑选三态总线的办法。相比之下,选用多路挑选器的问题是较多连线带来的布线拥塞问题,挑选器的推迟问题根本上不是什么问题,深亚微米规划中,门的推迟不同现已变少,一起多层金属也带来了满意的布线资源。

3逻辑归纳以及后端规划相关问题

3.1编码风格查看

DC对编码风格的查看供给杰出的支撑,在进行逻辑归纳之前最好先剖析一下DC的log文件,看是否有上述的或其他的一些编码风格问题。经过set_dont_use指令能够制止运用一些工艺相关的单元,all_registers带参数也能够陈述出规划中所用到的Latch。下面首要评论前面说到的一些状况在归纳以及后端完结时的特别处理。一起,还有许多EDA东西供给编码风格进行查看。

3.2异步时钟域

在编码规划中咱们经过区分,将异步时钟域接纳模块别离成独立的模块,其他模块都选用独自的时钟,归纳束缚相对简略。关于那些带有异步时钟域的模块,假如不进行束缚,DC总是企图去满意采样时钟的setup/hold时刻,事实上,规划者并不关怀异步时钟域之间的这些问题,而其Metastability问题在编码阶段现已处理。一般,能够设置异步时钟域之间的Path为false_path。如:

set_false_path-from[get_clocksCLKB]-to[get_clocksCLKA]

假如异步接口数据的操控依照最终一种办法

(也便是在约好的节拍内读取数据),也就需求发送方的数据skew操控在必定范围内。因为没有对这些途径进行束缚(尽管能够设置这些path的Maxdelay,可是这种束缚关于skew的操控并不能取得好的作用),东西无法对这些途径进行主动优化。因而最好选用手艺布局的办法,让这些skew在一个可控的范围内,在STA阶段,也需求对这些skew进行独自的剖析。

3.3特别时钟信号处理

门控时钟像一切的内部时钟相同,时钟的skew或许引起一些坚持时刻问题,默许条件下,时钟树归纳东西并不把逻辑门相连的时钟信号连到时钟树上,非门控的触发器上的时钟是连在时钟树上,这个时钟推迟是相当可观的,为了操控门控时钟与非门控时钟的skew,一般从时钟树叶子节点的上一级引出时钟信号作为操控门的时钟输入。在STA阶段需求对门控时钟的Setup/Hold时刻进行特别剖析,以及Glitch查看。然后,咱们再回忆一下例1的代码中的状况,能够用图2的示意图表明。