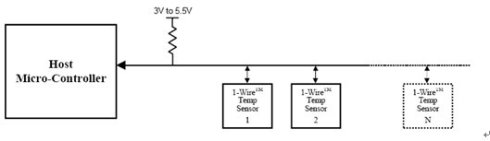

1-WIRE 总线是一种异步半双工串行传输,只需要一条信号线(OWIO)来传输数据,典型的1-WIRE 总线传输架构如图1。1-WIRE 总线传输中,信号线除了作为传输数据的用处之外,也一起是一切衔接此1-WIRE 总线设备电源的来历。信号线会衔接一个4.7K欧姆的Pull-High电阻,电阻再接到电源(3V到5.5V)。1-WIRE 总线传输运用的速度有规范速度与高速两种。每个1-WIRE 总线有独立的64位辨识码以供设备辨识用,因而最多能够衔接1.8*1019个设备,几乎是无限制。1-WIRE常见的应用是在EEPROM上与一些传感器界面上。

1-WIRE的速度有规范:1MHz(1us),高速:5MHz(0.2us).

1-WIRE有四种数据包:

1.Reset:每个通讯周期都是由Reset信号开端。Master会先发送Reset Pulse让一切在1-WIRE上的Slave设备进入区分状况,当一个Slave或很多个Slave接纳到Reset Pulse信号之后,Slave会回传一个Presence Pulse信号,用来表明接纳到。

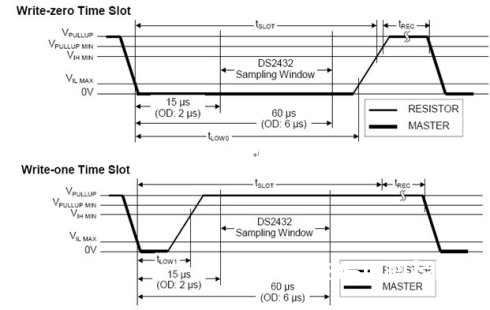

2.Write 0:发送一个“0”bit给Slave(Write 0 time slot)。

3.Write 1:发送一个“1”bit给Slave(Write 1 time slot)。

4.Read Da

2.Write 0:发送一个“0”bit给Slave(Write 0 time slot)。

3.Write 1:发送一个“1”bit给Slave(Write 1 time slot)。

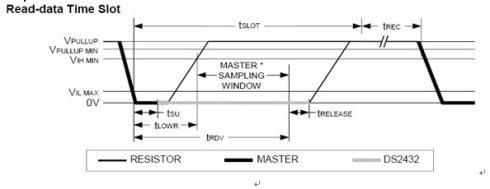

4.Read Da

Reset:一开端Master要跟Slave做任何通讯时,Master会先传送一个低准位的Reset Pulse(TX)of(规范速度:480us;高速:48us)的一段时间。接着Master会开释出总线线并进入接纳方式(RX),1-WIRE Bus会透过上拉电阻将准位拉回High状况。然后Master在Da

Write Da

Read Da