今日我们聊聊xilinx7系列FPGA装备的相关内容。总所周知FPGA上电后,其作业的逻辑代码需求从外部写入FPGA,FPGA掉电后其逻辑代码就丢掉,因而FPGA能够被无限次的装备不同的逻辑代码,但FPGA需求装备外部的非易失存储器来存储其逻辑代码或许经过单片机、DSP或许其它操控器来完成FPGA上电后的逻辑代码载入。

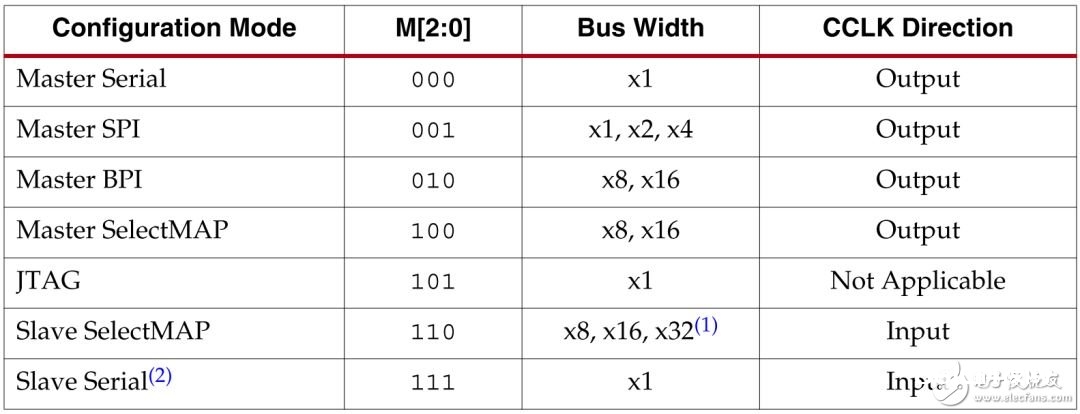

xilinx7系列FPGA规划有专门的逻辑代码装备管脚,经过不同的管脚接法,其逻辑代码装备形式能够分为以下7种:

1,主串装备形式

2,从串装备形式

3,主并装备形式

4,从并装备形式

5,JTAG装备形式

6,主SPI装备形式

7,主BPI装备形式

所谓的主,即装备时钟CCLK由FPGA供给;所谓从,即装备时钟CCLK由外部操控器供给。下面这张表代表了这7种装备形式,其形式的切换由FPGA的3个装备管脚M0、M1、M2操控:

下面我们别离说说xilinx7系列FPGA的这7种装备形式:

1,主串装备形式

在该形式下,FPGA向外部的非易失性串行数据存储器或许操控器宣布CCLK时钟信号,装备数据会以串行方法载入FPGA,在前几代的FPGA中,存储器一般挑选xilinx 官方的XCF串行系列存储器,并给出了相应的规划原理图,但在7系列FPGA中,这种方法形似被抛弃了,其官方的装备文档里并无主串装备形式的相关具体描绘。

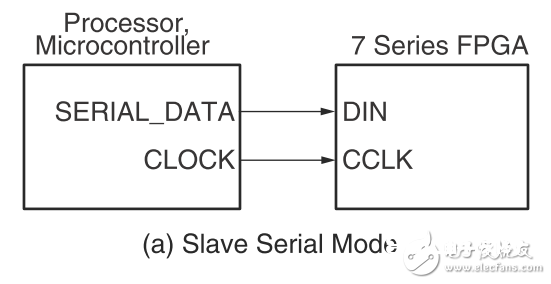

2,从串装备形式

如下图1所示,在该形式下,由外部的处理器供给CCLK时钟和串行数据,用户完成起来相对杂乱,不行大众化,这儿就不做介绍了。

图1

3,主并装备形式

相同的,该形式在其官方文档并无具体规划描绘,无从参阅。

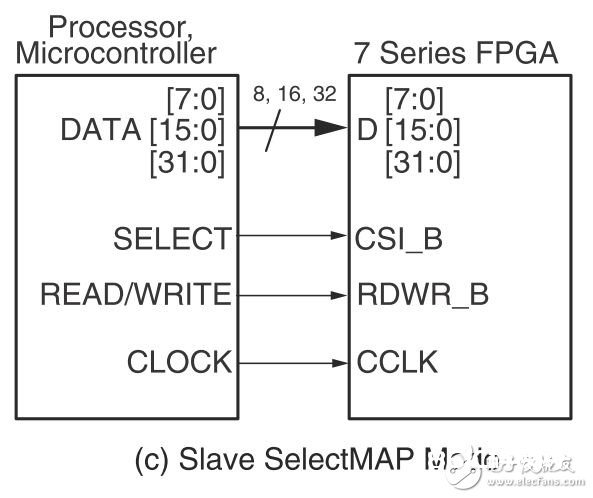

4,从并装备形式

如下图2所示,在该形式下,外部处理器供给装备时钟和并行的装备数据,该形式相对于串行方法来说,装备的速度快,但规划略微杂乱。下图3为官方给出的具体装备原理图,该形式相同运用较少。

图2

图3

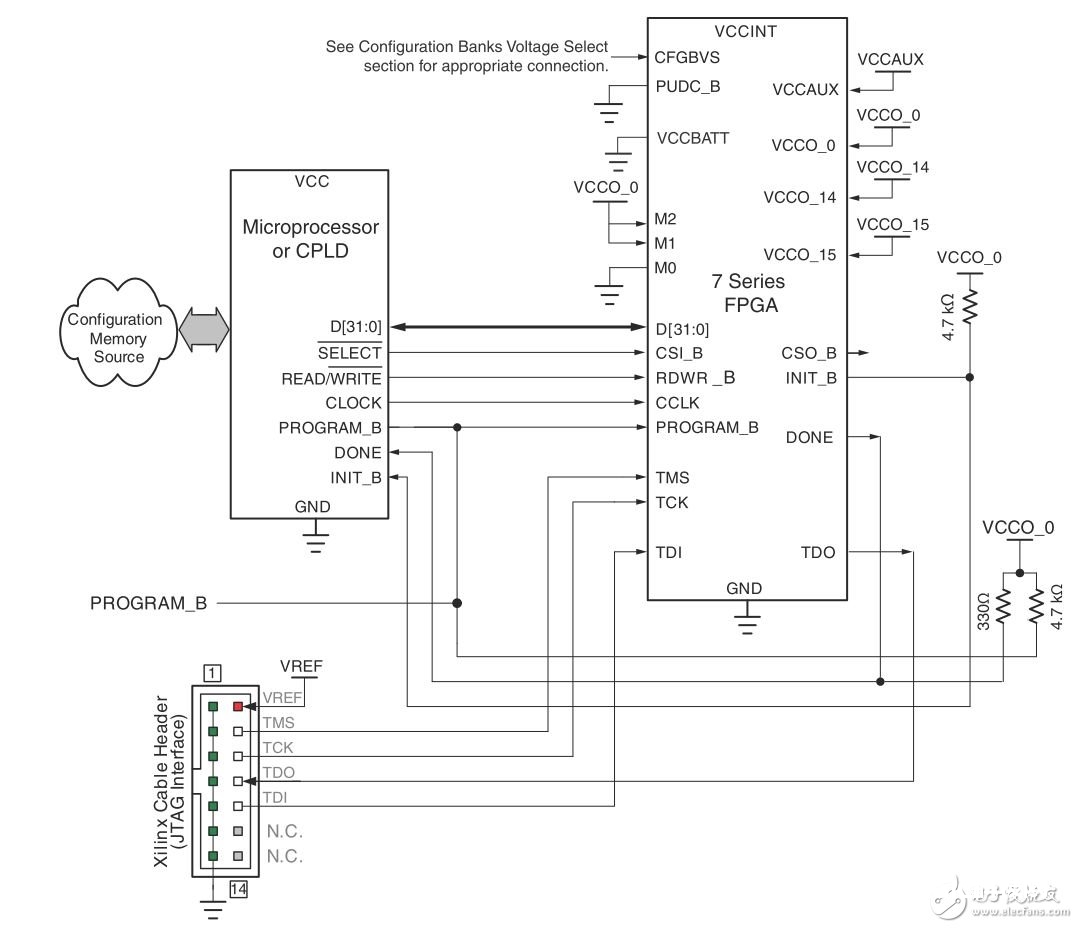

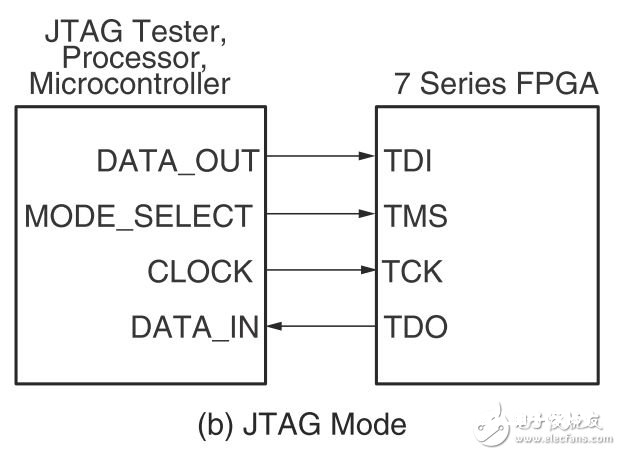

5,JTAG装备形式

如下图4所示,该形式归于工程调试形式,我们在规划FPGA时必带这种形式。该形式只能在线装备和调试FPGA,无法存储逻辑代码。最简略的操作方法是运用xilinx官方供给的专用JTAG调试下载器,但一同也答使用户经过外部处理器自行规划JTAG的数据协议来装备FPGA逻辑代码。再次着重,该形式仅仅一个调试形式。

图4

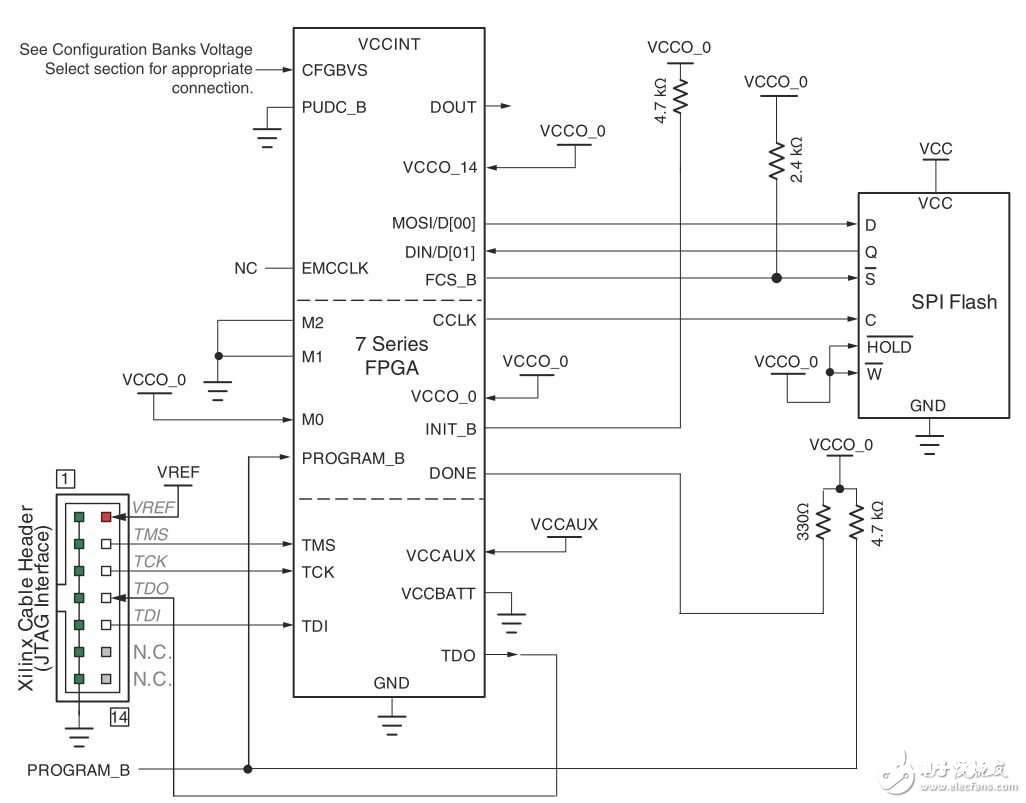

6,主SPI装备形式

这种形式应该算是我们运用最广泛的装备形式了,经过外挂一个SPI存储器即可。一般该形式和JTAG装备形式一同规划。JTAG形式在线调试好逻辑代码后,将该逻辑代码存储在SPI存储器中,今后FPGA上电后就会主动载入存储器中的逻辑代码。下图5为官方给出的具体装备原理图。

图5

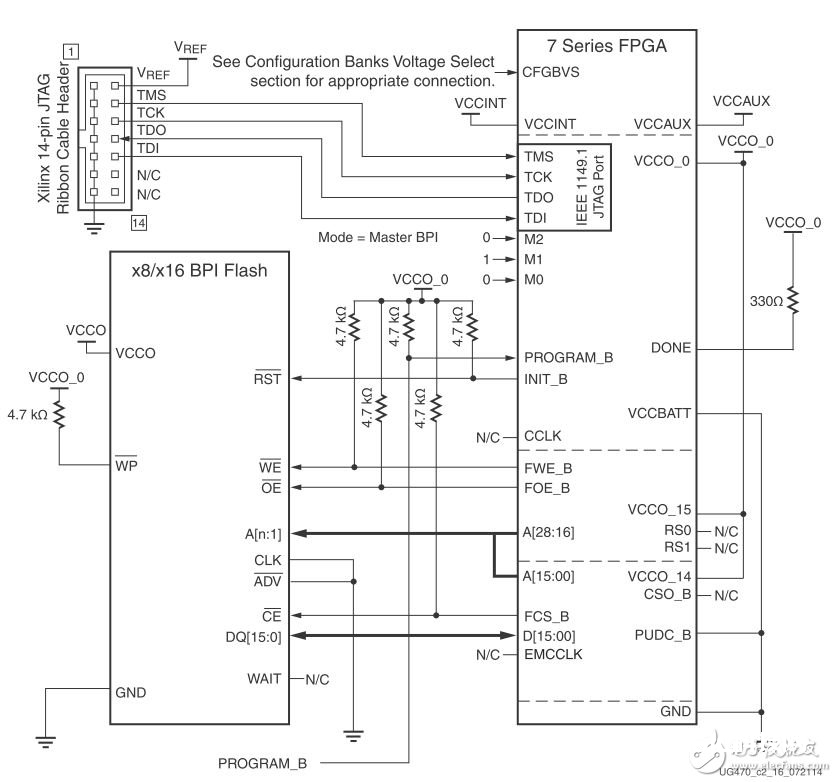

7,主BPI装备形式

该形式的时钟CCLK相同由FPGA供给,并行的数据比SPI形式的串行数据装备速度要快,但规划略微杂乱一点。图6为官方给出的具体装备原理图。

图6

我们在规划FPGA时,基本上都是选用JTAG装备形式+主SPI装备形式(图5)或许JTAG装备形式+主BPI装备形式(图6)。前者用于一般的使用,后者用于对FPGA上电后逻辑代码载入速度有较高要求的使用。