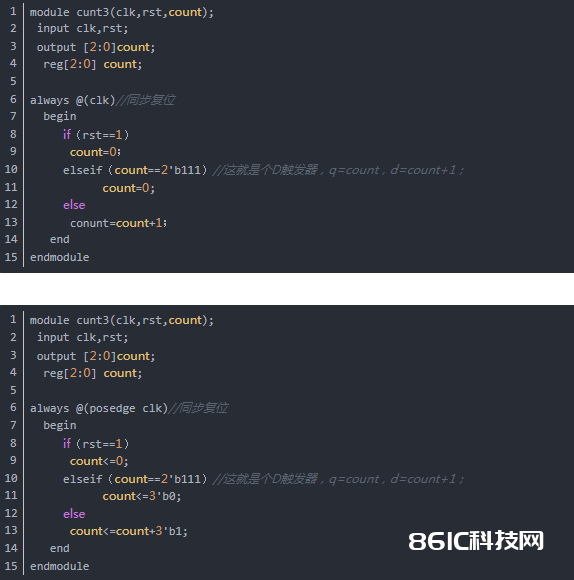

剖析:首要,咱们能够看到有哪些信号。复位rst 、计数器3位的、时钟信号。(用到2路挑选器。复位和不复位)

其次,怎样完成,一个时钟过来,记一次数便是加一次,保存(用到D触发器),满之后为0;

最终,依照以上剖析,进行编写程序。

上面是修改正的,由于时序逻辑电路,因而。用非堵塞赋值。q是3位,因而加上3‘b1,

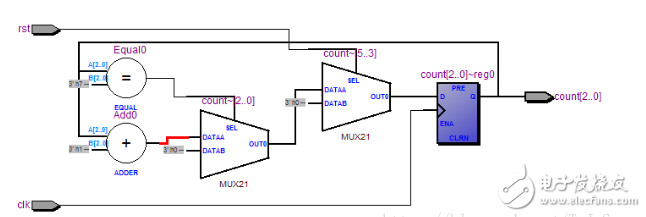

输入代码,挑选Processing 》 start 》 Analysis & Elaboration

Tools 》 Netlist viewer 》 RTL viewer

通过以上过程,则得到以下电路。

从图中能够看出有两个2选1挑选器和一个D触发器调集(由于存储的是3位数据,需求3个D触发器),别的还有一个加法器和一个比较器。

因而,能够标明从程序里就能够看要用那些元件,从而能更好的了解程序的用处。