前一阵出差,然后又吹空调受凉歇息了一阵子,耽误了不少时刻。现在缓过劲来了,能够持续写作了。出差途中数小时路上无聊,就随手打印了XAPP463.pdf,即《Using Block RAM in Spartan-3 GeneraTIon FPGAs》,深感FPGA装备的灵敏与杂乱性。在此把阅览此运用陈述的心得共享一下,欢迎咱们沟通。

在赛灵思Spartan-3、3E等系列的FPGA中,其逻辑单元CLB中一般含有不同数量的单端口RAM(SRAM)或许双端口RAM(DRAM),这儿的“单”或许“双”是由咱们开发人员界说的。一般情况下这种RAM散布于(distributed)FPGA的阵列结构中,所以被称为“散布式RAM”,以便差异于FPGA中的块RAM(block RAM);它们的具体差异咱们能够看Spartan3系列的用户手册(UG331.pdf, Spartan-3 GeneraTIon FPGA User Guide),其间对一切模块及其功用都有最全面的解说,包含各种杂乱的时序剖析。散布式RAM在部分规划中能够方便地完成小的数据缓存区、FIFO或许寄存器组等等。接下来咱们评论散布式RAM的特征、功用以及怎么运用Xilinx的东西来调用散布式RAM。

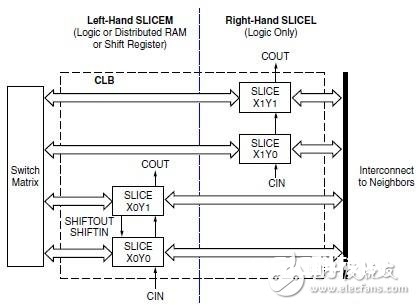

图1 散布式RAM的暗示

声明:本文内容来自网络转载或用户投稿,文章版权归原作者和原出处所有。文中观点,不代表本站立场。若有侵权请联系本站删除(kf@86ic.com)https://www.86ic.net/fangan/dianlu/179486.html