在 DRAM Storage Cell 章节中,介绍了单个 Cell 的结构。在本章节中,将介绍 DRAM 中 Cells 的安排方法。

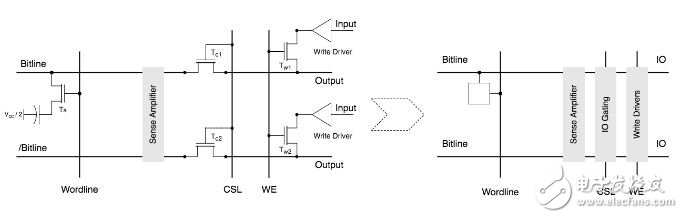

为了更明晰的描绘 Cells 的安排方法,咱们先对上一章节中的 DRAM Storage Cell 进行笼统,终究得到新的结构图,如下:

1. Memory Array

DRAM 在规划上,将一切的 Cells 以特定的方法组成一个 Memory Array。本末节将介绍 DRAM 中是如何将 Cells 以 特定方法的 Memory Array 安排起来的。

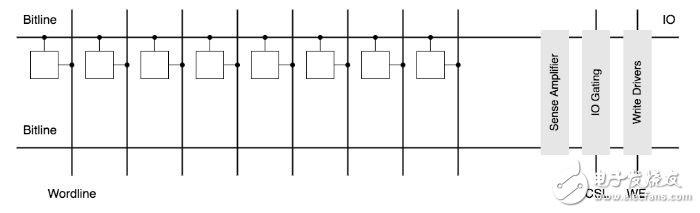

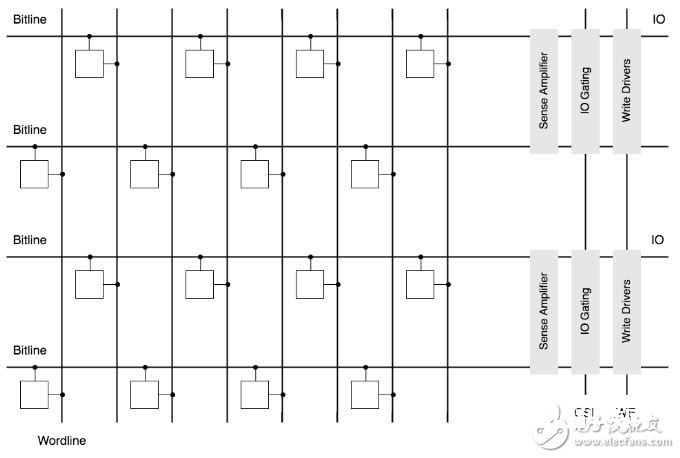

首要,咱们在不考虑方法的情况下,最简略的安排方法,便是在一个 Bitline 上,挂接更多的 Cells,如下图所示:

但是,在实践制作进程中,咱们并不会无约束的在 Bitline 上挂接 Cells。因为 Bitline 挂接越多的 Cells,Bitline 的长度就会越长,也就意味着 Bitline 的电容值会更大,这会导致 Bitline 的信号边缘速率下降(电平从高变低或许从低变高的速率),终究导致功能的下降。为此,咱们需求约束一条 Bitline 上挂接的 Cells 的总数,将更多的 Cells 挂接到其他的 Bitline 上去。

从 Cell 的结构图中,咱们能够发现,在一个 Cell 的结构中,有两条 Bitline,它们在功能上是彻底等价的,因而,咱们能够把 Cells 分摊到不同的 Bitline 上,以减小 Bitline 的长度。然后,Cells 的安排方法就变成了如下的方法:

当两条 Bitline 都挂接了足够多的 Cells 后,假如还需求继续拓宽,那么就只能添加 Bitline 了,添加后的结构图如下:

从图中咱们能够看到,添加 Bitline 后,Sense Amplifier、Read Latch 和 Write Driver 的数量也相应的添加了,这意味着本钱、功耗、芯片体积都会跟着添加。因为这个原因,在实践的规划中,会优先考虑添加 Bitline 上挂接的 Cells 的数量,防止添加 Bitline 的数量,这也意味着,一般情况下 Wordline 的数量会比 Bitline 多许多。

上图中,出现了一个由 16 个 Cells 组成的 Memory Array。其间的操控信号有 8 个 Wordline、2 个 CSL、2 个 WE,一次进行 1 个 Bit 的读写操,也便是能够理解为一个 8 x 2 x 1 的 Memory Array。

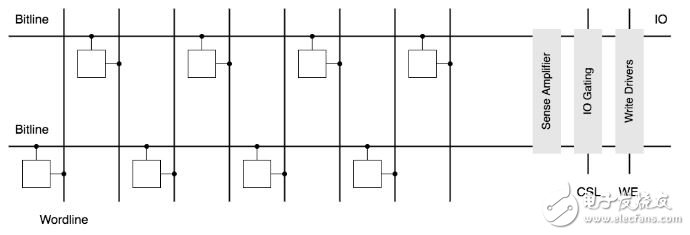

假如把 2 个 CSL 和 2 个 WE 合并成 1 个 CSL 和 1 个 WE,如下图所示。此刻,这个 Memory Array 就有 8 Wordline、1 个 CSL、1 个 WE,一次能够进行 2 个 Bit 的读写操作,也便是成为了 8 x 1 x 2 的 Memory Array。

依照上述的进程,不断的添加 Cells 的数量,终究能够得到一个 m x n x w 的 Memory Array,如下图所示

其间,m 为 Wordline 的数量、n 为 CSL 和 WE 操控信号的数量、w 则为一次能够进行读写操作的 Bits。

在实践的使用中,咱们通常以 Rows x Columns x Data Width 来描绘一个 Memory Array。后续的末节中,将对这几个界说进行介绍。

1.1 Data Width

Memory Array 的 Data Width 是指对该 Array 进行一次读写操作所拜访的 Bit 位数。这个位数与 CSL 和 WE 操控线的安排方法有关。

1.2 Rows

DRAM Memory 中的 Row 与 Wordline 是一一对应的,一个 Row 本质上便是一切接在同一根 Wordline 上的 Cells,如下图所示。

DRAM 在进行数据读写时,选中某一 Row,实质上便是操控该 Row 所对应的 Wordline,翻开 Cells,并将 Cells 上的数据缓存到 Sense Amplifiers 上。

Row Size

一个 Row 的 Size 即为一个 Row 上面的 Cells 的数量。其间一个 Cell 存储 1 个 Bit 的信息,也便是说,Row Size 即为一个 Row 所存储的 Bit 位数。

1.3 Columns

Column 是 Memory Array 中可寻址的最小单元。一个 Row 中有 n 个 Column,其间 n = Row Size / Data Width。下图是 Row Size 为 32,Data Width 为 8 时,Column 的示例。

Column Size

一个 Column 的 Size 即为该 Column 上所包括的 Cells 的数量,与 Data Width 相同。Column Size 和 Data Width 在本质上是相同的,也是与 CSL 和 WE 操控线的安排方法有关(参阅 Memory Array 末节中关于 CSL 的描绘)。

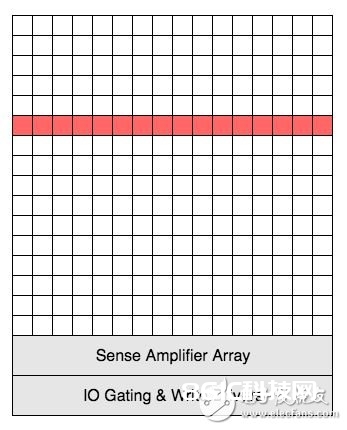

2. Memory Bank

跟着 Bitline 数量的不断添加,Wordline 上面挂接的 Cells 也会越来越多,Wordline 会越来越长,继而也会导致%&&&&&%变大,边缘速率变慢,功能变差。因而,一个 Memory Array 也不能无约束的扩展。

为了在不减损功能的基础上进一步添加容量,DRAM 在规划大将多个 Memory Array 堆叠到一同,如下图所示:

其间的每一个 Memory Array 称为一个 Bank,每一个 Bank 的 Rows、Columns、Data Width 都是相同的。在 DRAM 的数据拜访时,只要一个 Bank 会被激活,进行数据的读写操作。

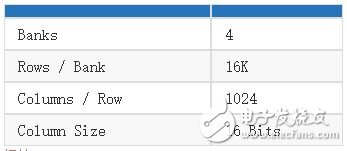

以下是一个 DRAM Memory OrganizaTIon 的比如: