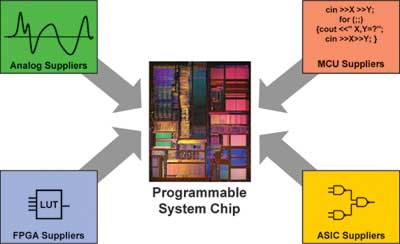

终端运用商场对器材的灵敏性、可装备性和功用的要求愈来愈高,但一同又要求功耗更低、体积更小及本钱更低。假如将模仿、存储器、逻辑和微处理器(MCU)悉数集成于单个芯片上,在灵敏性和集成性方面的压力日益添加,使到模仿器材、MCU和ASIC供货商纷繁转而为其产品参加可装备才干。

除了要为客户供给更多的功用,这些供货商还希望能下降开发本钱。可是,掩模本钱的不断攀升将持续约束ASIC产品的开发,而且也会影响MCU和模仿器材供货商扩展产品品种。为产品添加可编程和可装备的才干,能让半导体供货商只需以更少的掩模组合便可为相同的运用范畴服务,然后缩短开发周期和下降开发本钱。

在现有的四种干流技能(MCU、模仿电路、ASIC和FPGA)中,FPGA的可编程才干可谓占尽优势,但还有必要战胜一些妨碍才干开发成功的计划。FPGA技能的开发需求巨大的软、硬件出资。硬件芯片的要求包括开发高效、灵敏和高功用的可编程架构,并需求广泛的软件东西以支撑规划开发、验证、评测和编程。

|

| 图1 完结可编程体系芯片(PSC)解决计划的办法 |

与FPGA IP不同,AS%&&&&&%库可经过代工办法取得,而商场上有各式各样的MCU内核可供授权运用。这个范畴里有几家做得很成功的公司,其间最著名的是ARM。此外,模仿IP也可从多家供货商购得或自行开发。

三个要害因素

要完结可编程体系芯片有三个要害:首先是工艺技能,其次是体系规划构架,终究是东西支撑。

工艺技能的好坏是在单个单芯片上集成存储器、模仿和可编程逻辑的一个最大要害,现在一般选用标准CMOS工艺。因为需求高门数来完结大型可编程逻辑芯片,许多FPGA供货商均选用最顶级的CMOS技能。可是,CMOS工艺并不适用于嵌入式Flash和模仿集成,因而可编程体系芯片无法选用标准的CMOS工艺。一般,嵌入式Flash和模仿器材的工艺支撑是顶级的CMOS节点背面的多个工艺节点。顶级、高门数器材和以模仿及Flash为根底器材之间的工艺仍存在距离。

许多模仿器材会与外界的传感器或电源接口,外界信号的电压不会都是90nm CMOS工艺技能规则的1.2V电压。优秀的可编程体系芯片工艺将会支撑模仿器材与这些信号的直接衔接。经过支撑较高的电压,先进的Flash工艺便可扩展集成模仿IP的动态电压范В佣锤叩男旁氡群透训哪D庑阅堋N思醯陀筛咚偈致呒谀D釯P中参加的噪声,嵌入式Flash工艺有必要与模仿和数字部分有用地阻隔开来。这个工艺还有必要支撑高功用RAM和逻辑功用。

以Flash为根底的FPGA有必要能处理编程所需的大电压,而且很好地进行阻隔,以及对这些电压加以操控。高电压晶体管供给很大的动态电压规划,以及能与模仿IP的高电压信号直接衔接。此外,三井技能会进步模仿和数字元件之间的阻隔度,有助于减小芯片尺寸。

相关于混合信号AISC的开发或更杂乱的多芯片计划而言,可编程体系芯片的一个要害优势是其产品推出商场的时刻较短。为了充分发挥这一优势,体系规划有必要好好地加以安排,让用户能依据需求在高或低笼统度的水平下进行开发和规划。

可编程体系芯片技能为体系规划人员供给的灵敏功用够由相似于OSI通讯层的多层规划笼统水平显示出来。

这个层次模型供给了灵敏的规划环境,可一同在高和低的笼统水平进行规划。可编程体系芯片仓库有4个层次。0层相似于物理层,包括硬模仿IP和软及/或硬数字IP。第1层操控与0层及0层中各部件之间的通讯,与数据链路层相似。第2层很像OSI的表述层,担任将数据带到一个端点,使到终究体系运用(第3层)能够在其上作业,就像运用层相同。

0层即外设层(物理层)是可装备的功用块,能够选用硬衔接结构,如PLL(锁相环)或模仿输入通道,也能够在软门电路上完结,如UART或PC接口。这些外设能够装备,并支撑标准接口以便当通讯和履行。

第1层骨干(链路层)衔接和操控外设的存取。这应该选用软门电路结构,可延展至任何规划的外设。骨干层是总线和操控逻辑,担任办理外设装备,以保证其运作正常。骨干层还凭借通用的外设接口和低层次状态机,使外设办理能从体系规划中有用地卸除出来。骨干层还能依据外设行为和界说的功用标准,对阈限标识进行置位和清零。可编程体系芯片仓库的灵敏性答应规划人员直接装备外设,而且可按需求跳过骨干层,如这是所需的操控水平的话。

|

| 图2 可编程体系芯片(PSC)技能的层次 |

第2层小型运用隶属程序Applet(表述层)是独立的运用建构模块,运用Flash和模仿外设完结FPGA门电路内指定的功用。小型运用隶属程序经过与骨干通讯对鼓励信号和板级事情做出呼应;即经过骨干存取和操作外设,对鼓励信号做出呼应或建议其他动作。作为可彻底重复运用的IP结构,小型运用隶属程序能轻松导入规划环境及从规划环境中导出。这样,规划人员就可敏捷在其规划中导入多个小型运用隶属程序,然后构建杂乱的规划。

第3层体系运用程序(运用层)是较大的用户运用程序,选用了一个或以上小型运用隶属程序。因为在最高的笼统水平进行规划,而且由可编程体系芯片技能仓库予以支撑,因而整个FPGA体系规划无须任何HDL(硬件描绘言语)代码便可规划出来。该运用程序在FPGA门电路中完结,只需导入和装备多项小型运用隶属程序即可生成。

用户还可选配软MCU内核,以完结根据软件和HDL规划办法的组合。体系的区分十分灵敏,可让MCU置于小型运用隶属程序之上,或在需求时吸收小型运用隶属程序或小型运用隶属程序与骨干。

可编程体系芯片技能仓库供给了十分灵敏的规划环境示例。这种构架运用户能够取得最大的规划灵敏性,从最高水平的“选与点”规划(可完结快速的运用开发)到极低层次的规划(能完结最高的规划操控)以及两者之间的水平。

支撑东西

整合杂乱可编程体系芯片的东西会带来新的杂乱性和需求。在这层面所要求的开发东西特性如下:

高水平的规划才干;

快速生成运用程序的新办法;

软/硬件协同验证;

以总线为根底的通讯;

器材/体系建模及规划区分;

立异的调试功用。

为了支撑这种高水平的集成,开发东西有必要和谐合作。半导体器材和规划环境有必要和谐一致,然后到达事半功倍的产品开发功率。对规划人员来说,虽然添加了混合信号和Flash功用,可编程体系芯片环境下的规划作业应当与数字规划流程环境相同流通简明。

这些新东西有必要能让规划人员在规划中轻松履行和装备外设、在外设之间树立衔接、创立或导入构件模块或参阅规划,以及进行软/硬件验证。这些东西套件还应包括全面的软/硬件调试功用及整套实用程序,以简化根据软处理器内核嵌入式解决计划的开发作业 (如ARM和8051)。

可编程体系芯片东西组有必要为用户供给软/硬件规划中的高度灵敏性,以便进行体系建模。规划工程师和体系工程师能在FPGA逻辑门上自在区分其运用,也可经过选配软处理器内核或透过软、硬件结合的办法在软件中履行。

规划生成东西有必要供给十分灵敏的环境以及多种选项。只需有满意的FPGA逻辑门资源,用户便能在规划环境中导入任何数量的小型运用隶属程序。由图形用户界面支撑,这些小型运用隶属程序能够在规划及不同的外设中完结,只需单击鼠标便可进行一切装备,过程中彻底无须HDL编码。与此一同,该东西链还会创立骨干,衔接所需的外设,以及生成低层处理所需的操控。一切这些都会在后台主动完结,无须用户直接介入。这些以图形用户界面为根底的东西运用简单,而且供给快速的规划开发。这些东西并不排挤传统的HDL编码开发,让习气于这种开发流程的用户也可选用HDL编码来按需求衔接各个门电路,或完结高度定制化的规划。

因为可编程体系芯片技能添加了杂乱性和史无前例的集成度,仿真因而在规划验证中扮演无足轻重的人物。混合信号元件可在数字逻辑中进行行为化模型,并在数字环境中验证。可编程体系芯片东西解决计划有必要供给整套数字化行为仿真模型,对一切集成在芯片上的各种资源给予仿真支撑。这个战略能大幅下降东西本钱,因为它不再需求贵重的模仿建模东西,而能够有用完结体系级仿真的模仿建模东西一般高达10万美元。

由用户或运用生成器创立的RTL应可顺畅地经过逻辑及物理归纳。可编程体系芯片技能供给优异的集成才干,为单芯片规划的验证带来很大应战。因而,有必要选用先进的调试东西在仓库中各个运用笼统层面进行规划验证。例如,用户应可在运用指定的模块中嵌入逻辑分析器,以完结实时传感功用;而且还可将这些分析器与骨干接口,实时地监控外设的活动。此外,还需求额定的调试功用来让用户存取和修订与外设、寄存器列、嵌入式SRAM和Flash内存有关的装备。

因为可编程体系芯片渠道支撑嵌入式处理解决计划,因而也有必要支撑盛行的内核,如8051和ARM7,才干完结最广泛的运用。由Actel和其他供货商供给的东西能帮忙用户用C言语构建运用,且特为可编程体系芯片器材上运转的软MCU而优化。用户可运用其软件调试东西调试程序代码,并在协同仿真的环境下履行指令集仿真。

规划团队十分需求开放式的规划环境。这种规划环境能促进技能生态体系的开展,使客户、用户群、第三方东西开发商和规划公司能够联合一同,构成互动。其间,每一位成员只需专心于自己所长,即可创造出一个高效和低本钱的开发环境。体系规划人员能够从生态体系把握所需的资源。

可编程体系芯片技能和规划开发环境能让用户在高笼统度的层面进行规划,而且简单导入和导出小型运用隶属程序。这些模块化和已界说的小型运用隶属程序更有助于IP的重复运用和同享。客户可开发小型运用隶属程序以支撑其运用,也能够将其混合、匹配和内部同享。第三方东西供货商可针对特定的纵向商场运用开发小型运用隶属程序生成器,又或选用模型将小型运用隶属程序生成器作为东西链的一部分分发出去,然后加速规划开发。此外,体系规划人员还可结合处理器/微操控器生态体系,与多个解决计划供货商一起协作。

总结

因为在有用性、易用性和本钱效益上的固有优势,FPGA供货商更简单开发可编程体系芯片解决计划。规划架构决议了是否能缩短开发周期和下降开发本钱,坚持高度的灵敏性,以满意不同用户群的各种需求。

选用相似于OSI网络仓库的开发环境能够简化开发流程,让传统的数字规划人员按照习气在低层进行规划;至于非传统的FPGA规划人员则可经过导入和装备小型运用隶属程序,在较高层次进行规划。关于了解嵌入式处理器的规划人员来说,能够运用了解的C编码并在软件中进行全盘规划。该模型还供给各种灵敏的结构化手法,充分发挥高集成水平,便当于IP的重复运用和加速规划开发。