EdgeBoard简介

EdgeBoard是百度依据FPGA芯片研制的嵌入式AI解决方案,高功能的加快引擎可供给3.6Tops的强壮算力,完好的嵌入式参阅规划使硬件集成轻松快捷。现在EdgeBoard供给了FPGA软核和核算卡模块两种形状供硬件集成,面向项目布置也供给了抓拍机和核算盒两种根底硬件产品。EdgeBoard深度兼容百度大脑模型资源与东西渠道(EasyDL/AI Studio),极大降低了开发验证、产品集成、科研教育、项目布置门槛,适用于安防监控、工业质检、医疗确诊、农作物成长监控、无人驾驶、无人零售等场景

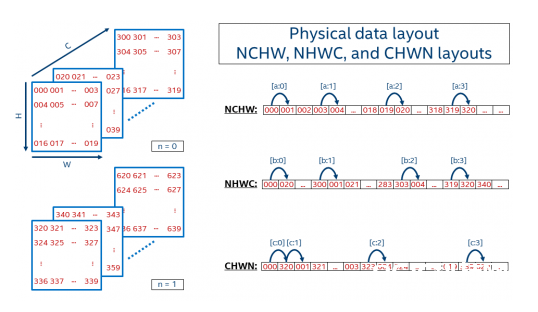

数据格局的逻辑表明与物理表明

深度学习中经常会运用NCHW、NHWC和CHWN数据格局来表明数据,其间N、H、W、C界说如下:

N:一个batch内图片的数量,一次处理的图片数量

H:笔直高度方向的像素个数,图片的高

W:水平宽度方向的像素个数,图片的宽

C:通道数。例如灰度图画为1, 五颜六色RGB图画为3

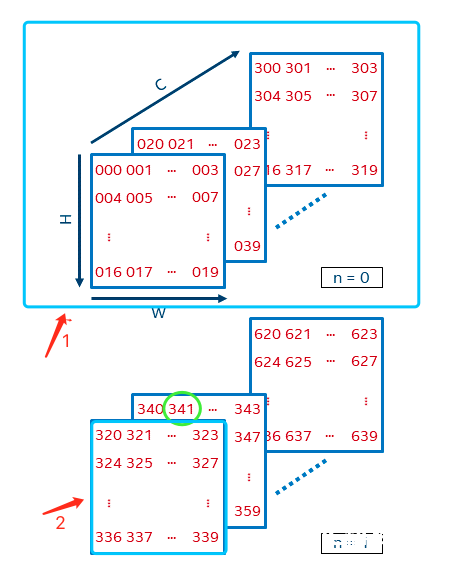

下图表明N=2,C=16,H=5,W=4的数据摆放,其间左图是逻辑表明,右图是物理表明。

以NCHW为例,其逻辑表明如左上图,n=0时,三个坐标别离标识了C、H、W的方向。榜首个元素是000,第二个元素沿着w方向,即001,随后是002, 003;然后沿H方向,即004, 005, 006, 007.。.如此重复到019后;再沿C方向,020,021, 022 。..。.一直到319;再沿N方向,也便是n=1,然后重复W方向,H方向和C方向。

依据以上NCHW的区分,物理地址表明界说如下(如右上图):

[a:0] 表明W方向,在一行内从左到右

[a:1] 表明从H方向,一行一行的从上到下

[a:2] 表明在C方向,从一个通道到别的一个通道

[a:3] 表明从N方向,从n=0 到n=1

终究NCHW数据格局的物理散布(在内存中的一维表明)表明为000 001 002 003 004 。.. 018 019 020 。.. 318 319 320 。.. 。.. 637 638 639。能够了解成把一个通道的一切像素一行一行地摆放起来,然后排下一个通道,即n=0摆放完后再排n=1。

同理NHWC表明是先沿C方向,再沿W方向,再沿H方向,最终沿N方向。所以在内存的寄存次序是,榜首个元素是000,第二个沿C方向,即020,040, 060 。..一直到300,之后切换到W方向,001 021 041 061.。.301.。到了303后再切换到H方向,即004, 024 。.. 304,最终到了319,再切换到N方向,320,340 。..一直到639。

[b:0] 表明C方向,榜首个像素从一个通道到别的一个通道

[b:1] 表明从W方向,最终一个通道榜首个像素回到榜首个通道的第二个像素

[b:2] 表明在H方向,最终一个通道榜首行最终一个像素回到榜首个通道的第二行的榜首个像素

[b:3] 表明从N方向,从n=0 到n=1

NHWC其物理表明为000 020 。.. 300 001 021 。.. 283 303 004 。.. 319 320 340 。.. 。.. 339 359 。.. 639。能够了解成把一个batch的一个像素的一切通道先摆放起来,然后排下一个像素。n=0摆放完结后,再排n=1。

同理CHWN其逻辑表明,先沿N方向,再沿W方向,再沿H方向,最终是沿C方向。

[c:0] 表明从N方向,从n=0的榜首个像素到n=1的榜首个像素

[c:1] 表明从N方向,从n=1的榜首个像素回到n=0的第二个像素

[c:2] 表明在H方向,从n=1的榜首行最终一个像素回到n=0的第二行榜首个像素

[c:3] 表明从N方向,从n=1的榜首个通道最终一个像素回到n=0的第二个通道榜首个像素

CHWN其物理表明为 000 032 001 321 。.. 003 323 004 324 。.. 。.. 019 339 020 。..。能够了解成先把一个batch中N幅图画的榜首个通道榜首个像素摆放起来,然后排第二个像素;再排第二个通道,第三个通道。..

数据在内存中的偏移地址

深度学习中触及许多的数据核算,核算需求从内存中取出数据,因而需求核算出数据的偏移地址以便进行取数。有了上面的逻辑表明和物理表明,能够推导出4维逻辑表明(n,c,h,w)映射到一维内存中偏移地址的公式。

界说方位(n,c,h,w)表明第n个batch的第c通道的第h行的第w列,那么该方位在不同数据格局下,在内存中的偏移地址核算公式如下: NCHW: offset_nchw(n, c, h, w) = n * CHW + c * HW + h * W + w NHWC: offset_nhwc(n, c, h, w) = n * HWC + h * WC + w * C + c CHWN: offset_chwn(n, c, h, w) = c * HWN + h * WN + w * N + n 其间N、C、H、W为常量,n、c、h、w为变量

在NCHW中,CHW=C*H*W,表明一个Batch,能够了解成一个BGR 3通道的图片,表达的是一个立方体。HW=H*W,表明一个平面,能够了解成是BGR 3通道图片的一个通道(灰度图便是一个通道图片)。W是一行,能够了解成一个通道上的一行。

以上图为例,假如想核算出绿色圈,即341的方位(n=1,c=1, h=0, w=1)。咱们需求先越过n=0的数据(CHW),图中箭头1指向的蓝色框区域;再越过n=1的榜首个通道(HW),图中箭头2指向蓝色框区域;这时进入到了n=1的第二个通道,越过h=0行(0*W);最终越过w个数抵达偏移方位。

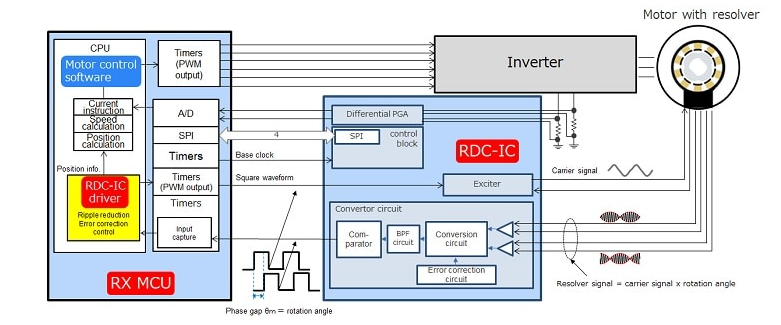

EdgeBoard为何运用NHWC

下面来剖析EdgeBoard挑选NHWC数据格局的原因。

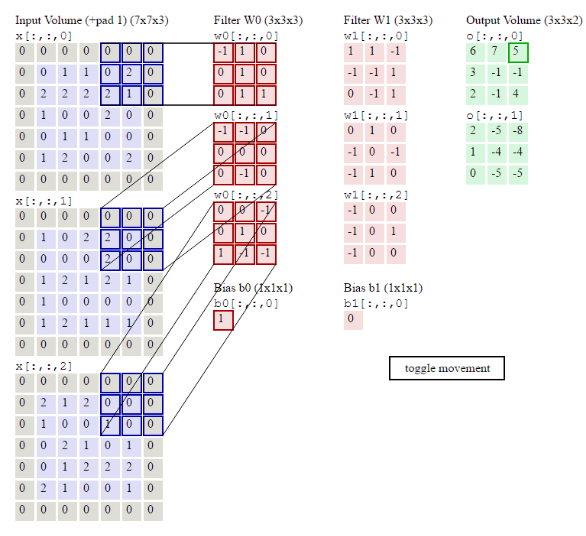

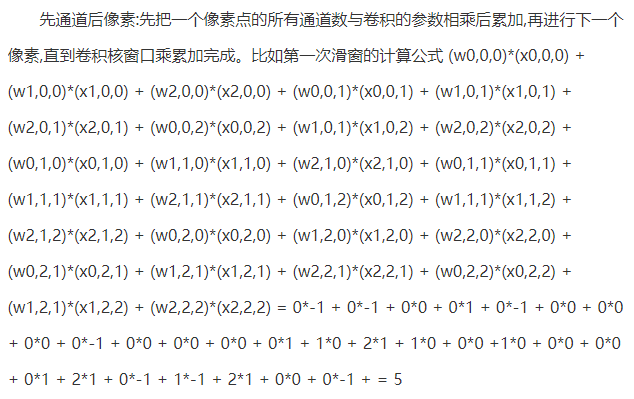

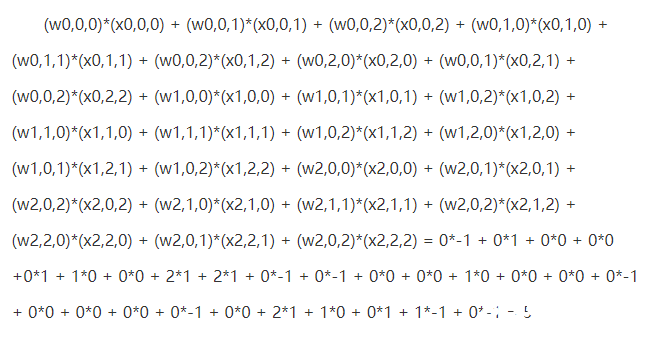

上图表明卷积的核算进程。依据卷积的运算特色,相同方位窗口一切通道数与卷积的参数相乘后累加,能够有下面两种核算方法:

先像素后通道:先把一个通道滑动窗口与卷积参数相乘后累加,再进行下一个通道,直到一切通道乘累加完结。比方榜首次滑窗核算公式:

能够看出两种方法核算的结果是相同。

而关于NHWC格局,即先通道后像素,是把一个像素的一切通道的数据放在一同。这样对应上图榜首个像素的3个通道值,第二个像素的3个通道值,第三个像素的3个通道值,它们在内存中的地址都是接连的,也便是说一次就能够把kernel榜首行需求核算的数取出,3×3的kernel需求3次取数。

而关于NCHW格局,即先像素后通道,是把一个通道的一切像素按次序摆放,这样关于一个3*3的卷积核,需求每取3个数就需求跳动n个数后,再取3个数。一个通道需求取3次,3个通道需求取9次。

在实践网络中,一般通道数会远大于卷积kernel数(不会像上图只要3个通道,一般是几十、几百个通道)。这样关于NHWC格局来说说,取数的次数会比NCHW少许多。对EdgeBoard来说,为了添加其所支撑网络的广泛性,削减对大输入尺度和高存储量权重网络的约束,选用NHWC的格局能够完结分批次地把Feature Map和Weight数据读取到FPGA的片上缓存,例如关于3×3的Kernel,咱们能够只读取三行(3WC)Feature Map的数据到FPGA内进行核算,即可得到一行输出数据,并传输到片外大容量缓存DDR,而不需依靠下一个3WC的Feature Map输入数据就可完结每一批次的输入输出数据传输。

再例如,咱们也可将Weight数据依据FPGA片上缓存的不同巨细分割成N份,一份一份发送到FPGA别离做卷积运算后,再传输回DDR做相应拼接,这等同于做一次大的卷积运算,优点在于能够依据不同容量的FPGA器材做不同匹配,大大提高了代码的硬件适配性。此外,因为C维度之间数据相关性较弱,选用NHWC格局更能发挥FPGA高并行度的核算特色,充分利用FPGA的算力。

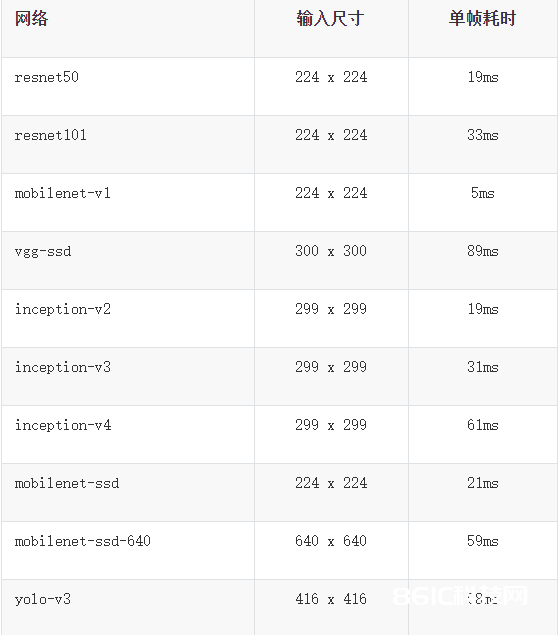

下表为EdgeBoard运用NHWC数据格局的网络功能:

责任编辑:gt