数字信号处理(DSP)技能在许多领域内具有广泛的用处,如雷达、图画处理、数据紧缩、数字电视和数据通信等。加法器和乘法器是构成一切DSP体系的根本结构,而加法运算是最根本的算术运算,无论是减法、乘法、除法或FFT运算,终究都要分解为加法运算。跟着在FPGA规划中加法功用需求的日益增长,加法树规划的日益增大,人们提出了许多完结加法功用的规划办法,以期在高的运算速度与低的逻辑占用之间求得最佳的完结作用。StratixⅡ是Altera公司推出的新一代高端FPGA,他选用了不同于以往系列FPGA的逻辑结构——自适应逻辑模块(ALM),这种ALM结构能够说是FPGA构架方面的革新。StraTIxⅡALM模块能够灵敏装备为3~7输入的查找表(LUT),他包括内置的加法器块,能够一次完结最多3比特的加法而不需求消耗额定的LUT资源。关于通用算术和加法树功用,StraTIxⅡ器材比其他FPGA架构供给了更好的功能和更少的逻辑占用。

本文提出了一种针对StraTIxⅡ中ALM特色的加法树规划计划,给出了一个在高速数字相关器中的实践运用,并进行计算机归纳测验验证。

1 、StraTIxⅡ的自适应逻辑模块(ALM)

FPGA的逻辑单元(LE)的经典结构是由一个4输入的LUT和一个触发器组成的。为什么是4输入而不是其他的逻辑结构呢,这是因为选用较“窄”的逻辑结构,比较节省硅片面积,可是整体功能比较差,而选用较“宽”的逻辑结构,整体功能比较好,可是糟蹋硅片面积,本钱较高。所以选用4输入的LUT只是在本钱和功能之间做的一个折衷。

图1给出的StratixⅡ的ALM正是兼有了“窄”的逻辑结构的高利用率和“宽”逻辑结构的高功能。ALM中的组合逻辑模块能够依据用户的需求由规划东西主动装备成需求的形式。能够配成5输入和3输入的LUT,或两个4输入的LUT等。别的,ALM内部独立于LUT之外还有两个3输入加法器,每个ALM中答应对3个不同的2 b数据进行加法操作。这种才能经过紧缩加法树中总的过程数,大大进步了加法树的功能,而且逻辑资源耗用也大大削减了,因为将3个1 b数据相加在StratixⅡ器材中只占用半个ALM,而关于传统的4输入LUT架构则需求2个LE。

图2列出了和传统的4输入LUT结构的FPGA相比较,选用ALM的StratixⅡFPGA器材例化3输入加法器的优势。从图2中能够清楚地看出,关于相同3个2 b数据相加的逻辑结构,传统4输入LUT结构的FPGA例化需2级完结,占用4个LE,而关于选用ALM的StratixⅡFPGA器材来例化,只需一个ALM即可。

2 、针对ALM的加法树规划

现在大多数FPGA都是根据传统的4输入LUT加上一个触发器的LE结构,如Altera的Stratix,APEX,Cy-clone和FLEX10K等器材族。他们在完结加法树时只能选用2输入加法树,而选用ALM结构的StratixⅡ器材完结加法树时,可依据需求选用3输入加法树或2输入加法树。这样,就能紧缩加法树总的过程数,进步加法树的功能。削减的加法树过程n可由以下公式计算出:

![]()

这儿N是指输入数据的数目。

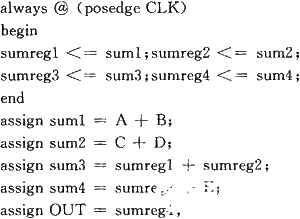

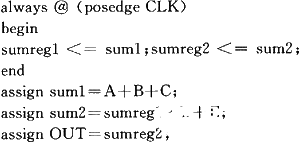

关于传统的FPGA,假如完结A+B+C三个数的加法器,最高频率的办法是先完结2个数的加法,如A+B,将和用寄存器打一拍,然后将寄存器的和与第三个被加数(C)相加。这种办法完结1比特加法器时,A+B相加将运用1个加法器和1个寄存器,即一个LE,需1级逻辑完结。这种思路一般被称为2输入加法树结构,将加法树逐级拓宽,能够完结更长的加法树结构。假如完结A+B+C+D+E五个数(16位)的加法树,运用这种2输入加法树办法共需3级寄存器缓存。其Verilog程序首要算法如下给出,选用器材StratixⅡEP2S15FC484-5,图3(a)给出了经过Synplify Pro 7.7归纳后的RTL视图。归纳成果为:默许束缚条件下,共需64个ALM,完结预算的时钟频率为400.00 MHz。

因为ALM对输入能够在3到7之间自在装备,那么关于上述16比特的5个数的加数求和的加法器,能够让ALM装备成6输入的LUT,运用6-LUT能够一起完结3比特加法,用2个3输入的加法器替代上述的4个2输人加法器来完结。其算法如下给出,在其他相同条件下,归纳后的RTL视图如图3(b)所示,归纳成果为共需32个ALM,完结预算的时钟频率为427.30 MHz。可见节省了50%的ALM资源。

3 、加法树的运用

加法树在许多运用中呈现,比方用在滤波器、乘法器、累加器、第三代(3G)无线基站的信道卡相关器等。下面以在数字通信体系中广泛运用的高速数字相关器为例来阐明加法树的运用。

在数字通信体系中,常用一个特定的序列作为数据开端的标志,称为帧同步字,发送端在发送数据前刺进帧同步字,接纳端假如收到帧同步字就能够确认帧的开始方位,然后完结发送和接纳数据的帧同步。数字相关器的作用是完结两个数字信号之间的相关运算,即比较等长度的两个序列间持平的位数。最根本的相关器是异或门。例如y=a○+b,当a=b时,y=0,表明数据位相同;当a≠b时,y=1,表明数据位不同。多位数字相关器能够由l位相关器级连构成。N位数字相关器的运算一般能够分解为以下两个过程:

(1) 对应值进行异或运算,得到N个l位相关运算成果;

(2) 计算N位相关成果中0或1的数目,得到N位数字中相同位和不同位的数目。

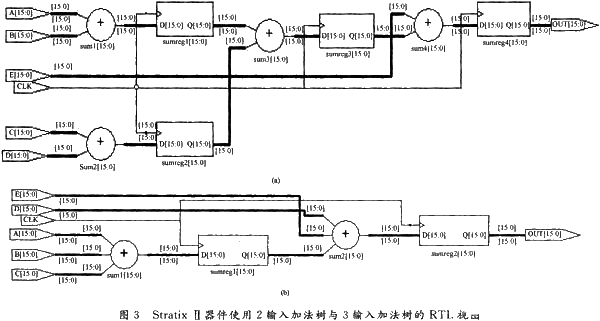

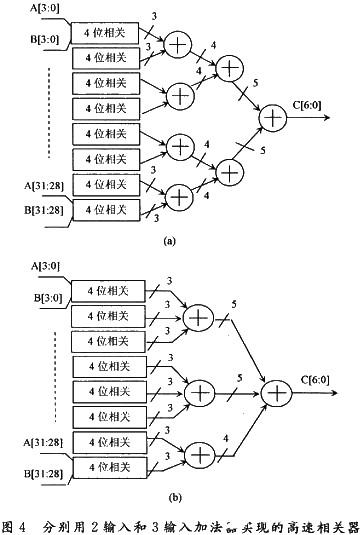

关于一个32位的高速数字相关器,因为完结起来需求的乘积项、或门过多,因此为下降耗用资源,能够分解为8个4位相关器,然后用3级加法器相加得到悉数32位的相关成果,这是传统的完结办法,如图4(a)所示。针对选用灵敏的ALM结构的StratixII器材,能够选用3输入加法器来改善加法树,只用2级加法树就可完结,如图4(b)所示。

选用器材StratixⅡEP2S15FC484-5分别用2输入加法器树和3输入加法器树来完结上述相关器,SynplifyPro 7.7对图4(a)归纳成果为占用80个ALUTs(自适应查找表)和56个FF(触发器),预算时钟频率为509.9 MHz。而对图4(b)归纳成果为占用65个ALUTs和41个FF,预算时钟频率为465.0MHz。可见尽管略微下降了时钟频率,但节省了大约20%的资源占用。

4 、结语

本文给出了运用StratixⅡFPGA完结加法树的计划及其在高速数字相关器中的运用。计算机归纳仿真成果表明,该计划与传统完结加法树的计划比较,能经过紧缩加法树中总的过程数,大大削减了对FPGA逻辑资源的占用,而且跟着加法树输入数据的数目添加,逻辑级和逻辑资源削减的百分比会更大。

责任编辑:gt