运用渠道:官方STM32F429DISCOVERY开发板,180MHz的主频,守时器频率90MHz。

相关标题:

(1)丈量脉冲信号频率f_O,频率规模为10Hz~2MHz,丈量差错的绝对值不大于0.1%。(15分)

(2)丈量脉冲信号占空比D,丈量规模为10%~90%,丈量差错的绝对值不大于2%。(15分)

思路一:外部中止

思路:这种办法是很简单想到的,并且对简直一切MCU都适用(连51都可以)。办法也很简单,声明一个计数变量TIM_cnt,每次一个上升沿/下降沿就进入一次中止,对TIM_cnt++,然后守时计算即可。假如需求占空比,那么就另外用一个守时器计算上升沿、下降沿之间的时刻即可。

缺陷:缺陷清楚明了,当频率前进,将会频频进入中止,占用很多时刻。而当频率超越100kHz时,中止程序时刻乃至将超越脉冲周期,发生巨大差错。一起更重要的是,想要丈量的占空比由于遭到中止程序影响,差错将越来越大。

总结:咱们其时第一时刻就把这个计划PASS了,没有相关代码(这个代码也很简单)。不过,该办法在频率较低(10K以下)时,可以拿来丈量频率。在频率更低的情况下,可以拿来测占空比。

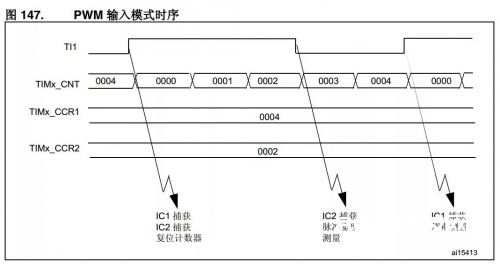

思路二:PWM输入形式

思路:翻遍ST的参阅手册,在守时器傍边有这样一种形式:

简而言之,理论上,通过这种形式,可以用硬件直接丈量出频率和占空比。其时咱们发现这一形式时欢天喜地,认为可以一步处理这一问题。

可是,通过丈量之后发现这种办法测试数据不稳定也不精确,数据不断跳动,且和实践值相差很大。ST的这些功用常常有这种问题,比方守时器的编码器形式,在0点处频频正负跳变时有可能会卡死。这些办法尽管省劲,稳定性却不是很好。

通过线性补偿可以必定程度上削减差错(参数在不同情况下不同):

freq=Frequency*2.2118-47.05;

这种办法无法完结要求。所以在这里我并不引荐这种办法。假如有谁可以有较好的程序,也欢迎发出来。

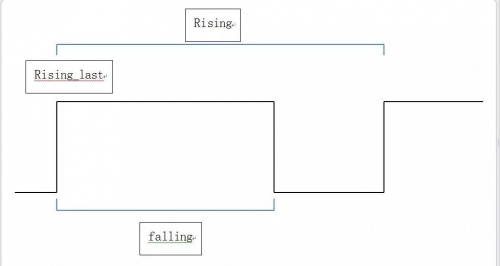

思路三:输入捕获

思路:一般来说,对STM32有必定了解的坛友们在丈量频率的问题上往往都会想到运用输入捕获。

首要设定为上升沿触发,当进入中止之后(rising)记载与前次中止(rising_last)之间的距离(周期,其倒数便是频率)。

再设定为下降沿,进入中止之后与上升沿时刻之差即为高电平时刻(falling-rising_last),高电平时刻除周期即为占空比。

该办法尤其是在中低频(<100kHz)之下精度不错。

缺陷:稍有经历的朋友们应该都能看出来,该办法依然会带来极高的中止频率。在高频之下,首要是CPU时刻被彻底占用,此外,更重要的是,中止程序时刻过长往往导致会错失一次或屡次中止信号,体现便是丈量值在实践值、实践值×2、实践值×3等之间跳动。实测中,最高频率可以测到约400kHz。

总结:该办法在低频率(<100kHz)下有着很好的精度,在考虑到其它程序的情况下,主张在10kHz之下运用该办法。一起,可以参阅以下的改善程序削减CPU负载。

改善:前述问题,约束频率前进的主要因素是过长的中止时刻(一般运用情形之下,还有其它程序部分的约束)。

所以进行以下改善:

1.运用2个通道,一个只丈量上升沿,另一个只丈量下降沿。这样可以削减切换触发边缘的推迟,缺陷是多用了一个IO口。

2.运用寄存器,简化程序

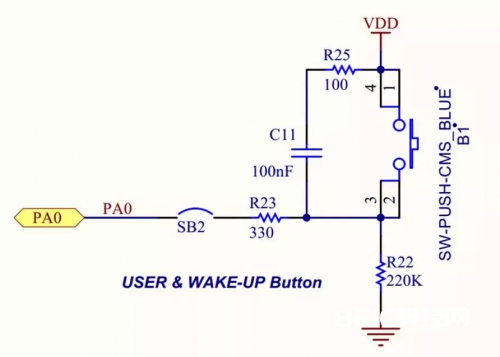

之所以改用TIM2是由于TIM5的CH1(PA0)仍是按键输入引脚。原本想来这应当也没什么,按键不按下不便是开路嘛。

所以,当运用他人的程序之前,请必定细心检查电路图。

这样,最高频率可以到达约1.1MHz,是一个不小的前进。可是,其根本问题——中止太频频——依然存在。

处理思路也是存在的。本质上,咱们实践上只需求读取CCR1和CCR2寄存器。而在内存仿制过程中,面临大数据量的转移时,咱们会想到什么?

明显,咱们很简单想到——运用DMA。所以,咱们运用输入捕获事情触发DMA来转移寄存器而非触发中止即可,然后将这些数据存放在一个数组傍边并循环改写。

这样,咱们可以随时来检查数据并计算出频率。

大神在回复中提出了几个改善定见,列出如下:

1.可以设定仅有通道2进行下降沿捕获并触发中止,而通道1捕获上升沿不触发中止。在中止函数傍边,一次读取CCR1和CCR2。这样可以节约很多时刻。

2.可以先进行一次丈量,依据丈量值改动预分频值PSC,然后前进精度

3.距离采样。例如每100ms采样10ms.

这样的改善应当可以将最高采样频率增加到2M.可是频率的进一步前进依然不可能。

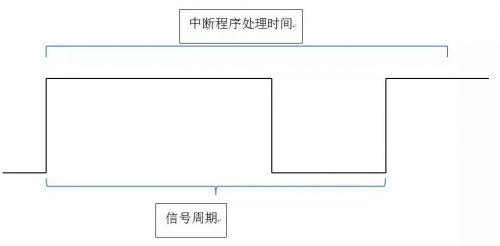

由于这时的主要矛盾是中止函数时刻过长,导致CPU还在处理中止的时分这一次周期就完毕了,使得终究丈量到的频率为实在频率的整数倍左右。示意图如下:

因而,高频时依然引荐以下办法。

综上,对这几种办法做一个总结:

外部中止:编写简单,通用性强。缺陷是中止进入频频,差错大。

PWM输入:全硬件完结,CPU负载小,编写简单。缺陷是不稳定,差错大。

输入捕获:可到达约400kHz。低频精度高,10Hz可到达0.01%以下,400kHz也有3%。缺陷是中止频频,无法丈量高频,幅值必须在3.3~5V之间。