比较于单目视觉,双目视觉(Stereo Vision)的要害差异在于可以使用双摄像头从不同视点对同一方针成像,然后获取视差信息,核算方针间隔。未来十年,为了完结从感知+预警到决议计划+履行的进化之路,高档辅佐驾驭体系(ADAS)将接入更多的传感器,完结更为杂乱的核算,一起具有更高的安全性。

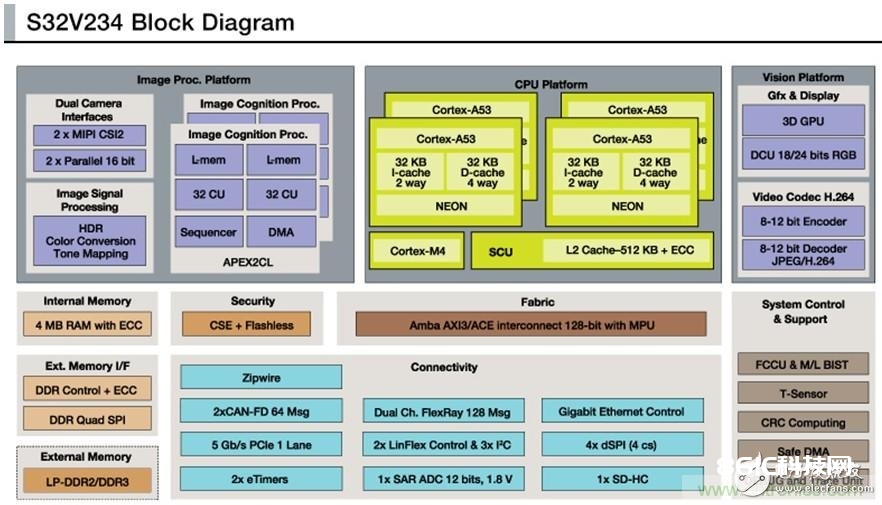

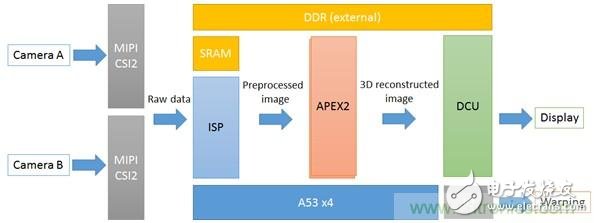

图1:S32V234结构图

S32V234选用了4颗ARM Cortex A53作为中心CPU,以取得更高的功用功耗比。别的,S32V234包含了一颗ARM Cortex M4来作为片上MCU,首要用于要害IO(如CAN-FD)的实时操控,并支撑AutoSAR操作体系。

芯片集成了两路MIPI-CSI2和两路16bit并行相机接口,以及Gbit以太网操控器,为图画传感器的输入供给了多种挑选。一起芯片内部包含了可编程的图画信号处理(ISP)硬件模块。使用嵌入式ISP,外部配搭的图画传感器可以输出raw data,然后下降物料本钱,节约空间尺度。别的,芯片还包含了两个名为APEX2CL的视觉加快引擎。每个APEX2CL具有64个本地核算单元(CU),并配有本地内存,经过SIMD/MIMD(单指令多数据/多指令多数据)的处理方法对图画辨认进程进行加快。 别的值得指出的是,考虑到ADAS体系对安全性和可靠性的苛刻需求,S32V234在规划时加入了比如ECC(过错查看与纠正),FCCU(毛病搜集与操控单元),M/L BIST(内存/逻辑内置自测)等多种安全机制,可以满意ISO26262 ASIL B~C的需求。

双目视觉简介

比较于单目视觉,双目视觉(Stereo Vision)的要害差异在于可以使用双摄像头从不同视点对同一方针成像,然后获取视差信息,核算方针间隔。详细到视觉ADAS使用来说,假如选用单目摄像头,为了辨认行人和车辆等方针,一般需求大规模的数据收集和练习来完结机器学习算法,并且难以辨认不规则物体;而使用毫米波雷达和激光雷达进行测距的精度尽管较高,可是本钱和难度亦较高。所以,双目视觉的最大优势在于保持开发本钱较低的前提下,完结必定精度的方针辨认和测距,完结FCW(前方磕碰预警)等ADAS功用。

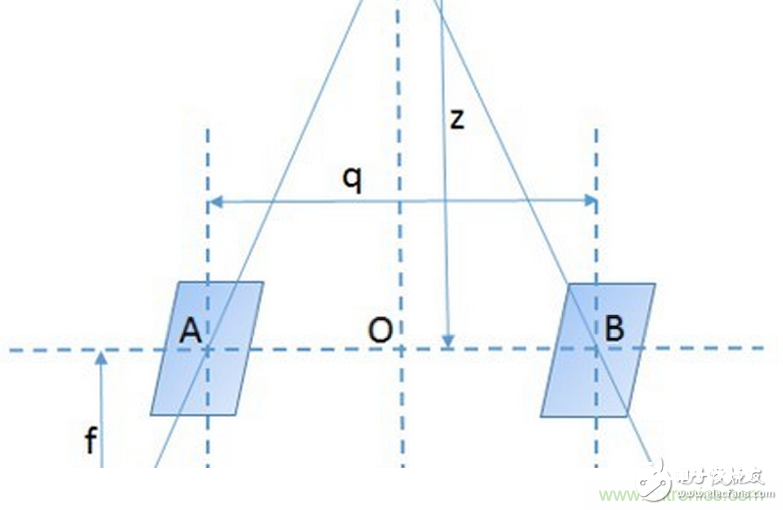

双目视觉测距的基本原理并不杂乱,如图2所示,P为方针点,它在左右两个相机(镜头中心别离为A和B)上的成像点别离为E和F,则P点在两个相机中的视差为d=EC+DF。依据三角形ACE与POA以及三角形BDF与POB的相似性,推导可得d=(fq)/z,其间f为相机焦距,q为两相机光轴的间隔,z为方针到相机平面的间隔。则间隔z=(fq)/d,而f和q可认为是固定参数,所以求出视差信号d即可求得间隔z。

图2:双目视觉测距原理

依据双目视觉的测距原理,一般将其完结进程分为五个过程:相机标定,图画获取,图画预处理,特征提取与立体匹配,三维重构。其间,相机标定是为了得到相机的表里参数和畸变系数等,可以离线进行;而左右相机图画获取的同步性,图画预处理的质量和一致性,以及立体匹配(获取视差信息)和三维重构(获取间隔信息)算法的实时性要求带来的巨大运算量,对在嵌入式渠道上完结双目视觉ADAS提出了应战。

根据S32V234的双目视觉ADAS解决计划

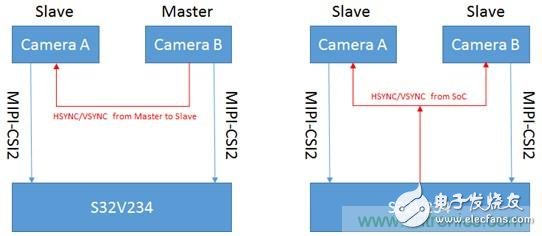

S32V234片上具有两路MIPI-CSI2相机接口,每一路最大可供给6Gbps的传输速率,可用于左右两路相机的视频输入。因为两路相机别离输入两个MIPI通道,需求考虑二者之间的同步问题。在外部图画传感器的合作下,S23V324可以支撑不同的同步方法。如图3所示,图画传感器一般具有场同步信号(VSYNC)和行同步信号(HSYNC)来进行信号同步:当两路相机作业在主从形式时,由Master向Slave发送同步信号;当两路相机都作业在从形式时,可以由S32V234内部定时器发生同步信号,一起发送给两路相机。

图3:双目相机同步计划

在S32V234获取外部相机的图画信号后,可以由内部的ISP进行预处理。ISP模块包含多个针对ISP功用进行优化的处理单元,使用片上SRAM对输入信号和中心处理成果进行缓存,并选用一个根据ARM Cortex M0+的专用协处理器来办理ISP处理单元的时序,然后完结图画信号的像素级处理。因为ISP坐落芯片内部并且可以灵敏编程,所以不只可以节约双目相机外置ISP的本钱,并且其运算资源和带宽可以支撑对双路高达1080p@30fps图画信号的实时处理,确保了双路图画信号的质量和一致性。

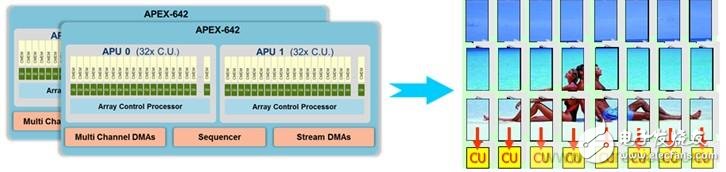

在双目视觉ADAS使用中,最大的应战来自于对两路图画进行立体匹配和三维重构所需求的巨大运算量。以FCW使用为例,既要求视差信号的提取具有满意的精度以确保测距精度,又要求处理帧频保持必定水平以确保预警的响应速度,因而要求嵌入式渠道具有满意的处理才能。S32V234中集成的图画加快引擎APEX2的结构如图4所示,其并行核算结构和专用DMA等规划确保了对图画信号具有极高的处理功率。详细来说,ISP对图画信号预处理结束后送入DDR,APEX2引擎将图画切割后经由专用DMA将其送入每个CU对应的本地内存CMEM中,而立体匹配所需求的块匹配(Block Matching)等算法可以在不同的CU中并行处理,处理结束后的数据经由DMA送回DDR,由CPU进行进一步处理(如生成预警信号),或送至专门的DCU(Display Control Unit)模块输出显现。

图4:APEX2架构及图画处理示意图

综上所述,根据S32V234的双目视觉使用数据流如图5所示。在该使用中,数据流依照ISP-APEX2-DCU的方向活动,A53作为主控CPU完结逻辑操控和必要的数据处理。经过这种流水线式的处理方法,可以使各部分核算资源充分使用,进步核算功率。

图5:根据S32V234的双目视觉数据流

使用S32V234开发板建立双目视觉渠道,对双路720p@30fps视频信号进行处理,其输出成果如图6所示。其间从左至右的三幅图中方针与相机的间隔别离为1m,2m,3m,显现成果以冷暖色彩的改变表征方针间隔。成果表明,S32V234可以对双目视觉信号进行实时处理,正确得到三维测距成果,一起辅以芯片的各项安全性规划,可以满意双目视觉ADAS体系的需求。

图6:S32V234双目视觉显现成果

总结

恩智浦的视觉ADAS专用芯片S32V234集成了图画信号处理器ISP,图形加快引擎APEX2,3D GPU等专用核算单元,经过流水线式的处理架构使各个异构核算资源充分使用;不同核算模块对OpenCV ,OpenCL和OpenVG等多种API的支撑增强了算法的可移植性;而契合ISO26262规范的功用安全规划使得芯片可以满意ADAS体系对安全性的苛刻需求。S32V234支撑包含双目视觉在内的多种视觉ADAS和传感器数据交融解决计划,使得咱们在通往无人驾驭的道路上迈出坚实的一步。