1.布景

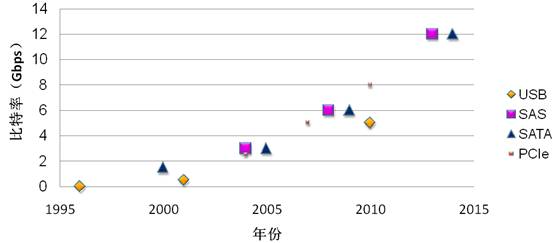

网络、多媒体、移动通讯对进步数据吞吐率的需求日积月累,推进计算机和通讯技能不断打破速度极限。图1是当时干流计算机外设总线的速率演化状况。

图1干流高速串行标准演进图

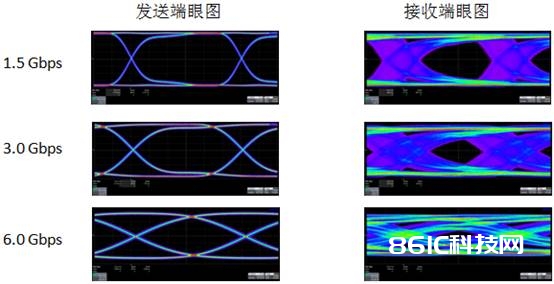

数据率越高,信道趋肤效应和介质损耗对信号质量的影响越严峻,在时域上体现为:边缘变缓,码间搅扰加剧,颤动添加。一般运用眼图来评价高速信号质量。下图是三种速率的信号在发送端和接纳端别离测得的眼图。能够显着看出,速率越高,接纳端的眼图闭合程度越小。能否在接纳端正确检测出受损的信号,是高速收发器芯片设计者面对的应战。

图2不同速率信号的失真程度

在以往的高速串行信号一致性测验标准里,一般都要求测验发送端功能,比方输出电压摆幅、上升时间、颤动、眼图等。跟着速率进步,只是测验信号发送端现已不能确保高速链路能按预期功能正常作业,有必要对接纳机功能也进行测验。USB 3.0、PCI Express 3.0以及SATA和SAS标准现已明确要求进行接纳机测验。

2.接纳机测验原理

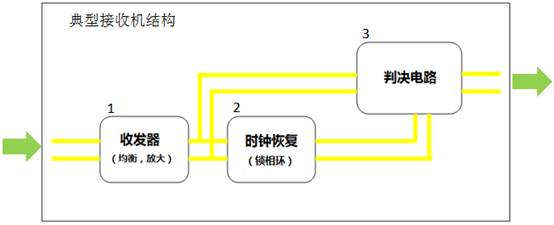

在发送器测验中,一般运用示波器直接丈量输出信号的起伏、上升/下降时间、眼图和颤动,然后评价发送器的驱动才能、预加剧、参阅时钟稳定性等各项功能。在接纳端,典型的接纳机芯片框图如下:

图3典型接纳机内部框图

它包含

信号检测(扩大,均衡)

根据锁相环(PLL)的时钟康复

判定电路(并转串,线路码解码)

对接纳机功能的测验实践便是对以上三个首要部件的功能测验:

1)能够识别出多小起伏的信号,即接纳灵敏度

2)时钟康复电路中的锁相环能否去除低频颤动

3)能够正确识别出带有多大颤动的数据,即颤动容限

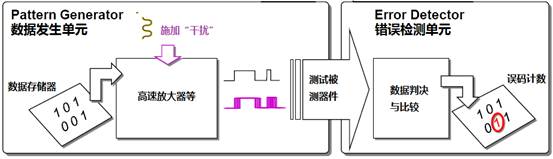

不像发送端能够直接丈量被测件(Device Under Test,DUT)输出的信号,信号进入接纳机内部后无法直接观测,一般运用仪器发生必定样本量、必定特征的鼓励数据流给DUT。这些特征一般是多种形式的“搅扰”,仪器通过施加不同程度的“搅扰”,测验接纳机的体现。

这种仪器一般是误码率测验仪(Bit Error Rate Tester,BERT)。简略的说,误码率测验便是发送已知数据给被测接纳机芯片,通过量化被过错判定数据的份额来衡量接纳机芯片的功能。在功能上,误码率测验仪包含数据发生(Pattern Gernerter)和过错检测(Error Detetor)两个部分,即前者发生鼓励,后者检测呼应。

图4误码率测验仪作业原理框图

测验时,误码率测验仪和DUT收发互连构成回环,如图5。Pattern Generator宣布带有“搅扰”的信号给DUT。DUT将接纳到的数据通过内部回环又发送回给误码率测验仪。一般通过DUT内部的检测和时钟域改换,发送回去的数据不再带有“搅扰”。

图5误码率测验仪与DUT回环衔接

DUT一般有两种回环形式:

1)外部BERT(或称Retimed Loopback)

图6外部BERT测验框图

DUT将RX端收到的BERT数据从TX端发送回去,由BERT比照发送和接纳到的数据