0 导言

在信号处理领域中,依据FPGA+DSP的结构规划现已是体系开展的一个重要方向。跟着该体系规划的广泛运用,功用变得愈加丰厚,本钱日趋低价。而在某些小型化运用的场合中,对体系体积的要求越来越高,因而如安在硬件层次上缩小体系体积,现已是必需求考虑的要点。除了选用高集成度的芯片、布局愈加紧凑的电路结构之外,优化体系的功用完结办法则能在更高层次上减小体系体积。

关于FPGA+DSP的根本架构,DSP电路模块的首要构成为DSP芯片和存储其程序的FLASH芯片,现已为最小结构,无法精简。FPGA电路模块常用的构成办法为FPGA芯片和相应的装备芯片。而FPGA有多种装备办法,不同的装备办法,所需芯片会有差异,因而选用芯片数量少的装备办法能够在必定程度上节省电路板的面积。

不同厂家、不同系列的FPGA芯片,装备办法都存在有差异。关于Xilinx公司的Virtex-Ⅱ系列FPGA来说,首要有自动串行、自动并行、被迫串行、被迫并行和鸿沟扫描5种装备办法。其间,鸿沟扫描办法只能烧写断电即丢掉的.bit文件,不能在体系中独自运用;自动串行和自动并行的装备办法需求额定的装备芯片,不利于精简体系;被迫并行和被迫串行的装备办法都是依托FPGA外部衔接的微处理器来进行装备的,而FPGA+DSP结构中的DSP正好能够充任装备电路中的微处理器,这样就能够省去装备芯片和JTAG电路等相关模块,能在必定程度上缩小体系体积。本文挑选了被迫的并行装备办法,原因在于更高的装备速率,此种装备办法在工程实践中有着重要意义。

1 装备办法

1.1 装备文件格局

装备FPGA便是要把开发东西现已综合好的程序文件按必定的时序写入FPGA芯片中。而Xilinx的开发环境能够依据用户的挑选发生多种文件格局,以不同的后缀名区别。不同的文件格局包含了不同的信息,有不同的用处。最常用的格局有.mcs格局、.bit格局和.bin格局,其间,.mcs文件是给FPGA的装备芯片烧写程序时运用的,而.bit和.bin文件都是直接给FPGA烧写程序时运用的。所不同的是,.bin只包含了最原始的装备数据,而.bit文件除包含有最原始的装备数据外,还在最初添加有头部冗余信息,里边包含了当时ISE工程的姓名、器材类型、编译时刻等。这部分信息是不应该烧写到FPGA芯片中去的,因而,本文挑选运用.bin文件来对FPGA进行装备。一般的,此装备文件数据都是以Xilinx指定的16进制同步字符FF FF FF FF AA 99 55 66最初,并在重复4次16进制同步字符20 00 00 00后结束。

因为被迫并行的装备办法省去了装备芯片,因而,FPGA程序需求和DSP程序一起存入FLASH芯片中。本文挑选运用AD公司的DSP,其烧写FLASH用的程序文件格局为.ldr,每行是由16进制的0xXXXXXXXX数据组成。所以,应该对FPGA所用的.bin文件进行格局转化。运用Matlab东西,能够完结这一功用。要留意的是,.bin文件其实是ASCII码办法,要转化成ASCII码的二进制码才干运用。.bin文件是由若干个2位的16进制数据构成的,对每个数据a(i)首要别离提取高低位,可通过Matlab的函数floor(a(i)/16)和mod(a(i),16)来别离完结。然后对提取后的数据d进行格局码转化,相应的matlab程序如下:

if(d《10)

d=d+48;

else

d=d+55;

end

1.2 装备管脚

与FPGA装备相关的管脚能够分为2类:专用管脚和可复用管脚。专用管脚的作用是固定的,而可复用管脚在装备阶段作为装备管脚,装备结束后能够装备为通用的IO管脚,也能够持续作为装备管脚。装备管脚首要有:异步复位PROG_B,初始化INIT_B,装备时钟CCLK,数据输入D0-D7,加载成功指示DONE,写信号RDWR_B,片选信号CS_B,形式挑选M0~M2,忙指示BUSY(并行加载且钟速率大于50 MHz时才运用)等。需求留意的是,一般的微处理器数据格局是little endian格局,D0位为最低有用位,而Xilinx的FPGA选用了big endian格局,在接纳程序数据时,D0位是最高有用位。而.bin文件仍选用littIe endian格局,其最高有用位是D7位,所以需求对数据进行位次序转化。在本文中,为了简化操作,直接在硬件衔接进步行了数据位的次序转化,即DSP的D7位和FPGA的D0位相连,DSP的D6位和FPGA的D1位相连,以此类推。

1.3 装备流程

FPGA的上电装备进程大致能够分为4个阶段:上电、初始化、数据加载和发动。详细完结的操作如下:

(1)上电。内核供电VCCint大于2.5 V,管脚供电电压VCCO大于1.0V,上电即可完结。

(2)初始化。上电完结后,外部输入低电平PROG_B信号,复位装备寄存器,一起,FPGA拉低INIT_B信号,来指示其正在进行内部装备寄存器的铲除。当PROG_B为高时,INIT_B仍要坚持一段时刻直至装备寄存器彻底铲除。PROG_B信号至少需求300ns,无最大值约束。本文中的PROG _B信号由DSP供应。

(3)数据加载。在INIT_B信号的上升沿,FPGA会采样它的装备形式管脚M0~M2来挑选不同的装备办法,本文的被迫并行形式,需求M0~M2值为:011。然后在INIT_B信号为高时,开端进行装备数据加载。在同步字符加载完结后,真实的装备逻辑数据开端被加载。在数据加载结束而且做了2次正确的CRC查验之后,开端进入FPGA发动阶段,不然,FPGA输出INIT_B为低,偏重新来进行装备。

(4)发动。CRC校验正确,则FPGA拉高指示信号DONE,然后再需求4个CCLK来激活一切的IO管脚,使能并初始化内部RAM、触发器等,终究完结FPGA的发动进程。

在生成FPGA的.bin文件时,能够设置加载FPGA时运用的时钟CCLK频率,可是,这个频率只对自动加载办法有用,被迫办法时,CCLK时钟由外部供应,与此参数无关。

2 硬件完结电路

2.1 硬件结构

本文选用AD公司出产的ADSP-TS101这款芯片作为装备FPGA的主处理器。ADSP-TS101是一款极高功能的静态超标量处理器,一起支撑浮点和定点处理,最高作业频率为300 MHz,地址规模4 GB,最大支撑16MB的PROM。从地址的0x08000000~0xFFFFFFFF为外部存储器空间的一部分,能够拜访独立的外围设备,彻底能够满意片外程序的寻址。为了完结装备FPGA的时序,需求DSP有灵敏可控的引脚信号。而ADSP-TS101的4个标志引脚信号FLAG3~FLAG0答应在ADSP-TS101和其他的设备之间传递位信号。任何一个标志引脚既能够作为输入也能够作为输出,且ADSP -TS101的许多指令都能够以标志引脚的输入作为履行条件,能够在多处理器和其他接口之间进行高效的通讯和同步。因而,能够将此4个管脚和FPGA进行衔接,模仿完结FPGA的装备时序。

存储芯片选用Spansion公司的高功能FLASH芯片S29JL064H,最小拜访周期为55 ns,其能够装备成8M×8 b的存储办法。而Virtex-Ⅱ系列FPGA的装备数据包含装备数据帧和装备寄存器数据,装备寄存器数据都为40×32 b,即1 280 b,装备数据帧会因器材不同而有改变,关于XC2V1000器材来说,装备数据帧为4 082 592 b,总的装备数据不到4 Mb。所以,此存储芯片彻底能够满意FPGA和DSP程序的存储。关于FLASH存储空间的区分,选用一分为二的办法,DSP和FPGA程序各占一半空间。即,从地址0x00000~0x3FFFFF这4 MB空间用来存储DSP程序,剩下的4MB空间0x400000~0x7FFFFF存储FPGA程序。

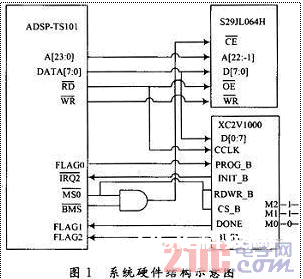

体系的硬件结构示意图如图1所示。由DSP的RD信号充任FPGA的装备时钟CCLK,FLAG0信号模仿FPGA的PROG_B信号,FLAG1和FLAG2别离作为FPGA的DONE信号和BUSY信号的输入。此体系在规划时,选用了DSP,FPGA,FLASH共用数据总线的办法,所以当DSP从FLASH芯片中读取FPGA的加载数据并出现在总线上的时分,能够直接被FPGA抓取来完结FPGA程序的正常加载。

2.2 作业时序

体系上电后,DSP发动DMA通道0,从FLASH地址0开端,把一个256 word的程序块传送到内部存储器地址0x00~0xFF。然后,DSP开端从0x00履行加载核,加载核将后续运用代码和数据加载至地址0xFF之后的内部存储器内。最终,加载核发动一个256 word的DMA,使其本身被作业程序代码掩盖。至此,DSP即从地址0x00开端履行作业程序。在作业程序中首要从FLASH存储器中读取FPGA的加载程序,并给出相应的加载时序,完结FPGA程序加载。详细的作业时序,如图2所示。

3 结语

跟着FPGA+DSP的体系结构在电子规划领域中运用的日益广泛化,在不添加其它额定器材的前提下,依托DSP模仿FPGA加载时序,对FPGA运用了被迫并行的装备办法。此办法在必定程度减少了规划冗余,完结了小型化和低本钱。运用于电路体系中,作业安稳牢靠,灵敏高效。