1.导言:

跟着信息技术的开展和微型计算机的遍及运用,计算机已成为现在运用最为广泛的信息处理和信息传输的电子设备。因为计算机的特别结构方法与作业方法,它不可避免地会向空间辐射电磁波 ,其信息电磁走漏问题现已对信息安全和保密构成了严重威胁 。研讨标明,视频电缆的辐射在整个视频通路的辐射中占主导地位 。因而,假如咱们在视频信号传输到显现器之前就对其进行处理,就能够有用地削减视频信号被截获的可能性,而一般视频信息在视频电缆中是串行传输方法,假如选用并行数据传输,并行数据即便在走漏后也是极难复原的 。本文所规划的视频信息收集体系便是把视频信号在发送到视频电缆前先进行处理再传输到电缆上,选用现场可编程逻辑阵列(FPGA)为中心处理单元,体系程序在QUARTUSII环境中通过归纳仿真,成果标明整个体系既满意视频体系对实时性的要求,又削减了信息走漏的可能性,验证了计划的可行性。

2.体系描绘:

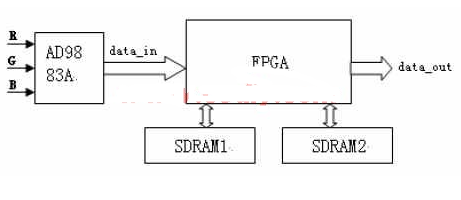

体系简化结构如图1所示,选用AD公司高性能视频专用模数转化器件(ADC) AD9883,收集三路R,G,B模仿视频信号,以高性能、高集成度、低功耗系列FPGA作为中心部件,运用FPGA的在体系可编程以及操控逻辑完结方法灵敏等特色,发生体系需求的时序,完结数字视频信号的读取和两片SDRAM的替换读写,并将以像素为单位的视频信息转化为位平面格局。FPGA处理完后就将成果通过并行电缆传输至显现端适配卡,而显现端适配卡则担任将位平面信息复原为像素格局。该体系能够完结实时视频数据流的无缝缓冲,一起完结对视频信号的并行传输,下降在数据传输进程中的电磁走漏。体系首要包含A/D转化部分、帧存取部分和数据改换部分,下面分别对这三个部分进行介绍。

3.A/D转化部分

A/D转化部分选用的是AD9883,其首要特色是:1)高达300M的带宽和140MHZ的转化速率;

图1 收集体系结构图

2)三路独立的0-1.0V的输入信号规模,十分合适采样视频信号;3)供给I2C总线接口,以习惯多种运用 [4]。

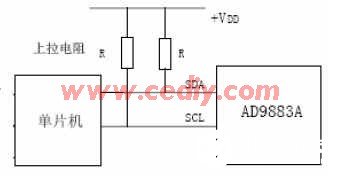

AD9883芯片在运用前需求依据实践的功用目标对内部寄存器进行初始化,初始化进程依托AD9883的SDA和SCL两引脚进行,时序契合I2C总线时序规范。选用支撑I2C总线协议的P89LPC932A1PLCC28单片机完结对AD9883的初始化,硬件衔接如图2,

图2 AD9883A初始化电路图

4.帧存取部分:

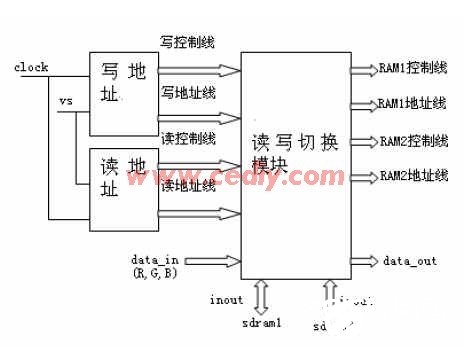

输入和输出缓冲电路一般有三种结构方法:双口RAM结构,FIFO结构,乒乓缓存结构 [5]。数字视频处理体系的杰出特色是视频数据的流量十分大,因而,体系有必要树立快速、有序的视频数据输入、输出机制,尽可能选用高速的FPGA,并在此基础上,选用习惯于高速FPGA的乒乓缓存结构。因为SDRAM一起具有SRAM存取速度快和DRAM集成度的长处,所以在这儿选用SDRAM作为帧存储单元,两片SDRAM读写地址和切换信号的发生均由高速FPGA完结,其全体结构如图3所示。

4.1SDRAM作业原理

SDRAM与SRAM不同,它只能将数据坚持很短的时刻。为了坚持数据,SDRAM有必要隔一段时刻改写一次,假如存储单元没有被改写,数据就会丢掉。SDRAM一般包含2个或4个bank,由地址线复用选通行和列地址拜访SDRAM内部存储单元,这种方法有用的削减了地址线,扩展了地址拜访空间。当规划FPGA完结对SDRAM的读写操控时,首要有必要对SDRAN进行初始化装备,即写形式寄存器,以确认CAS潜伏期,突发传输形式等作业形式;然后,通过激活指令激活对应地址的bank,一起输入行地址。最终,通过读指令或许写指令输入列地址,将相应数据读出或许写入到对应的地址。操作完结后用相关指令间断读或写操作 [6] [7] 。

图3 帧存取单元电路图

4.2写地址发生电路:

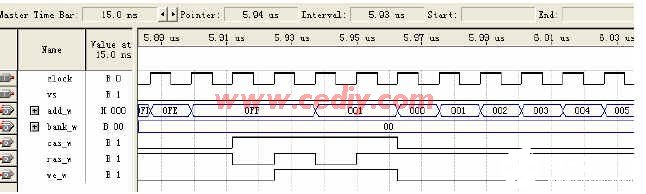

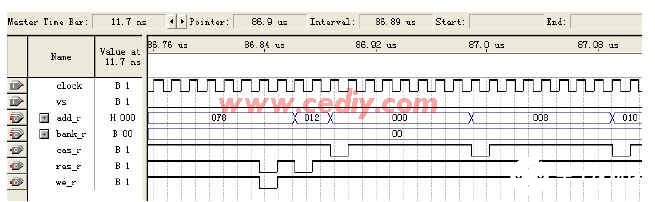

写的进程是将三路24bit R,G,B数字信号写入SDRAM中,所选用SDRAM是32位,剩下高8位补0。写地址发生电路发生数据写入RAM时需求的行,列选通信号ras_w,cas_w,写答应信号we_w,写地址信号add_w以及块挑选信号bank_w。写地址发生电路中心是两个11位计数器,当列数计到最大列数值时,通过预充电指令封闭所内行,并把行数加1,鄙人一个时钟周期先激活下一行,再进行写入,写地址发生仿真波形如图4所示。

图4 写地址发生仿真

4.3读地址发生电路

读的进程是将存储在SDRAM中的数据读到视频传输电缆上,读地址相同发生读RAM所需求的操控及地址信号。与写地址操控电路不同的是,读取进程有读潜伏期CL,即从CAS与读取指令发出到第一笔数据输出的这段时刻,所以在一行读完的时分,先履行两个空操作指令再预充电封闭所内行。一起在读方法上选用突发接连读取形式,突发长度BL设定为8,只要在开始列地址发送列地址和读指令即可,今后的寻址与数据的读取主动进行,这样能够大大下降对操控资源的占用,读地址发生仿真波形 如图5所示。

图5 读地址发生仿真

4.4读写切换电路

读写切换电路完结两片SDRAM的替换读写,在一帧时刻内一个SDRAM向显现器输出图象信号,另一个接纳来自显卡端的R,G,B信号,鄙人一帧两个SDRAM进行读写切换,这样循环下去。读写切换信号switch由场同步信号VS通过二分频发生,周期为2倍场同步信号周期,在其为低电平时,向SDRAM1写入数据,高电平时从中读出数据。除了完结读写地址信号切换,还要完结数据输出切换,这儿把SDRAM数据线与FPGA的接口界说为inout端口类型,由switch信号决议端口处于输出仍是输入形式。

5.数据改换部分

前面说过,把串行视频信号转化为并行信号能够大大下降信号在视频传输电缆上的信息走漏,但假如简略的将模仿视频信号转化为数字信号后直接进行传输,尽管数据是并行传输的,但一起传输的仅仅一个像素的不同位灰度信息,因而,从像素视点来考虑,仍然是串行传输的。所以在视频信号送至传输电缆之前就进行位面分层格局转化,使得并行电缆上能一起传输多个像素,完结真实意义上的并行,即依据像素的并行传输。

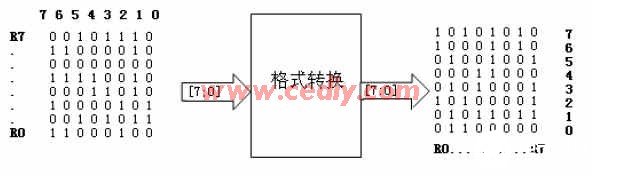

以赤色信号为例,FPGA从SDRAM中读出8个像素的R(赤色,8位)灰度数据,通过转化后成为位面分层格局,再通过8次并行接连输出,宽度为8位,这样将8个像素的R灰度数据R7-R0一起接连输出,R灰度数据位面分层示意图如图6所示。通过接纳端电路的处理,将会复原到原始的灰度数据。这样,就将传统的串行模仿传输,变为并行数字传输,增加了信息被截获后复现的难度,确保了信息的安全传输。

图6 位面分层输出示意图

6.定论

以高速FPGA作为中心处理器材,完结了防视频信息走漏体系数据发送端的规划,选用SDRAM作为缓冲存储器,在数据发送端先对视频信号进行位面分层格局转化,完结真实意义上的象素并行传输,削减了信息走漏的风险,通过软件仿真和硬件完结,证明了此计划的可行性。

本文作者立异点:

1.器材挑选:选用视频专用ADC,高速可编程逻辑器材FPGA,选用SDRAM作为缓冲存储单元,速度快,确保了视频信息传输的实时性要求;

2.结构规划:因为SDRAM的队伍地址复用等特色,选用FPGA作为中心处理器,在一片FPGA内规划了SDRAM的读/写,切换操控器;

3.防信息走漏算法:许多参考文献中指出,并行传输的信号很难被复原;因而在视频信息发送到传输电缆之前就把串行传输的信号转化为并行,这儿的并行不是简略的将模仿视频信号转化为数字信号后直接进行传输,尽管数据是并行传输的,但一起传输的仅仅一个像素的不同位灰度信息,因而,从像素视点来考虑,仍然是串行传输的。所以在视频信号送至传输电缆之前就进行位面分层格局转化,使得并行电缆上能一起传输多个像素,完结真实意义上的并行。

责任编辑:gt