导言

多节点体系,在现在的许多电子体系运用场合都可以看到。这种多节点体系因为具有结构可扩展性、功用装备的灵敏性以及便于查找毛病节点等杰出的可维护性得到了越来越广泛的运用。一般,多节点体系各个节点的首要硬件构成有很大的相似性。特别是近年来, FPGA 这个强壮的渠道让多节点体系各个节点的硬件构成具有了更广泛的通用性。尤其是跟着 IP 核技能的推行,再加上一些功用强壮的 CPU 核的呈现,如 Xilinx 公司供给的 PicoBlaze 和 MicroBlaze 等,使得现在的许多体系的首要功用都可以由大容量的 FPGA 完结,而无需再运用比较贵重的高功用微处理器。

关于节点体系,这将大大下降体系本钱。关于由大容量 FPGA 构成的多节点体系,体系的晋级是一个费时吃力的作业。此刻,FPGA 的长途晋级才能就显得尤为重要。关于包括 arm、DSP、PowerPC 等高功用嵌入式微处理器的多节点体系,运用这些嵌入式微处理器,选用 SELECTMAP 对 FPGA 进行加载并完结长途晋级,无需添加过多的外部器材,是十分经济和高效的。但关于中心器材便是大容量 FPGA 的体系,假如由 FPGA 本身来接纳晋级数据并写入存储装备数据的非易失性存储器,一旦晋级失利,将无法再次晋级,然后约束了它在许多需求高可靠性要求或许维护人员不便于抵达的场合的运用;而假如单纯为了完结体系的长途晋级而参加价格贵重的嵌入式微处理器,又会较大地添加体系本钱和复杂性。针对这种状况,笔者规划了运用 ATmega64 单片机和 RS485 总线,加上接入以太网的主控计算机构成的长途晋级体系,处理了上述问题。

1 体系规划

1.1 体系结构规划

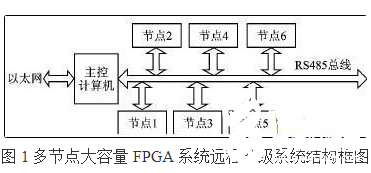

长途晋级体系首要由一台接入以太网的主控计算机、半双工 RS485 总线以及各个子节点构成,组成结构如图 1 所示。主控计算机通过以太网从外部获取整个体系各个节点的晋级数据,然后通过 RS485 总线向各个子节点发送其对应的晋级数据,完结多节点体系的晋级。RS485 总线选用一主多从的半双工办法,主控计算机为总线的主操控器,只能由它向各个节点建议通讯衔接,其他子节点只能呼应主控计算机的操控指令。

1.2 节点晋级原理

各个节点通过 RS485 总线与主控计算机相连,在无晋级数据时,总线可以用来传输主控计算机对各个节点的查询和操控指令。主控计算机与各个节点的通讯协议可以选用具有查询操控帧、应对帧和数据帧 3 种帧类型的协议。只要主控计算机可以发送查询操控帧,查询或设定各个节点的长途晋级状况或工况信息。子节点接纳主控计算机的指令和数据,发送应对帧,并完结本身的晋级。

2 子节点的硬件规划

2.1 子节点硬件结构框图

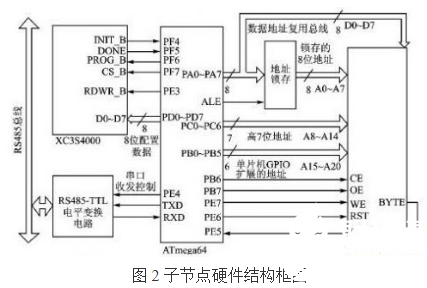

如图 2 所示,以一个由 Xilinx 公司的 XC3S4000 大容量 FPGA 构成的体系为例,长途晋级体系子节点的硬件电路首要包括: ATmega64 单片机,用于存储大容量 FPGA 装备数据的 Flash,以及接入 RS485 总线的半双工总线收发器。ATmega64 单片机用于完结对大容量 FPGA XC3S4000 的加载,以及从 RS485 总线接纳 FPGA 的晋级数据并写入具有 2 MB 存储空间的 Flash 存储器 SST36VF1601C 中。RS485TTL 电平改换电路选用 RS485 收发器 SP485R。

2.2 子节点硬件规划阐明

在子节点的硬件规划中,ATmega64 单片机是完结整个晋级功用的要害。ATmega64 是依据增强的 AVR RISC 结构的低功耗 8 位 CMOS 微操控器。因为其先进的指令集以及单时钟周期指令履行时间,ATmega64 的数据吞吐率高达 1 MIPS/MHz,然后可以缓解体系在功耗和处理速度之间的对立。AVR 内核具有丰厚的指令集和 32 个通用作业寄存器,并且一切的寄存器都直接与算术逻辑单元(ALU)相衔接,使得 1 条指令可以在 1 个时钟周期内一同拜访 2 个独立的寄存器。这种结构大大进步了代码功率,并且具有比一般的 CISC 微操控器最高至 10 倍的数据吞吐率。ATmega64 有如下特色:

① 64 KB 的体系内可编程 Flash(具有一同读写的才能,即 RWW),2 KB 的 EEPROM,4 KB 的 SRAM,32 个通用作业寄存器;

② 53 个通用 I/O 口线;

③ 实时计数器(RTC);

④ 4 个具有比较办法与 PWM 的灵敏的定时器 / 计数器(T/C),具有片内振荡器的可编程看门狗定时器;

⑤ 2 个 USART,面向字节的双线串行接口(TWI),1 个 SPI 串行端口;

⑥ 8 路 10 位具有可选差分输入级可编程增益的 ADC;

⑦ 与 IEEE 1149.1 规范兼容的,可用于拜访片上调试体系及编程的 JTAG 接口。

ATmega64 是以 Atmel 高密度非易失性存储器技能出产的。片内 ISP Flash 答应程序存储器通过 ISP 串行接口(或许通用编程器)进行编程,也可以通过运转于 AVR 内核之中的引导程序进行编程。通过将 8 位 RISC CPU 与体系内可编程的 Flash 集成在一个芯片内,ATmega64 成为一个功用强壮的单片机,为许多嵌入式操控运用供给了灵敏而低本钱的处理方案。

运用 ATmega64 单片机完结对大容量 FPGA 的长途晋级,触及的首要技能问题有三点:一是怎么将 ATmega64 单片机接入 RS485 总线;二是在接纳到晋级数据后和加载 FPGA 时,怎么运用 ATmega64 单片机对大容量的 Flash 存储器进行读写操作;三是 ATmega64 单片机完结 FPGA 的 SELECTMAP 加载。

2.2.1 RS485 接口电路规划

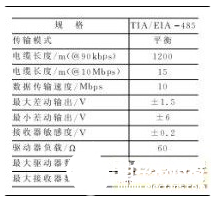

如表 1 所列, RS485 总线规范具有操控便利、价格低廉以及高噪声按捺、相对高的传输速率、传输间隔远和宽共模规模等长处。在曩昔的 20 年时间里,建议性规范 RS485 作为一种多点差分数据传输的电气规范,被运用在许多不同的领域作为数据传输链路。

表 1 TIA/EIA485 串行通讯规范的功用

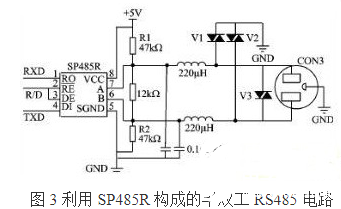

子节点的 ATmega64 单片机通过 Sipex 公司规划出产的高功用 RS485 收发器接入 RS485 总线。

SP485R 是一款与盛行的规范 RS485 芯片彻底兼容,并且包括更高的 ESD 维护和高接纳器输入阻抗等功用的 RS485 收发器。接纳器输入高阻抗可以使 400 个收发器接到同一条传输线上,又不会引起 RS485 驱动器信号的衰减。该收发器的特色如下:

① 答应超越 400 个收发器接到同一条传输线上;

② 接纳器输入高阻抗(规范值 RIN=150 kΩ);

③ 半双工装备与工业规范引脚共同;

④ 共模输入电压规模为 -7~+12 V;

⑤ 低功耗(250 mW);

⑥ 独立驱动器和接纳器使能引脚。

其典型运用电路如图 3 所示。

ATmega64 单片机的规范串行口通过 RXD 直接衔接 SP485R 芯片的 RO 引脚,通过 TXD 直接衔接 SP485R 芯片的 DI 引脚。由单片机输出的 R/D 信号直接操控 SP485R 芯片的发送器 / 接纳器使能:R/D 信号为 1,SP485R 芯片的发送器有用,接纳器制止,此刻单片机可以向 RS485 总线发送数据字节;R/D 信号为 0,SP485R 芯片的发送器制止,接纳器有用,单片机可以接纳来自 RS485 总线的数据字节。上拉电阻 R1、下拉电阻 R2 用于确保未衔接总线时的 SP485R 芯片处于闲暇状况,以进步每个 RS485 节点的作业可靠性。6.8 V 的 TVS 管 V1、V2、V3 用来维护 RS485 总线,防止 RS485 总线受外界搅扰时发生的高压损坏 RS485 收发器。

2.2.2 ATmega64 存储空间的扩展

ATmega64 的寻址空间为 64 KB,运用 ATmega64 本身的寻址体系,只能拜访 0x0000~0xFFFF 的地址空间。显着,这关于存储和加载大容量 FPGA 的装备数据是远远不够的。以 Xilinx 公司的 Spartan3 系列 FPGA 为例,其装备数据所需的存储空间如表 2 所列。

表 2 Spartan3 系列 FPGA 装备文件巨细

以 XC3S4000 型 FPGA 为例,它的装备文件所需的存储空间约为 1.35 MB,已远远超出了 ATmega64 单片机的寻址空间。因而,为了可以运用 ATmega64 单片机来完结对 FPGA 装备数据的读写,有必要对其寻址空间进行扩展。扩展的硬件衔接框图如图 2 中的单片机与 Flash 的衔接部分所示。

本规划中是运用通用 I/O 来扩展 ATmega64 单片机的寻址空间的。ATmega64 单片机的总寻址空间为 64 KB,但片内 4 KB 的 SRAM 及各种寄存器占用了前面的部分寻址空间,故其片外存储器寻址空间是 0x1100~0xFFFF。因而将 Flash 的低 15 位地址直接接到 ATmega64 单片机的低 15 位地址总线上,其他 6 位高位地址用单片机的通用 I/O 进行挑选。寻址时单片机的专用地址口只输出 0x8000~0xFFFF 的地址数据,与通用 I/O 输出的地址组合后给出 Flash 的读写地址。

通过以上对 ATmega64 单片机寻址空间的扩展办法,可以完结 ATmega64 单片机对适宜的 Flash 存储器的寻址操作,然后处理了大容量 FPGA 装备数据的存储和读取问题。

2.2.3 用 ATmega64 完结 FPGA 的 SELECTMAP 加载

Xilinx 公司的 Spartan3 系列 FPGA 加载办法分为 5 种: Master Serial、Slave Serial、Master Parallel、Slave Parallel、JTAG。

依照 FPGA 是否操控加载进程,加载办法可分为 Master 办法和 Slave 办法;依照加载数据时的数据位宽,可分为 Serial 办法和 Parallel 办法。用于加载的引脚首要有: PROG_B,CCLK,RDWR_B,DONE,INIT_B,CS_B,BUSY,D[0~7],M[0~2],HSWAP 和 JTAG 接口(TDI、 TMS、TCK、TDO)。加载进程大体分为 3 个进程:装备的树立、装备数据的加载和加载完结。

SELECTMAP 即 Slave Parallel 办法,是由外部操控器操控 FPGA 的加载进程,并以 8 位数据的办法向 FPGA 写入加载数据的加载办法。图 2 中 FPGA 与 ATmega64 的衔接部分为 ATmega64 单片机选用 SELECTMAP 办法对 FPGA 进行加载的硬件衔接框图,详细完结进程如下:

ATmega64 通过将 FPGA 的 PROG_B、CS_B 和 RDWR_B 引脚置低来敞开加载进程,FPGA 在 PROG_B 置低后开端铲除内部装备 RAM,并将 INIT_B 脚置低。PROG_B 从头置 1 后,在 INIT_B 由低变高的上升沿,FPGA 采样 M[0~2]引脚获取装备办法信息。 ATmega64 监督 FPGA 的 INIT_B 脚,当 INIT_B 脚由低变高时,阐明 FPGA 现已完结了内部装备 RAM 的铲除作业,并准备好接纳装备数据。在 ATmega64 给出的 CCLK 装备时钟的上升沿,装备数据 D[0~7]写入装备 RAM。当 FPGA 接纳完一切的装备数据后,DONE 引脚被 FPGA 置为高电平。ATmega64 可以通过监督 DONE 引脚来判别 FPGA 是否加载完结。关于 Spartan3 系列的 FPGA,假如装备 FPGA 的 CCLK 的频率高于 50 MHz,则外部操控器还需求监督 FPGA 的 BUSY 引脚。当 BUSY 脚为高时,阐明 FPGA 还未完结上一个装备数据的处理,此刻外部操控器需求持续坚持上一个装备数据在 D[0~7]引脚,直至 BUSY 引脚回到低电平。关于本规划的运用,ATmega64 给出的装备时钟频率远低于 50 MHz,不用考虑 BUSY 引脚的操控效果。

3 软件规划

3.1 主控计算机的软件规划

主操控计算机的软件运转状况应该分为两种:一是平常的查询操控状况,用来查询和操控体系中各个节点的作业状况;二是体系的晋级状况,用来履行对各个子节点的晋级操控。如图 4 所示,这两种状况是可以彼此转化的。

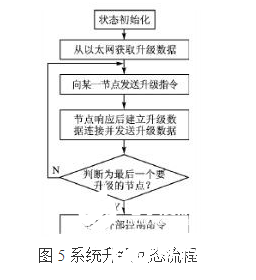

软件的查询操控状况,是由体系所要完结的首要功用决议的,不属于本文所评论的领域。在体系的晋级状况,主控计算机先要通过以太网取得体系各个节点的长途晋级数据,待悉数晋级数据接纳完结后,向体系的一个节点发送晋级指令。节点呼应并树立起通讯衔接后,将该节点的晋级数据悉数发送到该节点。接下来,主控计算机判别上一个节点是否为最终一个需求晋级的节点,假如不是,则持续进行下一个节点晋级数据的传输。体系一切的节点晋级完结后,等候外部输入的操控指令。例如,让整个体系从头启动,加载新的数据;或暂时不从头启动而回来查询操控状况。软件流程如图 5 所示。

3.2 子节点的软件规划

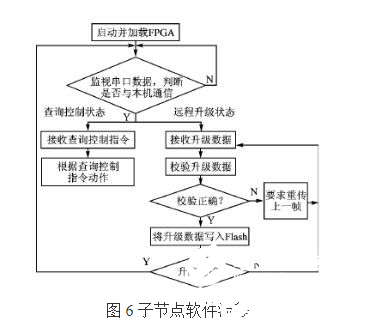

关于子节点的软件规划,与主控计算机相同,也分为平常的查询操控状况和体系晋级状况,并且它们之间也可以与主控计算机一同彼此转化;但 ATmega64 单片机还要承当对 FPGA 的加载使命。开机运转后,ATmega64 单片机先加载子节点 FPGA,使子节点可以正常作业。子节点正常作业后,监督 RS485 总线并判别有无对本节点的通讯。当主控计算机要求与本节点树立通讯衔接时,发送反应信息,与其树立通讯衔接。子节点依据主控计算机发送的指令,进入查询操控办法或许长途晋级办法。进入长途晋级办法后,子节点接纳主控计算机发来的长途晋级数据,晋级数据通过校验后写入 Flash。晋级完结后持续等候主控计算机的指令,从头启动或持续运转。其详细的软件规划流程如图 6 所示。

结语

FPGA 既承继了 ASIC 的大规模、高集成度、高可靠性的长处,又克服了一般 ASIC 周期长、出资大、灵敏性差的缺陷,逐渐成为许多体系完结的抱负挑选。特别是跟着 FPGA 容量和功用的提高,加上其共同的硬件晋级才能,其运用规模越来越广。本文所提出的对大容量 FPGA 构成的多节点体系的长途晋级办法,体系构成简略、技能老练,并且具有显着的本钱优势。