这儿咱们运用一个波形发生器作为比如,来阐明怎么运用Modelsim对Quartus II生成的IP Core和相应的HDL文件进行功用仿真和时序仿真。这个比如里边运用到了由Quartus II生成的一个片上ROM存储单元。这种存储单元和RAM相同,都是根本的FPGA片上存储单元,在今后的规划里边会常常运用到。

功用仿真

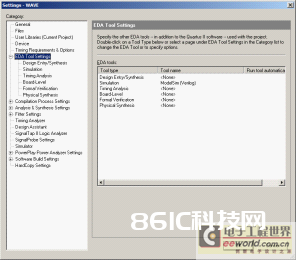

(1)在Quartus II中设置第三方仿真东西,挑选“Assignments-Settings-EDA Tool Settings-Simulation”,挑选“ModelSim-Verilog”。如图1所示。

图1 EDA东西设置

(2)编译工程。编译带有IP Core的工程文件。

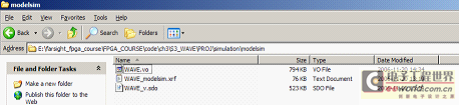

(3)编译完成后会在工程目录下生成“simulation-modelsim”的目录,如图2所示。其间包括了3个文件:“.vo”是仿真网表文件,能够用来替代规划文件;“.xrf”是Quartus编译生成的信息文件;“.sdo”是工程延时信息。

图2 编译生成文件(4)参加仿真库文件。

仿真库的途径为“C:\altera\quartus50\eda\sim_lib”,包括了如下3个仿真库文件。

· 220model.v:带有用户原语类型的Quartus自带的IP核的库文件。

· altera_mf.v:Quartus自带的IP核的库文件。

· cyclone_atoms.v:相应系列的器材库。

在本例中需求增加altera_mf.v,cyclone_atoms.v两个库文件。

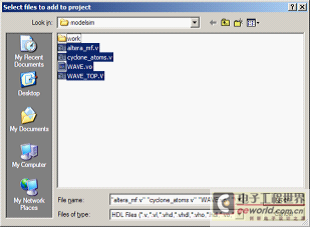

(5)将测验文件粘贴到方才生成的目录中,如图3所示。

图3 增加测验文件

(7)翻开modelsim。

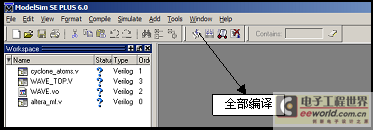

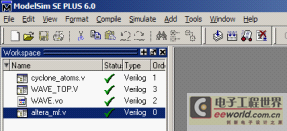

(8)创立工程并增加源文件,如图4所示。

图4 为工程增加源文件(9)编译工程。结合库文件一同进行编译、如图5和6所示。

图6 悉数编译后

(10)修正wave.vo文件。将文件中的延时信息注释掉,即:

//initial $sdf_annotate(“WAVE_v.sdo”);

(11)从头编译wave.vo文件。

时序仿真

(1)将功用仿真第(10)步中对wave.vo文件做的注释改回来,从头进行编译。

(2)从头翻开开端仿真对话框,挑选顶层模块。

(3)挑选“SDF”选项卡。

(4)参加“.sdo”文件,将两个SDF Options都选中。

(5)和功用仿真相同,为波形窗口增加信号,开端进行仿真。

(6)经过波形图,检查时序仿真的延时。