1导言

射频辨认技能(RFID)是使用射频方法进行远间隔通讯以到达物品辨认意图,可用来追寻和办理简直一切物理方针。在工业自动化、商业自动化、交通运输操控办理、防伪等很多范畴,乃至军事用处都具有广泛的使用远景,并且引起了广泛的重视。RFID体系一般包含读写器和电子标签(或称应对器)2个部分。RFID电子标签(Tag)由芯片与天线(Antenna)组成,每个标签具有专一的电子编码。标签附在物体上以标识方针方针。RFID读写器(Reader)的首要任务是操控射频模块向标签发射读写信号,并接纳标签的应对。对标签信息进行解码,并将信息传输到主机以供处理。依据使用的不同,阅读器可所以手持式或固定式。本文要点介绍的便是读写器的开发。

EPC标准现已公布第一代标准。标准把标签细分为Class0,Class1,Class2三种。其间Class0和Class1标签都是一次写入屡次读取标签,Class0标签只能由厂商写入信息,用户无法修正,因而又称为只读标签,首要用于供应链办理)Class1则供给了更多的灵活性,信息可由用户写入一次。Class0和Class1标签选用不同的空中接口标准进行通讯,因而两类标签不能互操作。Class2标签具有屡次写入才能,并增加了部分存储空间用于存储用户的附加数据。Class2标签答应参加安全与拜访操控、感知网络和AdHoc网络等功用支撑。现在EPCglobal正在拟定第二代标签标准,即UHFClasslGeneraTIon2(C1G2)。C1G2具有随时更新标签内容的才能,确保标签一直保存最新信息。EPC标准l_0版别包含EPCTag数据标准、Class0(900MHz)标签标准、C1ass1(13.56MHz)标签接口标准、Classl(860~930MHz)标签射频与逻辑通讯接口标准、物理标识言语(PhysicalMarkupLanguage,PML)。

本文要点介绍EPCClass1读写器体系规划、数字部分规划及FPGA在数字完结上的使用。因为U频段RFID技能的使用还处在前期的发展阶段,契合EPCClass1协议的读写器在国内还没有相关产品问世。本文对相关开发有必定的参考价值。

2EPCClasslb体系规划

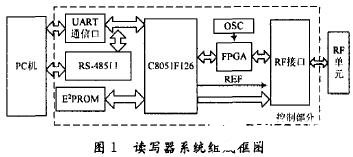

一个完好的RFID体系包含:读写器、天线、标签和PC机。读写器完结对标签(Tag)的读写操作。经过RS232或RS485总线完结PC机的指令接纳和EPC卡号的上传。图l是读写器的体系组成框图。读写器组成包含与PC机的串口通讯部分、单片机和FPGA组成的数字部分、射频部分。RF单元完结和标签的通讯,数字部分完结对射频部分的操控、回波指令解析PC机接纳卡号完结上位机的操控。下面临各模块做简略介绍。

2.1PC端

RFID体系一般要将标签信息读取到计算机上,然后等候处理用户经过PC机能够完结读写器操控,完结对标签的读写操作。读写器与PC机通讯是依据RS232总线,纠错算法是CRC—CCITT算法。

2.2射频模块

读写器对标签的读写是经过发送射频能量和对回波完结的。射频模一方面将数字模块送来的信息完结调制并发送。标签应对,射频模块接纳回波信号将他解调成基带信号,送到数字模块。

2.3数字模块

数字模块由单片机(cygnalC8O51F126)、存储器(24Cz56),FPGA(xlSlOO)组成单片机的功用有:

(1)完结与PC机通讯,接纳PC机指令,完结解析下传到FPGA

(2)将FPGA送来的EPC卡号加算CRC—CCITT校验上传PC机。择Xilinx公司ISE6.2,仿真软件为Modelsim5.7。规划完结采纳原理图和VHDL言语相结合的准则。顶层模块选用原理图规划,功用模块选用VHDL言语完结。

(3)处理多卡磕碰,完结多卡读取。因为FPGA完结多卡读取算法十分耗费FPGA资源,并且需求FPGA有很多的存储器资源寄存读到的卡号,本钱较高。而假如由PC机完结多卡读取算法,则读取速度很难进步。

(4)完结对射频模块的锁相环频率操控以及功率操控读写器发射功率常需求调整,并且读写器有时需求在不同射频频率,乃至跳频下作业。单片机经过对射频模块的锁相环操控完结对射频频率和功率的操控。

单片机选用CYGNAL公司的C8051F126。内部有128k的FLASH存储器和8k的RAM,能够在5OMHz主频下作业。

FPGA完结EPCClassl通讯协议,接纳单片机操控指令,将指令依照协议标准编码送到射频模块调制并发送,然后解调并接纳射频模块送来的回波基带信号,将得到的标签信息发送给单片机。FPGA完结的EPCClassl指令的根本指令包含scrollid,scrollallid,pinged,quiet,talk,kill;编程指令programid,verifyid,lockid,eraseid这些指令包含指令的发送和回波的解析。依据发送指令不同,对应的发送指令格局也不相同,分为2类。回波信号格局也依据指令的不同分为2类。下面介绍FPGA完结的EPCClass1协议。

3FPGA完结的信号调制解调

3.1FPGA器材及开发渠道

FPGA挑选Xilinx公司的SPARTIIXC2S100规划为1O万门,体系时钟挑选40MHz,满足要求。开发软件挑选Xilinx公司ISE6.2,仿真软件为Modelsim5.7。规划完结采纳原理图和VHDL言语相结合的准则。顶层模块选用原理图规划,功用模块选用VHDL言语完结

3.2结构框图

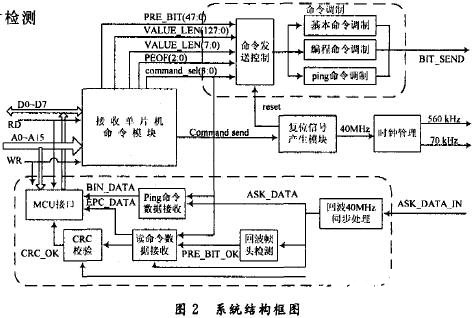

从体系的结构图能够看出FPGA完结的调制解调部分包含:单片机接口(单片机的指令接纳模块、向单片机发送数据模块)、复位信号发生模块、指令调制模块、指令接纳模块。

单片机向FPGA发送数据选用对地址操作方法,单片机对FPGA读取数据选用查询方法。FPGA整个作业进程:FPGA接纳单片机操控指令,接纳单片机指令模块将所收到的指令赋值给相应寄存器,一起复位信号发生模块依据单片机发送的指令发生复位信号(单片机写FPGA进程即为复位)。指令调制模块依据单片机送来的指令以及相应操控字,输出相应的调制信号(bit—sent)输出到射频模块。接纳模块一直在检测回波数据,当检测到回波数据的帧头有用时告诉读指令数据接纳模块接纳数据。一起将接纳到的数据送CRC校验模块校验,数据接纳完结,CRC校验也即完结,CRC校验模块校验成功即发生CRCOK=l表明读卡号成功,单片机查询到此位为高时经过MCU接口模块读卡号和CRC。在Ping指令时,Ping指令接纳模块判别指令发送模块此刻发送的指令类型。假如为Ping指令时,则接纳数据,将接纳的各槽数据及状况信息放在BINDATA寄存器中。

3.3要害功用模块

(1)指令调制模块

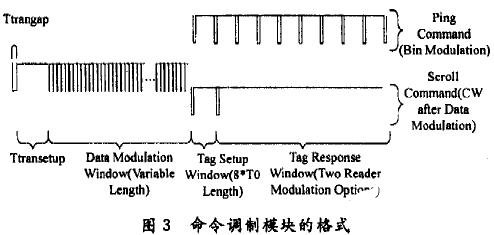

指令调制模块发送的指令有必要契合EPC标准对信息编码要求以及指令格局要求。信息编码占空比为1/8时钟表明“0”,占空比为3/8时钟表明“l”。指令格局要求如图3所示,依据EPC标准,能够将指令格局分为3种,分别为ping指令格局、写卡(program)指令格局、读卡(scrolled)指令格局,详细指令格局参照文献。指令调制模块完结3种指令格局的调制。指令调制模块规划采

(2)Ping指令接纳模块

回波编码和发送编码方法不同,Ping指令和scrollid指令回波编码用“1010”表明l,用“l100”表明0。接纳数据模块有必要将回波调制信号解调成~0,1信号。Ping指令是根本多卡操作指令。如图3所示,Ping指令的标签应对是在8个槽(bin)中应对,对应着不同的8组标签。这样一次Ping指令能够判别8组标签。进步了多卡功率.每一个槽(bin)信息用2个寄存器表明,BIN0(1:O)表明卡的状况信息:有卡、无卡、多卡。BIN(7:O)表明槽的数据。单片机依据槽状况信息决议是否读取槽数据.

(3)scollid指令数据接纳模块

scrollid以及scrollallid,verifyid指令的回波格局相同,接纳方法相同.回波格局如图4所示

一帧完好回波包含帧头(F7H),16位CRC,96位或64位EPCDATA。接纳模块选用检测帧头的方法,经过一个32位移位寄存器(1b数据由4个状况信息表明)检测帧头,帧头有用则读数据模块解调回波数据,解调数据存储在EPCDATA寄存器中。一起将检测到的bits送到CRC校验。

(4)CRC校验模块

CRC模块对数据接纳模块检测到的数据依照CRC—CCITT算法校验,校验经过则发生CRCOK=”1”。单片机依据此状况读取EPCDATA。CRC—CCITT算法完结选用串行方法。程序十分简略,并且节约FPGA资源。

节选代码如下:

xOr_flag_en:process(elk)begin

ifelk==‘0’andelkeventthen

ifen==’l’then

ifcrc_bur(15)==‘1’then

crcbur《=(crcbur(14downtoO)&data_in)

xor”OOO1OOOOOO1OOOO1”:

xor_flag《=‘l’

elseerc_buf《=crc_buf(14downtoO)&data_in:

xor_flag《=‘0’;

endif;

elsecrc_buf《=”111ll111111llll1”;

endif;

endif;

endprOcess

4结语

FPGA完结了对EPCClassl96位和64位卡的读写操作指令,读写成功率十分高,能完结8m间隔的正常读,多卡读取速度快。读写器和标签的读写速率为上行70kb/s,下行140kb/s。此读写器也现已在批量生产,投放市场。

在读写器规划进程中仍有几方面问题需求进一步改进。一是Ping指令回波没有CRC校验,所以Ping指令的回波检测成功率不行高,影响多卡速度;另一方面,当回波信号信噪比不高时,接纳成功率下降速度很快。一起,在读写器规划进程中发现EPC标签的一些问题。其间杰出的是,调试发现96位标签在应对时存在累积周期差,不能和读写器的时钟同步。标签锁相环不行精确,给读写器的规划带来不小难度.

责任编辑:gt