文章转自ADI官网,版权归属原作者一切

本文是两篇系列文章的第2部分。 第1部分 介绍了在电机操控运用中,运用sinc滤波器对∑-∆编码数据进行解调。尽管文中阐明晰同步sinc滤波器的脉冲响应对脉冲宽度调制(PWM)的重要性,并提出了同步战略,可是,同步计划会导致难以正确装备体系。

作为本系列的第2部分,本文提出一种针对同步优化的新式sinc滤波器结构。该滤波器可在需求严厉操控反应链时序的运用中进步丈量功用。接着,第2部分还将评论选用HDL代码完成sinc滤波器的办法,以及如安在FPGA完成上优化滤波器。最终,给出在一个根据FPGA的3相伺服驱动器上履行的丈量成果。

针对同步优化的sinc滤波器

如第1部分所述,经过正确对齐sinc滤波器对PWM的脉冲响应,能够完成无混叠的∑-∆丈量。尽管该办法很简单,可是很难(在许多状况下不或许)找到一个抱负的体系装备。为了阐明这一点,假定sinc滤波器和PWM模块共用同一个以 fsys运转的体系时钟源。调制器时钟 fmclk则由公式1确认。

其间 Dmclk 是调制器时钟的时钟分频数。相同,PWM频率 fpwm由公式2确认。

其间 DPWM 是确认PWM频率的时钟分频数。最终,sinc滤波器的抽取率(数据速率)由公式3确认。

其间 Ddec 是抽取后时钟的时钟分频数。为了防止脉冲响应和PWM周期之间的漂移,一个PWM周期内包含的抽取周期数量有必要为整数:

其间N为整数。兼并公式2、公式3和公式4可得:

明显,只要有限挑选的时钟缩放份额 Dx可满意公式5。此外,时钟缩放份额的挑选办法往往也遭到严厉约束。例如,体系或许需求以必定的PWM频率(例如10 kHz)运转或运用必定的调制器时钟(例如20 MHz)。另一个费事是进行调制器时钟挑选时,可选数值有限。例如,假如 fsys 为100 MHz,则 Dmclk仅有的合理挑选应为5到10之间有限范围内的整数(从20 MHz低至10 MHz)。

考虑到一切这些约束,很难(即使有或许)找到可在脉冲响应和PWM之间完成所需对齐的时钟缩放份额。通常会发作的状况是,用户被逼挑选满意公式5的时钟缩放份额,而非挑选可发生所需PWM频率、调制器时钟和信噪比(SNR)的时钟缩放份额。并且,假如其间一个频率随时刻发作变化,则无法找到有用的装备。这种状况在多轴体系中十分遍及,在这些体系中,单个运动操控器会对网络中的多个电机操控器进行同步。

尽管对齐计划可提供超卓的丈量功用,但事实证明它不切实际。以下章节将介绍一种新式sinc滤波器。该滤波器可提供超卓的丈量功用,一起答应用户独立挑选一切时钟分频数。

刷新式sinc滤波器

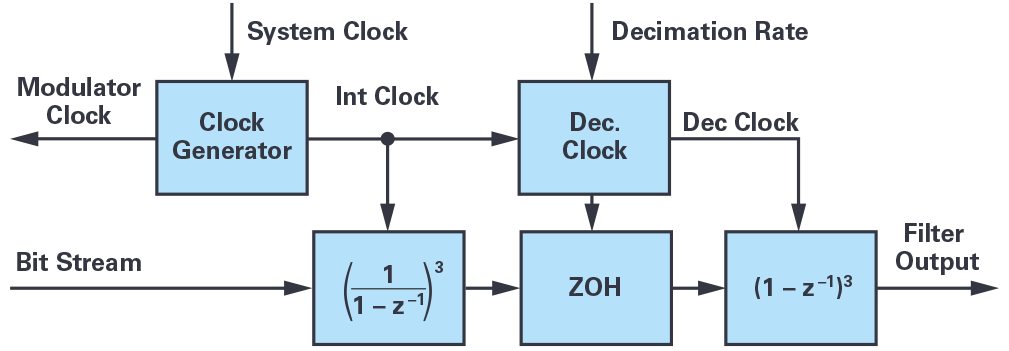

传统的三阶sinc滤波器如图1所示。滤波器经过按份额缩放体系时钟来生成ADC的调制器时钟,而ADC则向滤波器回来一个1位数据流。滤波器功用自身包含三阶级联积分器 1/(1 – z–1)(时钟速率与调制器速率相同)和三阶级联微分器 1 – z–1(时钟速率为抽取时钟)。