体系时钟优化能够进步体系的功能,但也颇具挑战性。为模数转化器规划颤动为350飞秒(fs)的编码电路是相对简单的,但这是否能够满意当今的高速需求?例如,测验AD9446-100(16 bit 100 MHz ADC)时,在Nyquist区运用100 MHz的采样时钟频率,350 fs的颤动将使信噪比(SNR)下降约3 dB。假如在第三Nyquist域中运用105 MHz的模仿输入信号测验相同的设备,SNR下降可达10 dB。为了将时钟颤动削减到100 fs或更少,规划者需求了解时钟颤动来自哪里,以及ADC能够答应多大的颤动。假如在电路规划完成后才发现时钟电路功能受颤动的约束,而且在规划阶段中本能够很简单地防止该问题发生,这时现已太晚了。

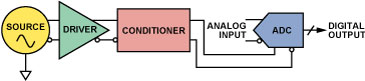

在这里咱们将评论相关的时钟参数和办法以完成高速转化器预期的功能,为此要用到一些技能窍门和经历。首先从典型的ADC时钟计划开端,如图1中所示,咱们将焦点放在信号链路中每一级的可用于优化时钟的技能,而且指明一些应防止运用的常用技能。

图1. 典型的时钟信号链路

什么是颤动?

颤动是体系时钟电路规划中最重要的参数,因而了解某些基础知识而且了解术语的意义是十分重要的。许多技能文献描绘了关于颤动的十分准确的数学模型,可是规划功能优秀的转化器并非悉数取决于准确的颤动描绘。规划人员有必要了解颤动怎么进入体系以及怎么使颤动的影响最小。

颤动是时钟边缘的方位改变,这将发生守时差错,直接导致转化起伏精度的差错(图2a)。模仿输入频率的添加导致输入信号的斜率添加,这将使转化差错扩大(图 2b)。应当留意,转化差错的衡量是相对的,10 bit器材0.5 LSB(最低有用位)的转化差错等效于16 bit器材32 LSB的差错。这意味着跟着ADC分辨率和模仿输入频率的添加,颤动变得愈加引人留意。

图2. 转化差错是时钟颤动和模仿输入频率的函数

直观上看,它们之间的联系是十分显着的,因而工程师能够经过剖析ADC功能和编码时钟颤动之间的联系,终究确认可接受的颤动量。式1界说了抱负ADC(具有无穷大分辨率)SNR(dB)与频率的联系,而式2界说了N(10、12、14或16)bit抱负ADC的SNR(dB)。

![]()

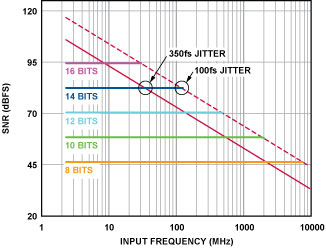

参看图3的斜线 (1)

![]()

参看图3的水平线 (2)

图3是由这两个公式画出的曲线图。用户能够在曲线交点处确认给定模仿输入信号频率时可容忍的总时钟颤动量。在低频下,精度遭到转化器分辨率的约束。但是,跟着输入信号频率的添加,在大于某个频点之后,ADC的功能将受控于体系的总时钟颤动。坐落该频点左边的输入信号频率,无须考虑小颤动的问题。

图3. 抱负ADC的SNR vs. 模仿输入信号频率和颤动

但是,假如信号频率在该频点邻近或许在其右侧,则有必要下降频率或分辨率,或许有必要进步颤动目标。因而,颤动越大,SNR功能受控于时钟体系颤动的频点就越低。

例如,假如运用具有350 fs颤动的时钟测验14 bit ADC,为了防止功能下降,输入信号频率有必要低于35 MHz(14 bit水平线与350 fs斜线的交点)。假如颤动为100 fs,则输入信号频率能够到达125 MHz。

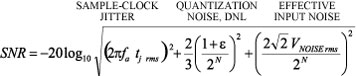

实际上,当模仿测验频率挨近交点时,运用该一阶近似的简化模型便丧失了有用性。为了全面地了解时钟颤动对ADC功能的影响,除了分辨率以外,还要考虑量化噪声和模仿输入起伏(式3,根据参阅文献9)。

(3)

(3)

其间

SNR = 信噪比(dB)

fa = 满量程正弦波的模仿输入频率

tj rms = 内部ADC颤动和外部时钟颤动的组合rms颤动

ε = ADC的平均差分非线性(DNL)(LSB)

N = ADC的分辨率(bit)

VNOISE rms = ADC的有用输入噪声

假如 tj rms = 0, ε = 0, 而且 VNOISE rms = 0, 则上面的公式变为咱们所了解的

SNR = 6.02N + 1.76dB

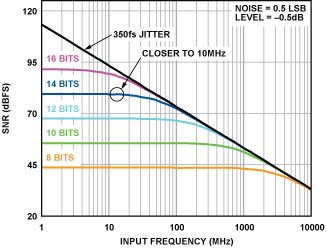

例如,假定ADC具有0.5 LSB的量化噪声,而且在测验时模仿输入起伏比满刻度低0.5 dB。图4结合了式2和式3,比较于简化模型,编码时钟颤动将在更低的频率处影响SNR功能。

图4. SNR是模仿输入频率、时钟颤动和量化噪声的函数

前面的示例中,模仿输入信号频率挨近35 MHz时,具有350 fs颤动的时钟不会影响14 bit ADC的SNR。可是在考虑量化噪声、输入信号频率和输入起伏的影响后,10 MHz的信号频率就应被留意。同样地,颤动为100 fs的时钟会在低于100 MHz的频率下引起SNR的下降。

消除颤动

在回忆有关颤动的基础知识之后,咱们将考虑颤动的源。能够使得ADC时钟沿改换的任何要素都将引进或影响颤动。这些要素包含串扰、EMI(电磁搅扰)、地效应和电源噪声。

串扰引起的颤动能够呈现在恣意两条相邻的走线上。假如一条走线承载信号,而邻近的平行走线承载改变的电流,则信号走线中会感生电压。假如该信号是时钟信号,则时钟边缘发生点的时刻将发生改变。

EMI辐射引发灵敏信号走线上的颤动。EMI由开关电源、高压输电线、RF信号和其他相似的源发生。与串扰相似,EMI经过电磁耦合调整了信号或时钟的时序。

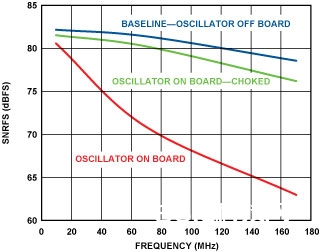

图5说明晰电磁搅扰对SNR的影响。蓝色曲线表明AD9446基线SNR vs. 频率的联系,其间AD9446运用外部时钟和线性电源。时钟未以任何方法连接到评价板。赤色曲线给出了将相同的时钟电路固定或焊接到评价板后呈现的功能下降,其间时钟电路由开关电源供电。绿色曲线给出了,假如对电源噪声进行滤波,则能够明显改善转化器的功能。

图5. 转化器功能 vs. 振荡器电源装备和频率

由开关电流或许不恰当的接地引起的地弹也或许带来颤动。当许多门电路一起切换时,开关电流会变大。这或许在电源平面和地平面上发生电流尖峰,使时钟电路的阈值电压或模仿输入信号的电平移位。例如:

考虑PCB走线和接纳门电路的输入端,门电路输出会具有10 pF的负载。当门电路切换时,10 mA的动态电流流入或流出每个输出端。[10 mA得自10 pF×1 V/ns,即CMOS门电路的典型摆率(I=C dV/dt)。] 因而,假如12个门电路一起切换,则动态电流或许累积到达120 mA。这将需求电源引脚供给很大的电流尖峰,而其间一个引脚是接地的。由引线电阻引起的瞬时压降(跳动)将影响一切以该引线作为参阅地的电路。

为了削减这些源引起的颤动,应运用杰出的布线和恰当的电路布局。重要的一点是将模仿电路和数字电路约束在其各自的区域中。为保证杰出的阻隔,每个电路层都应遵从该准则。了解回流怎么相关于源来活动以及怎么防止模仿和数字电路之间的越界或穿插是十分重要的。总而言之,有必要使灵敏的模仿输入和时钟走线远离其他电路和走线,避免遭到这些电路和走线的影响。

改善颤动意味着改善摆率

前面已评论了颤动的基础知识及其或许带来的影响,现在的问题是:怎么改善体系时钟或时钟电路以削减颤动?

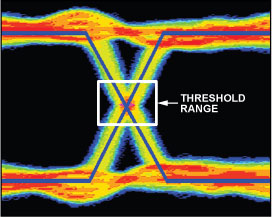

回忆之前的评论,当颤动呈现在转化进程或许时钟的阈值周期中时,颤动或噪声仅能损坏ADC的时序,如图6中所示。经过添加摆率使该边缘(而且因而使阈值周期)更快,将会使阈值周期中或许呈现噪声的时刻量变小,并使引进体系中的rms(均方根)颤动量变小。

图6. 差分时钟的阈值/转化区域的扩大示图

应当留意,摆率的添加不会影响原始信号质量,仅会影响经过阈值区域的转化时刻。为了证明这一点,参阅图2b。应当留意,信号摇摆越快,在转化区域中花费的时刻就越少。图7说明晰颤动和摆率之间成反比。与前面的示例结合考虑,关于12 bit ADC,输入信号为70 MHz时颤动最少为100 fs rms,对应摆率为1V/ns。