丈量范畴以及仪表仪器范畴中,对数字信号的丈量首要就是对其信号脉冲宽度进行丈量。现在运用最多的办法就是脉冲计数的办法,即经过高频时钟脉冲在待测信号的低电平处或许高电平处进行计数,然后按照脉冲数量,经过核算的办法得到信号宽度,待测信号独立于计数时钟,其信号的上升以及下降沿无法一起钟边缘精确的符合,所以,该办法得到的差错最大值可以到达一个时钟周期。例如,若是高频时钟为80MHz,那么其最大的差错量可以到达12.5ns。

脉冲计数法的精度也可以经过有用的办法予以进步,其思路如下:首要可以将计数时钟的频率予以进步,其次则是经过期幅转化技能对差错予以下降。丈量差错会跟着时钟频率的的进步而减小,可是频率进步,相对便会对芯片的要求有所进步。例如,若丈量差错要求为1ns 时,其时钟频率有必要到达1GHz,一般的计数芯片在这种状态下无法正常作业,而且电路板布线以及加工和资料挑选都会成为难题。而运用时幅转化技能就无需对时钟频率有所要求,可是该种办法运用了模仿电路,若是待测频率相对较高,那么丈量成果很简单遭到噪声的搅扰,而且若要求是对信号脉宽进行接连丈量,那么电路能否快速反应是该办法需求处理的一大弊端。

而同上述两种办法都不相同的是,文章论说了一种新式的办法,经过数字移相的办法,对脉宽丈量精度予以进步。该办法选用FPGA 芯片,完结了高精度脉宽丈量。

1.丈量原理

两路同频信号以一路作为参阅,将另一路以该路信号作为参阅,进行滞后或许超前的移动,然后构成相应的相位差,这边是移相。该种丈量办法一般运用延时办法,经过对两数字信号之间发生的相位差以延时长短进行决议,这种丈量原理的根底即数字移相技能。原始计数时钟信号CLK0 经过移相后得到CLK90、CLK180、CLK270。相位之间顺次相差90°,经过这四路时钟信号对四个相同计数器进行一起驱动,然后完结信号计数。

2.体系完结

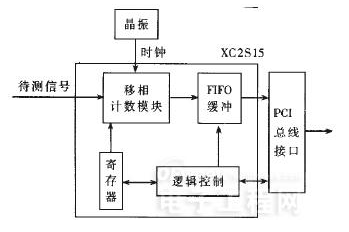

计数时钟之间所具有的相位差是该体系坚持正常运转的根底,原始时钟频率一般所具有的频率一般较高,频率接100MHz,而周期也大于10ns 而小于20ns,所以即就是存在推迟时刻也只是只要几ns;别的,为了防止由于传送推迟而对电路板芯片形成晦气影响,有必要确保体系的柔性以及安稳和精度。文章经过对可编程门阵列,对丈量办法予以完结。经过下图的剖析可以看出,丈量成果终究被送入到FIFO 缓存,然后在处理速度上可以有用得以进步,终究经过PLC总线完结数据的传送。

各个模块之间的时序需求予以和谐操控,而经过逻辑操控则可以有用的得以时刻,并使得体系可以正常运转。而FIFO 缓冲模块是在FPGA 芯片中予以完结,别的,逻辑操控也是在该芯片中予以完结的。

artanII 系列相对于其他的FPGA 芯片性价比相对较高。而且运转频率最高罢了到达200MHz,这儿芯片选用的是XC2S15-6 以此确保时钟信号不会呈现一直外协以及延时传送;而且在时钟信号的操控上也相对较为便利,例如时钟信号的分频以及倍频和移相。别的经过DLL 功用可以完结移相计数模块的快速构建,然后完结上述文章中介绍的几种丈量办法。经过DLL 处理后的原始时钟可以得到相差为90°的四组相位,即SLD0、CLK90以及CLK180和CLK270,最终核算出信号脉宽值。

3.仿真剖析以及精度剖析

经过给出内部的布线,完结芯片的政策成果,其仿真成果用Modelsim完结。在RESET 后对计数模块进行发动,继而开端丈量待测信号,丈量后会发生READY 信号,一起将丈量后的成果输出,为后续的丈量核算以及剖析供给根底信息,经过仿真试验可以证明体系可以到达方针要求。

然后进一步对体系进行差错剖析,体系丈量脉宽丈量会呈现差错的原因首要是由于体系原理差错TS、时钟相移差错Tp 和信号推迟差错Td 以及计数时钟抖晃Tc 等多项差错的存在。经过上面的剖析可以看出,若时钟输入过程中晶振为80MHz 时,得出的差错量为3.125ns。时钟相移差错是四路相位-偏移发生的信号自身,该信号从SLKDLL 中别离,按照芯片参数,最大的相移差错可以到达200ps。

经过剖析核算可以得出成果:别离可以得到计数时钟到各自计数器的推迟时刻,操控计数器发动中止的HF 信号到四个计数器的时刻。由于需求的是各计数时钟间相对推迟时刻,故还能得到时钟相对于HF信号到计数器的推迟。

数字移相技能是现在咱们应用在脉宽丈量上的根底,在此根底上文章提出了一种精度更高的丈量体系,这种办法不同于脉冲计数的办法,在精度上更是高出脉冲计数数倍。而该种办法的丈量精度还可以持续予以进步,首要可以经过以下两方面予以完善:首要将晶振频率持续进步,将FPGA 芯片的速度进步的更快。着也是由于体系原理差错会遭到晶振频率的影响,晶振频率越高,其差错值就会越小。其次,是对信号推迟差错予以下降。经过前面的剖析可以看出,体系精度会遭到信号推迟差错的影响。经过削减计数器以及技能时钟的信号推迟差异,可以将丈量精度有用进步。别的在FPGA芯片中,信号推迟的时刻可以便利的得到,所以,规划过程中只需求将内部元件的方位以及连线予以调整便可以对推迟差错进行调整,或许经过添加一些门电路,然后令信号推迟时刻坚持一致。