1、导言

在FPGA 规划中运用嵌入式处理器软核( 如MicroBlaze、PicoBlaze 等) 构成可编程片上体系( SystemOn Programmable Chip,SOPC) ,比较于ASIC 具有更好的可修正性和可维护性,得到了遍及的运用。因为ARM,MicroBlaze 等大型处理器内核具有调试接口,在与之对应的调试模块合作下,调试软件能够经过JTAG 接口完结: 履行到断点处挂起、单步履行、检查处理器内部状况、检查和修正Memory空间中的数据等根本的在线调试功用。上述根本的在线调试功用对嵌入式体系的调试具有重要意义。

关于PicoBlaze 等占用资源少、规划开发简略的细巧型处理器,一般不具有调试接口,然而在SOPC体系规划中常常需求运用上述处理器。运用上述处理器时,因为没有调试接口,归于大型处理器的规范高效的调试机制不再能够运用,因而经过指令集仿真( ISS,Cycle – accurate Instruction Set SimulaTIon) 和运用仿真东西对含有处理器的体系进行软硬件协同仿真是确保规划正确性的重要途径。然而在比如接纳机基带信号处理等体系的规划中,仿真所用的测验用例往往掩盖率不行,或许在发现毛病今后很难构造出与之相应的测验用例。因而火急需求使在线调试功用能够便利地扩展到一般的处理器上。

针对上述运用需求,这儿提出的新调试办法经过引进一种通用的调试模块( Universal Debug Module,UDM) 能够使没有调试接口的处理器树立起规范的调试机制。该调试模块运用处理器的中止机制完结处理器呼应断点( breakpoint) 的机制,运用依据双端口RAM 中一种奇妙的地址映射机制完结一起对多行代码设置断点的功用,而且能够便利地完结被调试体系和调试主机之间调试信息和指令的交互。UDM 还具有易于扩展的长处,当SOPC 体系中有多个处理器时能够共用一个UDM。

2 、在线调试的一般原理

嵌入式处理器的干流在线调试办法,现在首要有2 种: 后台调试形式( backgroud debug mode,BDM) 技能和依据IEEE P1149. 1 协议的JTAG 调试技能。BDM 技能在Motolora 微操控器中得到了许多的运用,ARM,MIPS 和PowerPC 等处理器都具有依据JTAG 技能的在片调试功用,如ARM 公司提出了依据JTAG 技能的RDI 调试接口规范,首要用于ARM 芯片的调试。处理器内核中经过添加支撑调试的扩展规划,可在预留的调试接口输入简略的操控信号,以完结: 处理器挂起( Halt) 、输出PC 值和通用寄存器值、输出和修正Memory 空间中的数据等根本的原始调试操作。一般上述调试接口的规划与指令集架构相关,如MIPS32 供给如下一些调试办法: ①断点指令BREAK; ②一些自陷指令TRAP; ③特别操控寄存器WATCH,经过编程使得特定的load /store 操作以及取指操作发生特别的破例;④一种依据TLB 的MMU,经过编程使得拜访恣意存储器页都能够发生特定的破例。

关于没有调试接口的处理器现在首要是经过在软件和硬件规划中充分考虑或许的调试需求,再加上调试主机和被调试体系之间的通讯机制来完结在线调试的。这种调试形式下,调试代码需求刺进到正常程序中,将调试信息输出到调试主机,一起还能够接纳调试主机发过来的指令做出各种呼应。该办法的首要缺点是针对不同的调试需求,要不断修正正常程序中的调试代码,导致规范化和通用性程度不高。此处的UDM 在不对处理器内核做修正的状况下即可使这类处理器树立起便利的调试机制,是一种不同于干流大型处理器完结在线调试的办法。

3 、通用调试模块( UDM) 的作业原理

3. 1 体系描绘

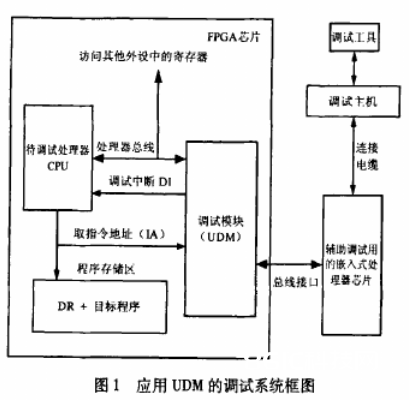

运用UDM 的调试体系框图如图1 所示,运用与FPGA 同在一块PCB 板上的ARM、DSP 等处理器作为辅佐调试用的嵌入式处理器( 下文中简称为辅佐处理器) ,简化了UDM 与调试主机之间的通讯。经过辅佐处理器的总线接口,UDM 中的各种操控和数据寄存器被直接映射到辅佐处理器的Memory 空间。在辅佐处理器开发东西的Memory 窗口直接进行数据读写操作,就可完结对UDM 的操控,如图4、图5 所示。因为在一块PCB 板上一起集成FPGA 和嵌入式处理器芯片是很常见的规划,因而这种通讯办法适用的规模很广。

UDM 直接作为FPGA 外部辅佐调试的嵌入式处理器的外设,如果在外部处理器总线挂接多个UDM 模块,就能完结一起对多个处理器进行调试。

UDM 经过发生调试中止( DeBug Interrupt,DI) 信号,使处理器呼应中止并调用调试服务程序( DebugRouTIne,DR) 。UDM 经过监测处理器的取指令地址( InstrucTIon Address, IA) 发生DI 信号。PicoBlaze 在运转DR 时可经过其总线接口拜访UDM,然后完结调试信息的输出和对调试指令的呼应。

3. 2 断点设置机制

发生DI 时因为处理器会当即履行DR,然后中止正常的履行流程转为为调试服务,因而决议DI 发生的机遇是完结断点机制的中心。DI 信号是经过监测处理器的取指令地址( InstrucTIon Address, IA)发生的。直接经过一个比较器将IA 与一个数据比较一次只能设置一个断点,为了处理此对立选用了如下办法: 在UDM 顶用双口RAM 存储断点装备信息,使RAM 中的每1bit 与程序存储区的一个地址对应起来,数据为1 代表设置了断点,0 代表没有。

将输入的IA 进行地址改换后对RAM 存储区寻址,使得RAM 在一端输出一个正好代表输出的地址处是否设置了断点信息,再依据此数据就可生成正确的DI 信号。在双口RAM 的别的一端,断点设置状况能够便利地被修正。这样一来能够设置的断点个数变为首要受UDM 中双口RAM 容量约束了。

3. 3 调试服务程序

只需在DR 中确保处理器不对方针程序的内外部环境形成改动,就等效于完结了处理器的挂起功用。因而,需求将DR 和方针程序的履行环境阻隔开来,这能够经过对编译器进行某些设置或强制的编码规范来完结。在处理器被挂起之后,DR 与外部调试主机通讯,经过查询指令寄存器的办法呼应调试主机宣布的各种调试指令。这些指令包含: 将有关的调试信息搬移到外部调试主机能够调查的缓存区中、修正Memory 空间中的数据、退出DR 使方针程序持续履行等。因为DR 有必要与方针程序运用彼此阻隔的资源而且小型处理器中代码容量,外部Memory空间巨细等都比较受限,因而DR 的规划应该尽或许占用较少的端口数、通用寄存器数和代码总行数。

4、 规划实例

Xilinx 公司的PicoBlaze 是一种常用的细巧型处理器,它由ALU、程序计数器栈( 适用于嵌套子程序) 、16 个8 位通用寄存器、64 字节RAM 构成的暂存器、程序计数器和操控器以及中止支撑电路构成,其代码容量为1024。本节以针对PicoBlaze 的运用为例,规划了一个详细的UDM,并在Spartan3S5000FPGA 进步行了实践验证。该UDM 运用的硬件资源为1 个18KB BRAM 和62 个Spartan – 3逻辑片,软件资源为61 行汇编代码,具有的功用如下:

·可一起在每一行代码处设置断点,在没有设置断点的状况下,可强制发生DI,然后运转DR 输出调试信息;

·能够调查到的调试信息为: 程序计数器PC的值、s0 ~ sb 寄存器、64byte 的暂存器,Memory 空间中的数据,在DR 运转时能够改写上述调试信息。

4. 1 硬件完结

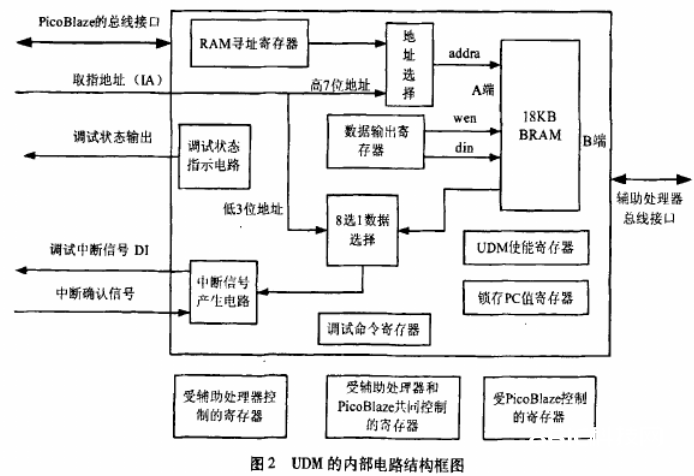

依据PicoBlaze 处理器运用的UDM 硬件结构如图2 所示。UDM 与调试终端和PicoBlaze 都有总线接口,因而其内部寄存器分为3 类: 仅受PicoBlaze操控,仅受辅佐处理器操控以及受二者一起操控。

PicoBlaze 和辅佐处理器分别在双口RAM 的A、B 端口写入数据。为了削减占用PicoBlaze 的I /O端口,PicoBlaze 在向双口RAM 写入数据之前先向RAM寻址寄存器写入地址,然后经过写数据输出寄存器将数据写入前一操作指定的地址中。

双口RAM 的B 端口连接到辅佐处理器的总线,数据位宽为16,可拜访的地址规模为0 ~ 255,地址0 ~ 165 作为交互调试数据的缓存区,地址192 ~255 用于存储断点设置信息。每一个寄存器中寄存16 行代码的断点设置状况,因为PicoBlaze 的代码容量为1024 行,故只需占用64 个寄存器,例如地址为193 的数据为0x4080 则标明第24 和31 行设置了断点。双口RAM 的A 端口数据位宽为8,在DR 运转时用于输入调试信息,在方针程序运转时输出断点设置信息。因而在A 端口有一个地址挑选电路,使得输入A 端口的地址在不同的状况下分别由RAM寻址寄存器和IA 决议。当运转方针程序时,A 端口输入的地址为IA 的高7 位加上偏移量0x180,输出的8bit 数据再经IA 的低3 位寻址输出1bit 数据,这样得到的数据正好反映了与IA 对应的代码是否设置了断点。中止信号发生电路依据上述数据和中止信号的时序要求,发生输出给处理器的DI 信号。

调试指令寄存器由PicoBlaze 和辅佐处理器一起操控,辅佐处理器向该寄存器写不同的数代表不同的调试指令。在运转DR 时经过查询该寄存器来完结对各种调试指令的呼应,在呼应调试指令之前PicoBlaze 将调试指令寄存器清0,作为与辅佐处理器的握手操作机制。当向调试指令寄存器写3 时,不论是否设置了断点都会当即发生DI 信号。

4. 2 软件完结

在依据PicoBlaze 的运用中,为了削减代码容量,DR 的流程比较简略。在初始化预备之后,顺次将s0 ~ sb 寄存器、64byte 的内部RAM,Memory 空间中的数据输出到双口RAM 中,然后堕入一个等候和处理调试指令的循环中。方针程序和DR 履行环境的阻隔经过约束方针程序只允许修正寄存器s0 ~sb 以及64byte 的内部RAM,而DR 只允许修正寄存器se ~ sf 来完结。只有当调试指令为退出调试时,DR 程序才会结束,PicoBlaze 又返回到方针程序的履行。当调试指令为改写调试信息时,PicoBlaze 将重复一次初始化和调试信息输出的进程。

4. 3 实践验证和运用状况

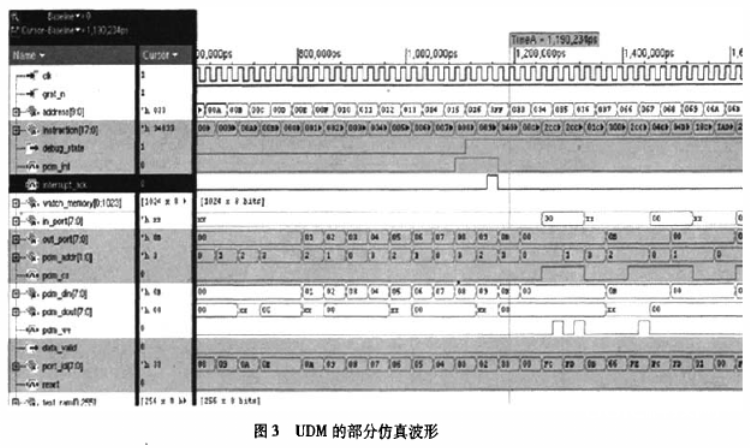

在运用UDM 之前,首要经过NC – verilog 对其进行了仿真,部分仿真波形如图3 所示。图中反映的是当作为DI 的信号pdm_ int 发生了之后,PicoBlaze怎样转入履行DR 的,限于篇幅,验证其他各种功用的仿真波形不在此赘述。

为了进一步对UDM 的功用和功用进行齐备的查验,在FPGA 中树立了如下简略的PicoBlaze 处理器体系。PicoBlaze 外部只接一块252X8bit 的RAM和UDM,PicoBlaze 上的方针程序流程为如下的死循环: 将s0 ~ sb 顺次置入0 ~ 11,再反过来顺次置入11 ~ 0; 将64byte 的RAM 顺次写入0 ~ 63,再反过来写入63 ~ 0; 将外部的RAM 顺次写入0 ~ 251,再反过来写入255 ~ 4。这样的一种简略规划,能够确保从输出的调试信息直接看出处理器在哪行代码处呼应了断点。

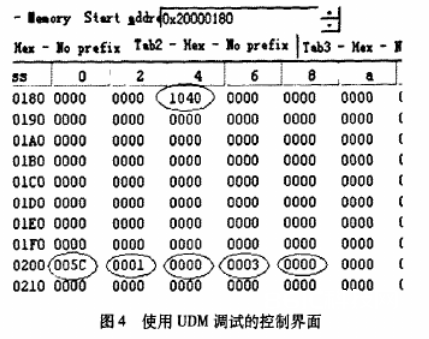

如图4 所示为在调试主机进步行调试操控的界面。偏移地址0x184 处的1040 标明在38 与44 两行代码处设置了断点,事实上从地址0x180 ~ 0x1ff处都能够设置断点。地址0x200 处为当时的PC 值,经过向地址0x208 处写1 可使其更新; 地址0x202处为UDM 的使能位,当其为1 时UDM 才被使能; 地址0x204 为调试指令寄存器,向其写1 使处理器从断点退出,写2 使处理器改写调试信息,写3 使处理器强制进入DR 输出调试信息; 地址0x206 处标明调试状况,当其为3 时标明处理器在运转DR,而且调试信息现已输出结束。

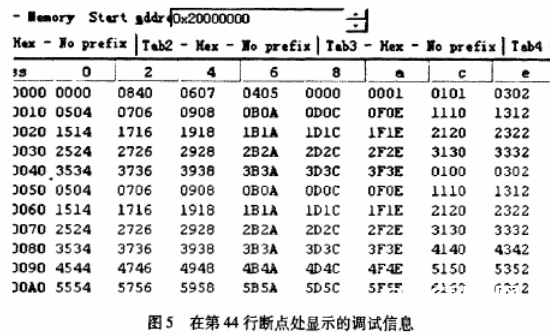

显现调试信息的界面如图5 所示,地址0x00 ~0x0b 显现寄存器s0 ~ sb 的数据,地址0x0c ~ 0x3b显现内部64byte 存储器的数据,地址0x4c ~ 0x14b显现PicoBlaze 外部Memory 空间的数据。因为图5中止点正好设置在完结顺次向PicoBlaze 的Memory空间顺次写0 ~ 251 之后,因而显现的数据是递加的。当断点正好设置在完结顺次向Pico Blaze 的Memory 空间顺次写255 ~ 4 之后,所显现的数据就变为递减。在许多其他断点处显现的调试信息与断点设置的方位也契合预期的状况,因而UDM 完全能够正确而高效地作业。

在开发一款信号处理芯片的FPGA 原型规划中,盯梢处理、电文处理、全体流程操控分别由一个PicoBlaze 完结,而且因为FPGA 资源的约束选用大型处理器来代替上述处理器简直不或许。因为输入PicoBlaze 的数据和操控信号杂乱,仿真验证不能很好地掩盖各种实践的运用景象。经过运用这儿的依据PicoBlaze 处理器规划的UDM,便利地完结了对上述3 个PicoBlaze 的在线调试,对进步开发功率发挥了重要作用。在其他运用PicoBlaze 的工程运用中,上述UDM 也得到了很好的推行。

5、结束语

规划了一种通用调试模块,用于辅佐无调试接口的处理器树立规范的调试机制。经过该模块的运用,提出了一种通用、规范、便利的调试办法,很好地满意了在SOPC 体系中对多个没有调试接口的细巧型处理器完结在线调试的火急需求。新办法经过发生调试中止使处理器跳转到调试服务程序中的办法完结处理器的挂起,经过依据双端口RAM 中一种奇妙的地址映射机制完结一起对多行代码设置断点的功用,经过调试服务程序完结数据搬移等调试指令。新办法还具有易于扩展,能够一起调试多个嵌入式处理器的长处。新的调试办法在工程实践中对进步调试功率发挥了重要作用,是一种普适的,运用价值显着的调试办法。

责任编辑:gt