相同,这款沟通生成器的噪声和失真水平应该远优于这些ADC的规范,依据大部分供货商供给的规范,其本底噪声水平远低于 –140 dBc,失真水平低于–120 dBc,输入信号音频率为1 kHz或2 kHz,最高可达20 kHz。有关适宜高分辨率带宽ADC的典型测验台的典型测验装备,请参阅图1。最要害的元件便是正弦波生成器(单信号音或多信号音),其间依据软件的直接数字频率组成器(DDS)能够供给彻底的灵活性、极高的频率分辨率和时钟同步功能,运用数据搜集体系来履行相干取样,以防止走漏和FFT窗口滤波。

因为本钱只要音频精细剖析仪的几分之一,所以能够依据直接数字频率组成(DDFS)原理规划十分精准的正弦波生成器,但需求经过软件在SHARC®处理器等浮点DSP处理器上完结。一个适当快的浮点DSP将能满意实时性要求,以及一切算法和处理条件,以到达先进的SAR ADC所设置的失真和噪声功能水平。经过运用SHARC内核架构的全字数据长度(32位或64位定点格局)来施行NCO相位累加,运用专有的40位浮点扩展精度来履行正弦近似函数,以及运用数字滤波器来确认频谱形状,量化效应(反转噪声和切断噪声)得到大幅下降,与用于信号重构的数模转化器(DAC)缺陷比较,这种效应能够忽略不计。

重构DAC:要害之处!

首要或许会挑选具有超卓的非线性差错(INL和DNL)规范的高精度DAC,例如超卓的20位高精度DACAD5791。可是它的分辨率只要20位,并且其R-2R结构不支撑施行信号重构,特别是发生十分纯的正弦曲线,这是因为在输入代码转化期间,它存在很大毛刺。传统的DAC架构依据二进制加权电流发生器或电阻网络构建,对数字直通和数字开关损害(例如外部或内部时序摇摆),以及数字输入位的其他开关不对称十分灵敏,特别是在会导致能量改变的严重改变期间。这就发生了与代码相关的瞬态,然后发生高起伏谐波杂散。

在20位以上的分辨率下,运用外部超线性快速采样和坚持放大器对DAC输出去毛刺并无太大协助,这是因为它在几十LSB下会生成自己的瞬态,且会因为重采样发生组推迟非线性。信号重构首要存在于通讯运用,经过运用分段架构(混适宜用于MSB的彻底解码部分和适用于最低有用位的二进制加权元件)来处理毛刺问题。惋惜的是,现在还没有超越16位精度的商用DAC。与NCO彻底可猜测的行为不同,DAC差错难以猜测和精确仿真,尤其是当制造商的动态规范很小或许不存在时,但专用于音频运用的DAC或ADC在外。插值过采样和多位∑-∆ DAC似乎是仅有的处理方案。这些先进的转化器具有高达32位的分辨率、超低失真和高信噪比,是在中低带宽内施行信号重构的最佳挑选。为了在音频频谱或稍宽的频段(20 kHz或40 kHz带宽)内完结超卓的噪声和失真功能,能够运用ADI公司产品系列中超卓的∑-∆ DAC产品,音频立体声DACAD1955, 尽管分辨率最高为24位,这款DAC仍然是商场上十分受欢迎的音频DAC。

这款音频DAC于2004年推出,依据多位Σ-Δ调制器和过采样技能,合作各种技巧,用于缓解这种转化自身固有的失真和其他问题。8

即便现在,AD1955选用的插值LP FIR滤波器仍然是同类超卓产品。它具有极高的阻带衰减(≈–120 dB)和极低的带内波纹(≈±0.0001 dB)。它的两个(左边和右侧通道)DAC能够以最高200 kSPS速度运转,但在48 kSPS和96 kSPS时完结最佳沟通功能,其动态规模以及立体声形式下的SNR,都支撑典型的EIAJ规范、A加权120 dB系数。在单声道形式下,两个通道一起异相组合,功能有望进步3 dB。可是,关于宽带运用,这些规范不太实践,这是因为它们是组成的,带宽规模在20 Hz至20 kHz之间。带外噪声和杂散不会超越20 kHz,部分是因为EIAJ规范、A加权滤波器和音频职业规范界说。这种满意特定音频丈量要求的带通滤波器模仿人耳的频率响应,与未滤波的丈量值比较,功能进步3 dB。

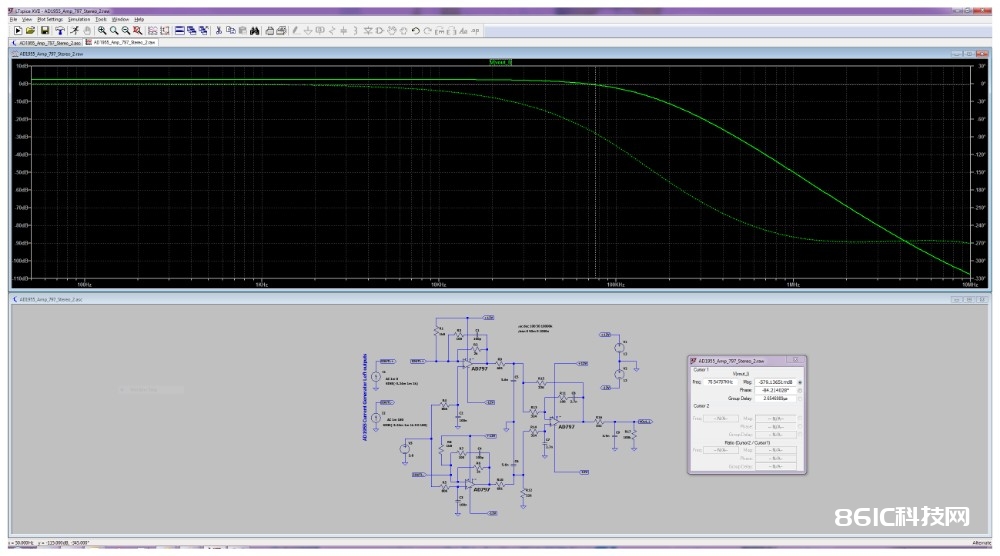

图6.LTspice仿真AD1955 EVB三阶抗混叠滤波器(立体声装备)的频率响应。

DDFS硬件演示渠道:选用AD1955完结正弦波重构

整套DDFS运用两个评价板完结,一个支撑DSP处理器,一个适用于选用AD1955 DAC进行模仿信号重构。挑选第2代SHARC ADSP-21161N评价板的原因在于其可用性、易用性,以及适宜任何音频运用的精简装备。现在仍在量产的ADSP-21161N于不久之前规划,支撑工业高端消费电子和专业音频运用,供给高达110 Mips和660 MFlops,或220 MMACS/s容量。与最新一代的SHARC处理器比较,ADSP-21161N最大的不同在于它选用较短的3级指令管道、一个片内1 Mb三端口RAM,以及数量更少的外设。精准信号音生成器的最终和最要害的级依据AD1955评价板,该板有必要从软件NCO供给的样本中,以彻底复原的办法重构模仿信号。这个评价板带有一个抗混叠滤波器(AAF),优化音频带宽来满意Nyquist规范,除了常用的S/PDIF或AES-EBU接收器外,还配有两个串行音频接口,用于支撑PCM/I2S和DSD数字流。PCM/I2S串行链路连接器用于将AD1955 DAC板连接到ADSP-21161N EVB的串行端口1和3连接器(J)。这两个板都能够装备为选用I2S PCM或DSP形式,以48 kSPS、96 kSPS或192 kSPS采样速率运转。DSP串行端口1生成左右通道数据、字挑选或左/右帧同步,以及双频DAC的数字输入接口所需的SCK位时钟信号。串行端口3仅用于生成运转DAC内插滤波器和Σ-Δ调制器所需的DAC主时钟MCLK,调制器以比输入采样频率(48 kSPS)快256倍(默许)的速度运转。因为一切DAC时钟信号都由DSP生成,所以运用Crystek供给的超低噪声振荡器CCHD-957代替了板原有的低本钱爱普生时钟振荡器。其相位噪声在1 kHz下或许低至–148 dB/Hz,适用于24.576 MHz输出频率。

在模仿输出端,有源I/V转化器有必要用于在恒共模电压下(一般为2.8 V)坚持AD1955电流差分输出,以最大极限削减失真。像AD797 这样的超低失真和超低噪声的高精度运算放大器能够满意此需求,还可用于处理模仿信号重构。 因为两个差分输出由DSP别离处理,因而挑选了具有AAF拓扑结构的立体声输出装备,而不是单声道形式。这个AAF运用LTspice® XVII进行仿真,成果如图6所示。因为滤波器的最终一部分是无源的,所以应该像最近推出的ADA4945那样添加一个有源差分缓冲级。这种具有低噪声、超低失真、快速树立时刻特性的全差分放大器是近乎完美的驱动任何高分辨率SAR和Σ-Δ ADC的DAC配件。ADA4945具有相对较大的共模输出电压规模和超卓的直流特性,能够供给超卓的输出平衡,有助于按捺偶数阶谐波失真产品。

EVB三阶滤波器的–3 dB截止频率为76 kHz,在500 kHz下仅衰减–31 db。这款低通滤波器具有超卓的带内平整性,但带外衰减有必要大幅改进,即便是限于朴实的重构音频运用。要按捺DAC成型噪声和调制器时钟频率MCLK,就有必要满意这一点。依据软件DDS的详细运用,用于单信号音生成器或恣意波形生成器(生成杂乱波形时为AWG),有必要优化AAF,以处理带外衰减或群推迟失真。以我们了解的SRS DS360超低失真函数生成器为例进行比较,选用7阶Cauer AAF可到达相似的采样速率。信号重构由AD1862完结,后者是一款串行输入20位分段R-2R DAC,适用于数字音频运用。AD1862在高达768 kHz (×16 fS)频率下能够坚持20位字采样速率,且具有超卓的噪声和线性度。它支撑单端电流输出,所以能够运用最超卓的放大器来施行外部I-V转化。

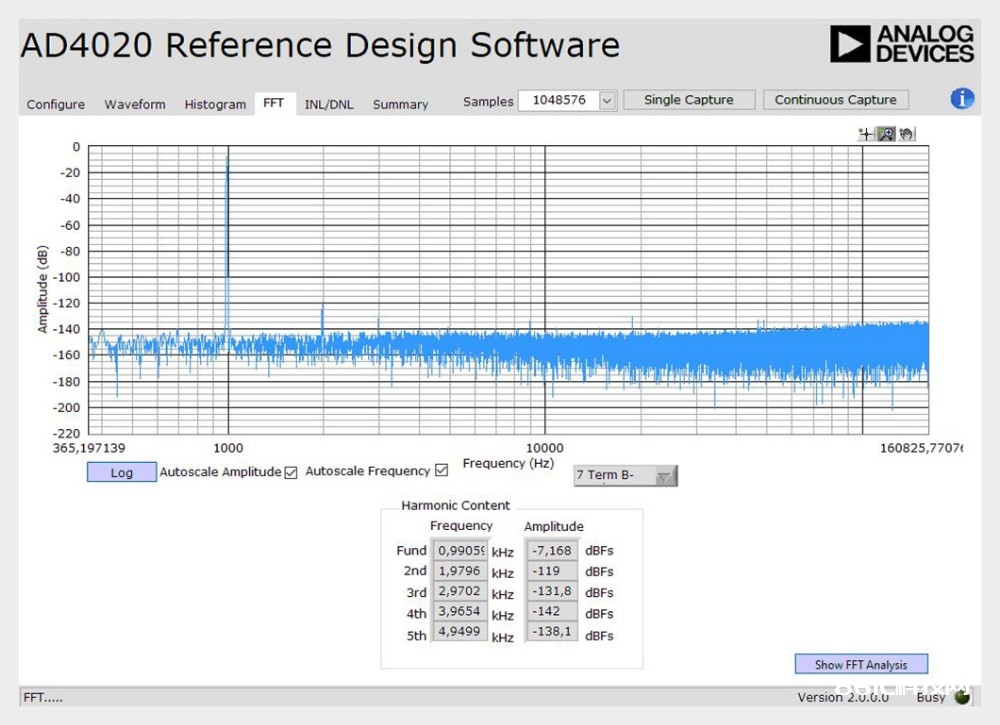

AD1955和SHARC DSP组合针对多种高分辨率SAR ADC施行测验,例如AD4020,其间未设置外部可选无源滤波器。默许情况下,根底AD4020评价板除了板载ADA4807驱动器之外,并无其他选项可用。用于在V_REF/2共模电压下偏置ADC输入的简略电路供给适当低的300 Ω输入阻抗,需求运用信号阻隔、沟通耦合,或运用外部差分放大器模块,例如EVAL-ADA4945-1。电路笔记CN-0513中描绘的AD4020参阅规划板便是一项不错的挑选。它包括一个分立式可编程增益外表放大器(PGIA),供给高输入阻抗,支撑±5 V差分输入信号(G = 1)。尽管这些AD4020板和它们的SDP-H1操控器不支撑相干采样搜集,但它们具有超卓的样本波形捕捉长度,最高可达1M。因而,能够完结具有可选窗口的FFT,供给超卓的频率分辨率和低本底噪声。例如,关于7项Blackman-Harris窗口,图7中所示的1 Mpts FFT图描绘了AD1955在生成的990.059 Hz正弦波下的失真水平。二次谐波是350 kHz带宽内–111.8 dBc下的最大失真重量和最大杂散。可是,在考虑整个806 kHz ADC Nyquist带宽时,SFDR受∑-∆ DAC调制器、内插滤波器频率和其二次谐波(384 kHz和768 kHz)约束。

在相同条件下,对传统的AD1862进行测验,成果显现频率行为稍微不同。在差分装备下,两个20位DAC的时钟速度约为500 kSPS,在1.130566 kHz下,本底噪声为–151 dBFS,正弦输出水平为12 V p-p时的THD为–104.5 dB。在AD4020 Nyquist带宽(806 kHz)下,SFDR挨近106 dB,受三阶谐波约束。DAC重构滤波器依据两个AD743 低噪声FET放大器,与AD1955评价板中的滤波器相同,归于三阶滤波器,可是-3 dB时的截止频率为35 kHz。

为了变得有用,依据DDS的生成器需求选用不错的滤波器,支撑在约250 kHz下完结大于100 dB衰减,以生成到达25 kHz CW信号频率规模的直流。这能够运用六阶切比雪夫滤波器完结,乃至运用用于显现超卓带内平整度的六阶巴特沃兹低通滤波器完结。滤波器阶将被最小化,以约束模仿级的数量和问题点,例如噪声和失真。

图7.从1 M点FFT剖析中能够看出,在低于–111 dBc下具有不错的失真功能,在1 kHz输入频率下,10 kHz至200 kHz频段内呈现最大杂散。本底噪声约为–146 dBFS。

定论

在规范评价板上施行的初级和开箱即用测验显现,用于传统正弦波CW生成的依据处理器的DDS技能要完结高功能指日可下。经过精心规划重构滤波器和模仿输出缓冲级,能够完结–120 dBc谐波失真系数。依据DSP的NCO/DDS不只遭到单信号音正弦波生成约束。经过运用具有适宜的截止频率,且无其他硬件改变的优化AAF(贝塞尔或巴特沃兹),相同的DSP和DAC组合可用作高功能AWG来生成任何类型的波形,例如,彻底组成可设置参数的多信号音正弦波(能够彻底操控每个重量的相位和起伏)来施行IMD测验。

因为浮点算法关于要求高精度和/或高动态规模的运用至关重要,现在,低本钱ADSP-21571或SoCADSP-SC571(ARM®和SHARC)等SHARC+ DSP处理器实践上是业界的实时处理规范,支撑最高10 MSPS的算计采样速率。双SHARC内核和其硬件加速度计选用500 MHz时钟频率,能够供给高于5 Gflops的核算功能和数十个内部专用SRAM,后者是生成各种波形,以及施行杂乱的剖析处理需求的根本组成部分。此类运用标明,在施行精准的数字信号处理时,并非一定要体系性地运用硬件可编程处理方案。得益于ADI公司的CCES、VDSP++ C和C++编译器,以及全套仿真器和实时调试器,浮点处理器及其整个开发环境能够快速轻松地从仿真器(例如MATLAB)移植代码,以及快速施行调试。

参阅文献

1 Joseph A. Webb。美国专利US3654450,1970年4月。

2 Joseph Tierney、Charles M. Rader、Bernard Gold。“数字频率 组成器。”IEEE 音频和电声学论文集,第19卷第1期,1971年3月。

3 Jim Williams、Guy Hoover。AN-132:用于验证纯度的A→D 转化器保真度测验。ADI公司,2011年2月。

4 John F. Hart。核算机迫临算法。Krieger出版公司,1978年。

5 William J. Cody、William Waite。初等函数 软件手册。Prentice-Hall, Inc.,1980年。

6 Robin Green。“更快的数学函数,第2部分介绍。”Sony Computer Entertainment America,2016年5月。

7 Henry T. Nicholas、Henry Samueli。“存在相位累加器切断时的直接数字频率组成器的输出频谱剖析。”IEEE,1987年5月。

8 Robert Adams、Khiem Nguyen、Karl Sweetland。“支撑分段噪声扰码的113 dB SNR过采样DAC。”IEEE,1998年2月。

ADSP-21000系列运用手册,第1卷。ADI公司,1994年5月。

数字信号组成技能教程。ADI公司,2001年3月。

Butler, Oscar。“2017年夏日实习陈述:高精度过采样20位超低功率搜集体系。”(ADI公司,2017年)

Crawford, James A. Advanced Phase-Lock Applications: Frequency Synthesis. AMI, LLC, May 2011.

Crawford, James A。高档锁相运用:频率组成。AMI, LLC,2011年5月。

评价板用户攻略UG-048。ADI公司,2010年2月。EV-4020-REF-DGNZ参阅规划板用户攻略UG-1280。

ADI公司,2019年5月。

Goldberg, Bar-Giora。频率组成数字技能。McGraw-Hill,1995年8月。

Ds360型超低失真函数发生器。Stanford Research Systems,1999年。

Symons, Pete。数字波形生成。剑桥大学出版社,2013年11月。

AD1862数据手册。ADI公司,2011年7月。

1241-2010 – 模数转化器术语和测验办法的IEEE规范。IEEE,2011年1月。

作者简介

Patrick Butler是ADI公司南欧出售集团的一名现场运用工程师,为法国全球商场和部分ADEF客户供给支撑。从1984年至今,他一直在ADI公司作业,首要担任DSP构建模块IC以及高速转化器的开发。在此曾经,他在法国圣艾蒂安斯伦贝谢公司ATE部分作业了5年,任规划工程师,之后法国南特Matra-MHS、AMD和Harris SC-Intersil担任多个运用工程师和FAE职位。现在,他的首要喜好是搜集旧式音响组件,在两个儿子的协助下,着手制造高效的有源喇叭扬声器体系。