导言

机载数据总线在飞机上的位置非常重要。机载总线转化板则是为计算机与机载设备之间的衔接供给的硬件根底。机载设备通过总线转化板与计算机进行通讯以收发数据。因而,用于测验体系的转化板的研发与开发就成为航电开展的一个重要部分。本文介绍的MIII总线转化板的首要功用是将机载火控设备的MIII总线数据转化成串口数据,以便利完结与PC机的通讯,这样,PC机就可读取机载设备数据或发送指令以操作总线设备。

该转化卡选用Top-Down自顶向下的规划办法,并归纳嵌入式可装备微处理器技能,来对体系进行模块化规划。顶层模块则选用图形规划办法,底层模块由VerilogHDL言语描绘,并运用Quartus lI完结仿真及归纳,然后在ALTERA公司的Cyclone II系列EP2C40芯片来完结。此规划提升了体系的处理速度和安稳性。下降了体系的功耗和本钱。

1 MIII总线介绍

MIII总线是某型飞机火控电子设备的专用数据通讯总线,又称第三级总线。MIII总线是单向地址、双向数据、半双工通讯总线。

MIII总线的接口逻辑信号与电信号之间的逻辑关系是:逻辑“1”对应逻辑高电平;逻辑“0”对应逻辑高电平。

MIII总线接口信号线依据功用可分为三组,即数据通讯总线、地址通讯总线和信号操控总线。其间,数据通讯总线包含0pKlK2~15pKlK-2;地址通讯总线:0pAl~15pAl。总线的“输入”表明从MIII总线转化板向某飞机火控设备输出数码标志,“输出”则表明从某飞机火控设备向MIII总线转化板输入数码标志。MIII的A1地址选通首要用于盯梢地址数据与挑选设备,外部写选公例用于在从MIII总线转化板向某飞机火控设备传输数据和地址时的数码盯梢。外部接纳选公例用于在从某飞机火控设备向MIII总线转化板传输数据时的数码盯梢。

2 RS422通讯协议

RS422通讯协议标准的全称为TIA/EIA-422-B串行通讯标准。该标准的数据传输选用差分传输办法,也称作平衡传输。因为RS-422标准的接纳器选用高输入阻抗和发送驱动器,故比RS232具有更强的驱动才能,并可支撑点对多点的双向通讯。RS-422四线接口因为选用了独自的发送和接纳通道,因而不用操控数据方向,各装置之间的任何有必要的信号交流均能够按软件(XON/XOFF握手)或硬件办法(一对独自的双绞线)来完结。

3 转化板全体规划

MIII总线转化板的全体结构如图l所示,由接口电平转化电路、总线接口操控逻辑、双口存储器和RS422转化模块组成。其间总线接口操控单元首要用于地址和数据的收发和存放,以及接口操控信号和驱动信号的发生等;双口存储器RAM用来存放数据和地址,包含MIII总线发送的数据以及PC机发送到MIII总线上的数据和地址;接口电平转化电路由单双向驱动电路芯片组成,该电路的作用是供给契合MIII总线要求的驱动电平信号。

3.1 总线转化规划逻辑

在总线接口操控单元的规划开发中,在严格执行国军标对地上设备的研发标准等要求下,为了保证体系的牢靠性,进步体系的可扩展性和功用,规划时应选用模块化规划办法,并尽可能选用老练的技能和器材。

依据上述规划准则,MIII总线接口板的硬件电路应选用FPGA器材来完结。而选用FPGA完结也具有规划周期短、本钱低、运转速度快、电路功用牢靠、具有集成软核、便利二次开发等长处。

本接口板的规划选用自上而下(Top-Down)的规划技能道路。规划从体系的全体动身,运用Ouartus II软件,并选用结构化描绘办法来对规划目标的功用特性进行剖析,然后自上而下逐渐将问题细化,再依据剖析的成果区分功用模块,并依据电路功用动身运用VerilogHDL言语对各模块电路进行数据流描绘,然后运用Quartus II软件进行各模块的功用仿真,在承认无误之后,再衔接各模块进行逻辑归纳及优化,终究下载到FPGA芯片。

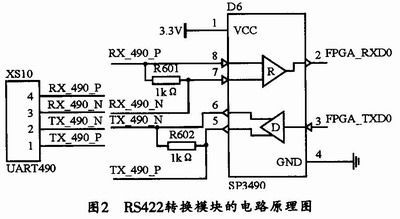

3.2 RS422转化模块

此模块选用SP3490芯片进行RS422通讯协议转化。SP3490芯片Sipex的+3.3V低功率全双工收发转化芯片,完全能够满意各种规格的RS-485和RS-422串行通讯协议。图2所示为RS422转化模块的电路原理图。

3.3 总线接口操控单元

总线接口操控单元的首要功用是MIII总线地址和数据的收发、转化、存放以及接口操控信号和驱动信号的发生等。总线接口操控单元能够依据FPGA嵌入IP软核的SOPC体系来完结。SOPC是一种特别的嵌入式体系,它是片上体系(SOC),即由单个芯片完结整个体系的首要逻辑功用,但它不是简略的SOC,它也是可编程体系,因而具有灵敏的规划办法,并可在FPGA中植入软核处理器。也能够依据规划要求,运用相应的EDA东西来对NIOS II及其外围设备进行构建,以使该嵌入式体系在硬件结构、功用特色、资源占用等方面全面满意体系的规划要求。此体系的开发东西选用Altera公司推出的Quartus II系列软件。FPGA选用Altera公司出产的Cyclone II系列的EP2C40芯片,此芯片选用TSMC验证的90nm低K介电质工艺制作的本钱优化架构,并具有更多的特性和非常大的容量,以及很低的单位逻辑单元本钱,故可满意体系要求。

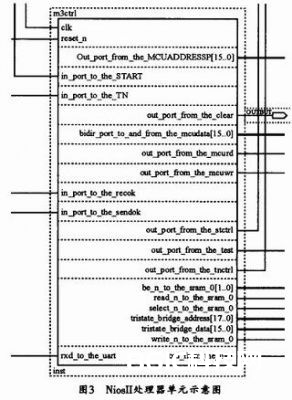

(1)Nios II处理器

Nios II处理器首要担任解析从RS422串口接纳的操控指令,以操控总线转化器,使其依照设定的作业形式运转;一起,该处理器还实时打包接纳到的MIII总线数据,并通过RS422串口上传至PC机,完结PC对MIII总线信息的获取。选用QuartusII软件SOPC Builder生成的Nios II处理器单元如图3所示。

详细作业时,当数据流向为RS422串口到MIII总线时,NIOSII处理器可将数据从RS422串口接纳缓冲存储器中读出,并输出至MIII总线发送缓冲单元中,一起还将数据发送到外部的SRAM中进行存储;而当数据流向为MIII总线到RS422串口时,其办法其之相似,其不同点是因为MIII总线的传输速率远大于串口的传输速率,因而要刺进相应的等候和协调操控信号。

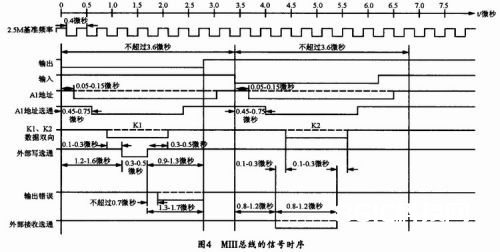

(2)MIII总线收发

MIII总线收发功用则独立于Nios体系。它充分运用FPGA可灵敏装备的特色,并用VerilogHDL言语完结MIII总线的实时性和牢靠性要求较高的要害部分,然后模仿MIII总线的逻辑功用,终究完结MIII总线数据、地址的收发以及与Nios体系通过自定义的接口完结通讯。MIII总线的信号时序如图4所示。

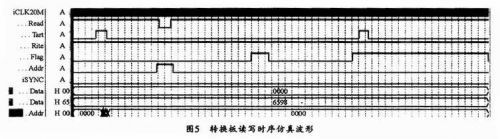

该转化板的读写时序可用VerilogHDL言语描绘,然后选用有限状态机完结上述操作,并用Quartus II进行时序仿真,其仿真波形如图5所示。本文选用的是用时钟同步输出信号的Moore型状态机,该办法可有用消除状态机输出信号的毛刺。

3.4 接口电平转化电路

因为FPGA可编程器材的输入/输出电平通常是3.3 V,而对接MIII总线设备是OC门输入/输出。OC门又称集电极开路(漏极开路)电路,其内部电压为+5 V。所以,FPGA的输入/输出需求进行两次电压转化。

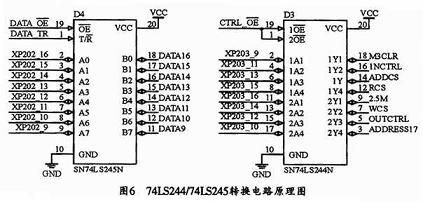

其间,第一次电压转化是把FPGA输入/输出电平的3.3 V转化为5 V电平。因为数据信号是读写双向的,而地址和操控信号是单向的(由MIII总线发送到对接MIII总线设备),因而,其数据信号应当用74LS245芯片来进行转化,而地址和操控线则运用74LS244芯片来转化,其电路原理如图6所示。

因为对接MIII总线设备内部是OC门输入/输出,并且因为OC门电路的输出管的集电极悬空,运用时需外接一个上拉电阻到电源。一般情况下,OC门会运用上拉电阻以输出高电平,此外,为了加大输出引脚的驱动才能,挑选上拉电阻阻值的准则是下降功耗及芯片的灌电流才能应当满足大,然后保证满足的驱动电流满足小。依据此准则,本规划挑选上拉电阻阻值为680Ω。其详细的电平转化电路原理图如图7所示。

FPGA输入/输出的信号,通过以上两个过程的电平转化,就能契合MIII总线对接设备的输入/输出信号要求。至此,只需MIII总线转化板输入/输出的地址、数据和操控信号依照MIII总线时序进行收发,就能够完结MIII总线通讯。

4 结束语

本文介绍了某型火控电子设备的专用数据通讯总线(MIII总线)转化板的规划办法,给出了MIII总线的总线通讯功用。一起介绍了运用F-PGA完结MIII总线部分电路的完结办法。事实上,运用FPGA可简化体系结构,缩短规划周期,进步体系的功用和可扩展性。现在,该转化板通过与某型火控电子设备联调证明,其功用正常,作业安稳,且已得到了用户好评,收到了杰出的社会和经济效益。