1 布景常识

图1 二值图画鸿沟提取演示

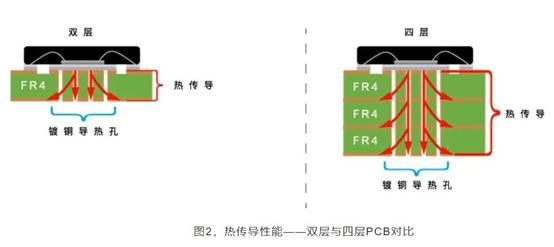

如图1 所示,图1 a为一幅简略的二值图画,通过鸿沟提取后构成如图1 b 所示的图画,显现出了白色区域的概括。

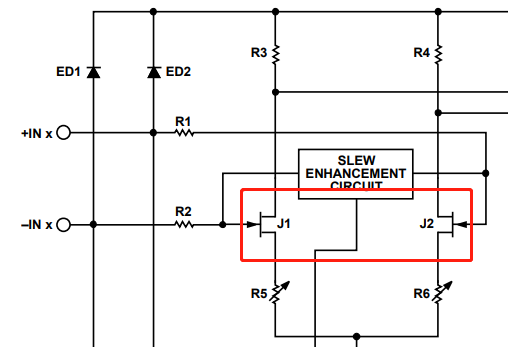

2 鸿沟提取算法

运用黑色提取,布景为白色,‘1’表明白色,‘0’表明黑色。

图2 二值图画鸿沟提取演示

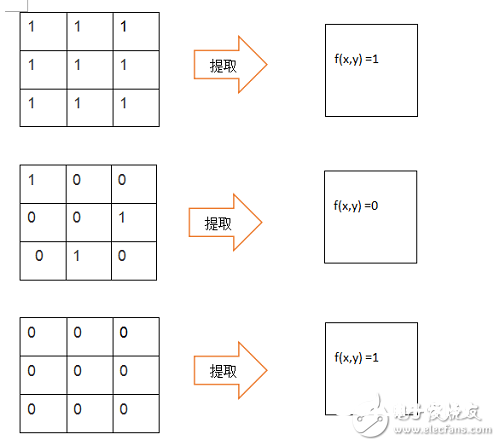

咱们运用3×3模板进行鸿沟提取,所以当3×3九个点都是‘1’的时分,输出为‘1’,当九个点都是‘0’的时分,输出为‘1’,其他状况输出均为‘0’。

3 FPGA二值图画鸿沟提取算法完成

图2 二值图画胀大FPGA模块架构

图2中咱们运用串口传图传入的是二值图画。

FPGA源码:

/*

Module name: boundary_extracTIon.v

DescripTIon: binary image boundary extracTIon

*/

`TImescale 1ns/1ps

module boundary_extraction(

input clk, //pixel clk

input rst_n,

input hs_in,

input vs_in,

input [15:0] data_in,

input data_in_en,

output hs_out,

output vs_out,

output reg [15:0] data_out,

output data_out_en

);

wire [15:0] line0;

wire [15:0] line1;

wire [15:0] line2;

reg [15:0] line0_data0;

reg [15:0] line0_data1;

reg [15:0] line0_data2;

reg [15:0] line1_data0;

reg [15:0] line1_data1;

reg [15:0] line1_data2;

reg [15:0] line2_data0;

reg [15:0] line2_data1;

reg [15:0] line2_data2;

reg data_out_en0;

reg data_out_en1;

reg data_out_en2;

reg hs_r0;

reg hs_r1;

reg hs_r2;

reg vs_r0;

reg vs_r1;

reg vs_r2;

wire[18:0] result_data;

line3x3 line3x3_inst(

.clken(data_in_en),

.clock(clk),

.shiftin(data_in),

.shiftout(),

.taps0x(line0),

.taps1x(line1),

.taps2x(line2)

);

//——————————————————————————

// Form an image matrix of three multiplied by three

//——————————————————————————

always @(posedge clk or negedge rst_n) begin

if(!rst_n) begin

line0_data0 <= 16'b0;

line0_data1 <= 16'b0;

line0_data2 <= 16'b0;

line1_data0 <= 16'b0;

line1_data1 <= 16'b0;

line1_data2 <= 16'b0;

line2_data0 <= 16'b0;

line2_data1 <= 16'b0;

line2_data2 <= 16'b0;

data_out_en0 <= 1'b0;

data_out_en1 <= 1'b0;

data_out_en2 <= 1'b0;

hs_r0 <= 1'b0;

hs_r1 <= 1'b0;

hs_r2 <= 1'b0;

vs_r0 <= 1'b0;

vs_r1 <= 1'b0;

vs_r2 <= 1'b0;

end

else if(data_in_en) begin

line0_data0 <= line0;

line0_data1 <= line0_data0;

line0_data2 <= line0_data1;

line1_data0 <= line1;

line1_data1 <= line1_data0;

line1_data2 <= line1_data1;

line2_data0 <= line2;

line2_data1 <= line2_data0;

line2_data2 <= line2_data1;

data_out_en0 <= data_in_en;

data_out_en1 <= data_out_en0;

data_out_en2 <= data_out_en1;

hs_r0 <= hs_in;

hs_r1 <= hs_r0;

hs_r2 <= hs_r1;

vs_r0 <= vs_in;

vs_r1 <= vs_r0;

vs_r2 <= vs_r1;

end

end

//——————————————————————-

// line0_data0 line0_data1 line0_data2

// line1_data0 line1_data1 line1_data2

// line2_data0 line2_data1 line2_data2

//——————————————————————–

always @(posedge clk or negedge rst_n) begin

if(!rst_n)

data_out <= 16'h0000;

else if(data_out_en1)

if((line0_data0 == 16'h0000) && (line0_data1 == 16'h0000) && (line0_data2 == 16'h0000) && (line1_data0 == 16'h0000) && (line1_data1 == 16'h0000) && (line1_data2 == 16'h0000) && (line2_data0 == 16'h0000) && (line2_data1 == 16'h0000) && (line2_data2 == 16'h0000))

data_out <= 16'hffff;

else if((line0_data0 == 16'hffff) && (line0_data1 == 16'hffff) && (line0_data2 == 16'hffff) && (line1_data0 == 16'hffff) && (line1_data1 == 16'hffff) && (line1_data2 == 16'hffff) && (line2_data0 == 16'hffff) && (line2_data1 == 16'hffff) && (line2_data2 == 16'hffff))

data_out <= 16'hffff;

else

data_out <= 16'h0000;

end

endmodule

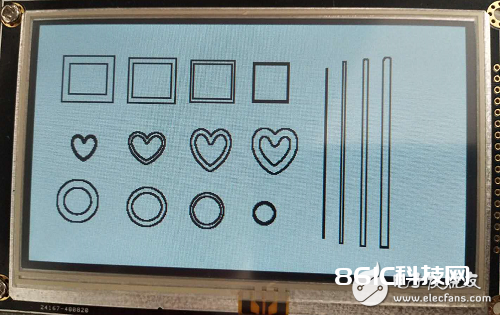

4试验成果

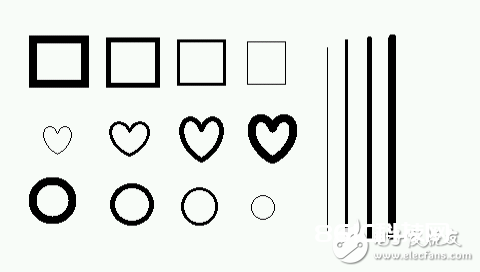

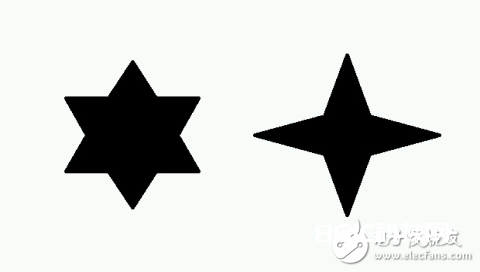

图5 试验原图1

图6试验原图2

图7 试验成果图1

图8 试验成果图2

成果剖析:图5和图7比照,比较粗的线都被查找出了边际,只要最细的那条没有被提取出来,而且被加粗,原因是最细的线条只要三个像素当查找出边际后显现为黑色,两头黑色连在一起所以线条就变粗了。图6和图8边际查找没有问题。