降压DC/DC转化器 (见图1)是一种十分受欢迎的开关DC / DC稳压器拓扑,广泛应用于许多电气和电子,从云基础设施到个人电子产品,再到工厂和楼宇自动化。它们占有了当今一切非阻隔开关稳压器拓扑75%以上的比例。

(见图1)是一种十分受欢迎的开关DC / DC稳压器拓扑,广泛应用于许多电气和电子,从云基础设施到个人电子产品,再到工厂和楼宇自动化。它们占有了当今一切非阻隔开关稳压器拓扑75%以上的比例。

降压转化器 的布局与模仿和规划相同重要,但假如缺少杰出的布局实践或许会延迟开发时刻,乃至形成操作和牢靠性问题。

的布局与模仿和规划相同重要,但假如缺少杰出的布局实践或许会延迟开发时刻,乃至形成操作和牢靠性问题。

布局考虑的要素包括旁路电容器、反应补偿网络组件、功率组件、寄生组件、接地回路和衔接。

旁路电容器

关于旁路电容,最小化引线电感很重要,可经过减小旁路回路面积、缩短高di / dt(电流转化速率)途径上的长度、尽或许运用接地层(如或许)、在电容器两头引进电流途径、防止多种布局等计划来完成。此外,并联不同的电容器类型以下降电容频带两头的阻抗很重要,由于它能够把2MHz至20MHz频率规模(典型的电容器值为0.1μF至0.01μF)的阻抗下降。牵引电容,使其更接近%&&&&&%(IC)引脚,还能向布局规划者展现要害节点和面积,如图2所示。

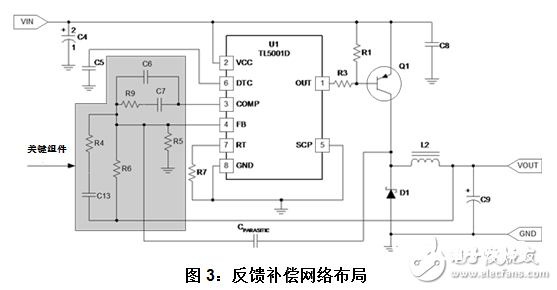

反应补偿网络

将补偿网络置于接近IC差错放大器的当地。放置电阻,使它们直接衔接到差错放大器(FB引脚)的反相输入,如图3所示。

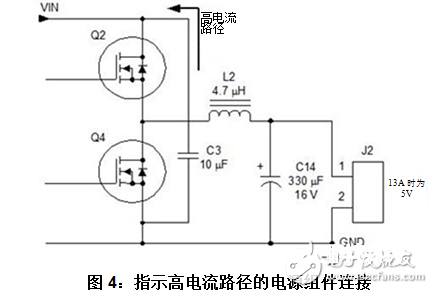

电源组件

保证正确衔接电源组件,由于电流途径中有高di / dt(电流转化速率),如图4所示。途径中的任何电感将导致开关节点振铃,这或许超越功率FET的肯定最大额定值,而且还会在体系中发生谐波和不必要的噪声。方针是经过运用双面印刷电路板(PCB)的装置来最小化回路面积,其间在PCB的一侧上具有MOSFET(金属氧化物半导体场效应晶体管),而在另一侧上具有电容器。保证正确地放置和布设组件。正确的规划无需缓冲电路来削减开关节点振铃。

寄生组件

留意寄生元件,由于它们或许引进并添加电源中的阻抗,这会导致稳定性和操作问题。留意接线电感,特别是低阻抗电路和滤波器、电源开关和守时电路。运用接地层和宽走线以最小化电感。在电路板%&&&&&%方面,留意高阻抗或噪声灵敏电路,并留意电路板平面/层和组件焊盘之间的耦合。电感器之间,特别是环形电感器,也或许发生磁耦合。这种情况下,请考虑其他装置方向。磁耦合也或许发生在环路之间,因而,应最小化环路面积并运用接地平面。

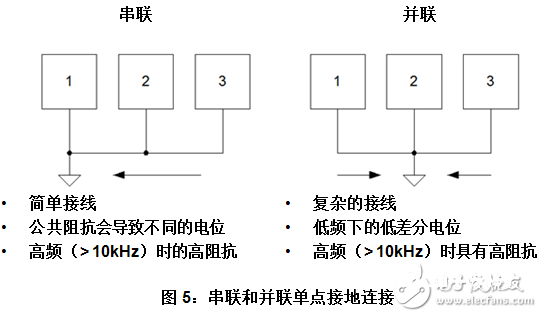

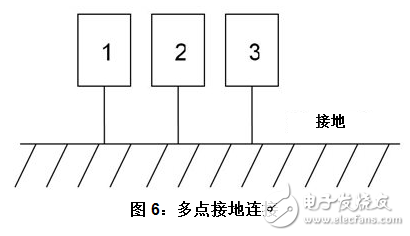

接地回路和衔接

更好的办法是运用多点接地。如图6所示,多点接地答应电路之间具有低阻抗,以最小化电位差,而且还削减了电路走线电感。意图是在单个电路中包括高频电流,并将其保持在接地平面之外。

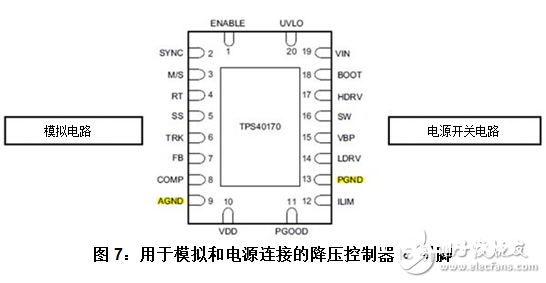

许多降压转化器 操控IC可辨认噪声和安静的电路区域,而且IC引脚如此摆放,使得IC引脚周围的布局和元件安置愈加简单。有些乃至为电源和模仿接地供给独自的引脚,如图7所示的TPS40170 60V同步降压脉冲宽度调制(PWM)操控器引脚。

操控IC可辨认噪声和安静的电路区域,而且IC引脚如此摆放,使得IC引脚周围的布局和元件安置愈加简单。有些乃至为电源和模仿接地供给独自的引脚,如图7所示的TPS40170 60V同步降压脉冲宽度调制(PWM)操控器引脚。

因而,环绕%&&&&&%引脚布局进行布局规划,并运用本文中说到的布局实践可帮助您从一开端就取得正确的降压转化器 规划,并防止今后呈现任何费事。检查TI的降压转化器

规划,并防止今后呈现任何费事。检查TI的降压转化器 和降压操控器挑选表,了解各种降压DC / DC解决计划。

和降压操控器挑选表,了解各种降压DC / DC解决计划。