1方针和布景

1.1项目方针

大规划科学问题对数学算法运算速度的追求是无止境的,因而需求探究更快速的办法。现在依据FPGA技能的可重构高功用核算体系现已成为研讨热门,把数学算法转化成硬件逻辑在FPGA中运转是一个好办法,但数学算法转化为硬件逻辑的进程杂乱,并且受限于硬件电路规划,并不是一切的数学算法都合适转化为硬件逻辑。且其存在的一个遍及的问题便是用户运用编程难度较大,且软件专用、价格昂贵。

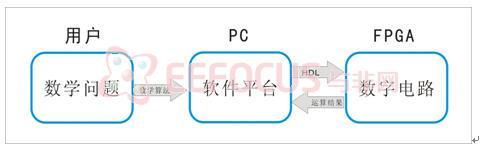

本项意图研讨方针是探究和树立图形化数学算法向硬件转化的理论办法,研讨开发数学算法向硬件逻辑转化的东西,与科学核算软件相结合树立起依据FPGA阵列的科学核算渠道原型。研讨方针结构流程如下:

体系方针结构和流程

FPGA 为各种高速算法的完结供给了一个很好的渠道,可是相同引申出的问题是怎么快速有用的树立这些算法。在数学中最常用的算法表明是流程图办法,因而本研讨针对怎么把数学流程图算法转化成为硬件逻辑以及树立其原型体系进行研讨,方案树立起一个在数学算法的树立和运算中对用户屏蔽EDA软件层,使得各种层次用户均可通明的运用FGPA核算体系,而不用关怀硬件和硬件布置、接口的各个细节,完结PC-FPGA科学核算的原型体系。

1.2运用布景

大规划科学问题对数学算法运算速度的追求是无止境的,因而需求探究更快速的办法。现在依据FPGA技能的可重构高功用核算体系现已成为研讨热门,把数学算法转化成硬件逻辑在FPGA中运转是一个好办法,但数学算法转化为硬件逻辑的进程杂乱,并且受限于硬件电路规划,并不是一切的数学算法都合适转化为硬件逻辑。且其存在的一个遍及的问题便是用户运用编程难度较大,且软件专用、价格昂贵。

FPGA 为各种高速算法的完结供给了一个很好的渠道,可是相同引申出的问题是怎么快速有用的树立这些算法。在数学中最常用的算法表明是流程图办法,因而本研讨针对怎么把数学流程图算法转化成为硬件逻辑以及树立其原型体系进行研讨,方案树立起一个在数学算法的树立和运算中对用户屏蔽EDA软件层,使得各种层次用户均可通明的运用FGPA核算体系,而不用关怀硬件和硬件布置、接口的各个细节,完结PC-FPGA科学核算的原型体系。

-

FPGA硬件加快才能

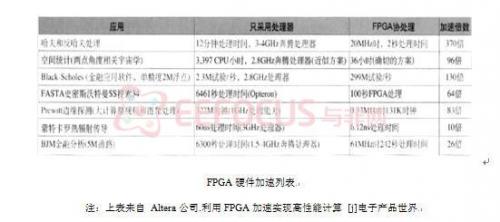

FPGA (现场可编程门阵列)是一种具有大规划可编程门阵列的器材,不只具有专用集成电路(ASIC)快速的特色,更具有很好的体系完结的灵敏性。FPGA可经过开发东西完结在线编程。与CPLD (杂乱可编程逻辑器材)比较, FPGA属寄存器丰厚型结构,愈加合适于完结时序逻辑操控。FPGA供给许多的并行资源,在硬件中只需求几个时钟周期就能够履行完函数功用,而次序操作的处理器则需求成百上千的时钟周期。由于只需求很少的时钟周期,FPGA即便选用较慢的时钟,也能够前进功用。减小时钟速率能够下降功耗,因而,FPGA协处理器的功耗功率远远大于处理器。运用当今高功用FPGA(例如,Altera的Stratix III系列FPGA)的结构和资源优势,许多的运用软件都能够选用硬件加快协处理器,大大前进功用,如表所示。相关于只选用处理器的运用,依据FPGA的协处理器在实践运用中运算履行速度前进了10倍,速度前进100倍也是很常见的。

FPGA硬件加快列表

注:上表来自 Altera公司.运用FPGA加快完结高功用核算 [j]电子产品世界

-

可重构核算

可重构核算(Reconfigurable Computing,RC),简略地说,便是运用FPGA逻辑完结核算使命。有些文献把它称为自习惯核算(Adaptive Computing),也有的文献把它称为FPGA定制核算(Custom Computing)。可重构核算的概念早在20世纪60年代就已提出。在通用微处理器上也运用了这一思维,如组件便是运用多路挑选器来完结功用的改变,而这些组件一般与核算结构不发生直接联络。现在,可重构核算已有较大开展,首要方针是期望经过硬件可编程,来自习惯核算使命的需求,以期到达最佳功用;并且这种硬件结构的改变,能实时地习惯核算使命要求的改变。可重构核算的底层技能是FPGA编程技能,可重构核算的长处是硬件规划的完结依据软件的灵敏性,并且坚持了传统的依据硬件办法的履行速度。其体系结构可变的特色,很好地习惯了实践运用中的多元化需求。

世界现状

世界上首要有XtremeData,Nallatech,美国星桥公司和苏格兰爱丁堡大学FPGA高功用核算联盟研讨类似产品。

-

XtremeData:(www.xtremedatainc.com)

选用了多片Altera® Stratix® III FPGA,并且运用Intel QuickAssist技能,XtremeData XD2000i In-Socket加快器(ISA)展现了这一强壮的1066 MHz协处理处理方案。Stratix III FPGA的快速架构和I/O功用在这一模块中十分有用,完结了安稳的1,066 MHz FSB速率。XD2000i模块相关于现在的GPU还具有功耗、体积、存储器误码校对编码(ECC)等优势:功耗低于60W,模块能够严密装置在刀片外形封装中。XD2000i模块结合了Intel Xeon 5000系列处理器和Stratix III FPGA协处理器,使客户能够运用功用最好的FSB加快器,明显下降了本钱和功耗,产品愈加紧凑。XD2000i模块选用了Stratix III FPGA,在依据Intel的渠道上,完结的某些算法具有优异的功用。Intel QuickAssist技能作业台为Altera和XtremeData等公司供给了立异的协处理器处理方案开发环境。Intel供给依据FPGA的紧耦合In-socket加快器。将依据Stratix III FPGA的XD2000i刺进到Intel Xeon处理器插槽中,使协处理器能够与存储器和主处理器完结高速链接,不需求改动电路板,从而为规划人员供给了简略的硬件集成途径。本年第三季度将供给新版XD2000i模块,四插槽电路板经过独自的FSB处理器互联支撑500K逻辑单元(LE)以及1,536个乘法器。

-

Nallatech:(http://www.nallatech.com)

该公司一向致力于高功用FPGA核算技能的研讨与开发,其处理方案包含了现在业界FPGA最老练和先进的开发技能,在技能的抢先性和运用的遍及性方面取得了一个很好的平衡。模块化的硬件渠道,供给一个由多个FPGA、内存、数模接口和串行接口组合而成的高带宽、内部衔接的结构。具体办法有PCI,VME,cPCI 和PCI-104等办法。FUSE体系软件能够运转在包含Windows,Linux和VxWorks等操作体系的主机体系上,通进程序环境中的APIs,供给装备、操控以及和FPGA运算渠道通讯等功用。供给了在主机体系和Nallatech FPGA运算渠道之间进行装备,操控和通讯的功用,支撑最常用的操作体系和编程言语。支撑的操作体系包含Linux,Windows和VxWorks; FUSE APIs,包含支撑DIMEtalk的APIs,支撑C/C++ 和Java的APIs; 在单个体系中支撑多个FPGA渠道; FUSE Toolbox for MATLAB供给了Matlab和FPGA硬件渠道的直接接口; 支撑硬件和主机之间接口的TCL脚本言语。

-

美国星桥公司

星桥公司以175000-700000美元的价格出售4种类型的FPGA“超核算机”,被称为HC-62的“超核算机”的价格为350000美元,装备11个Xilinx公司出产的价格为3000美元的FPGA芯片,它每秒能够完结2000亿次浮点运算。价格为700000美元类型的“超核算机”包含有22有个Xilinx公司的芯片,每秒能够完结4000亿次浮点运算。别的,客户还必须购买Viva的许可证,每人每年的价格为45000美元。

-

苏格兰爱丁堡大学FPGA高功用核算联盟的Maxwell

Maxwell只占用了爱丁堡大学并行核算中心的两个机柜。这一技能现在存在的问题是,编程十分困难。导致Maxwell还很难投入商业运用。但Maxwell现已试运转了来自石油、金融、医疗成像等职业对处理才能要求较高的运用软件。在运转金融职业的软件时,Maxwell的速度是运用规范处理器的类似体系的2-300倍。Maxwell选用了Xilinx的FPGA技能。

-

国内现状

在依据FPGA的可重构高功用核算的研讨范畴,国内首要有中国科学技能大学等少量几所大学的相关教授在研讨FPGA可重构核算的结构和算法,国内的FPGA可重构核算还处于起步阶段,与世界水平还有很大距离,尚无通用制品运算渠道,国内首要研讨现状比较见下表。

现在一般状况下关于需求运用PC来处理一个科学核算的问题,首要会运用C、Matlab或许其他言语来完结这个算法,变成程序,程序与操作体系进行交互运转,操作体系与机器码在CPU 的物理层上运转 ,而CPU 层则是作业在硬件逻辑层之上 . 能够看到,运算作业于3个层次,假设有办法让咱们的算法直接作业在硬件逻辑层,那么算法的运算速度将大大前进。

科学核算软件如Matlab、Scilab是广阔科研作业者广泛运用的数学东西,科研中许多的科学核算问题都是由科学核算言语来描绘的,本研讨的终究意图是选用依据FPGA的可重构核算技能对科学核算软件进行加快,使其能在PC渠道上完结高功用科学核算。

这项研讨最中心的问题便是怎么把科学核算问题转化成为硬件逻辑(可归纳)。

数学算法在PC上运转和在FPGA上运转状况比照

跟着微电子工艺水平的前进和EDA东西的前进,现在干流商用FPGA芯片的集成规划现已超越I千万等效门,并且还在依照摩尔定律增加,运用这些芯片处理问题的才能越来越强。另一方面,跟着运用要求的开展,可重构核算技能所处理问题的规划越来越大,体系也变得越来越杂乱,一同对体系规划时刻的要求却是越来越短,迫切需求开发和运用与此需求相习惯的支撑电路实时重构技能的高档规划办法和东西来充沛发挥现有FPGA的才能。现在可重构核算面对的首要问题是许多规划作业依托手艺办法完结,并要求用户把握算法、并行核算、硬件描绘言语和电路规划等许多相关常识及丰厚的规划经历,规划难度很大,规划周期较长,严峻限制着可重构核算技能的推行和遍及。

现在世界上尽管现已有一些面向可编程芯片规划的高档东西,但根本上是学习ASIC规划办法,不光短少对实时可重构的支撑,并且终究主动生成的电路往往难以满意用户较为严厉的时序要求。本研讨规划的支撑电路实时重构的科学核算渠道为用户供给一个高档言语规划东西,下降用户的运用难度,大大加快可重构核算电路规划的速度,必将成为可重构核算技能开展的方向,因而本规划是一个极具出路的研讨课题。本体系运用FPGA的可重装备特性,核算机与FPGA运算相结合的核算设备,假设能与支撑电路实时重构的编译技能相结合,将能很轻松地规划出小规划、高功用、低本钱、低功耗的硬件渠道,本体系探究和树立数学算法向硬件逻辑转化的理论办法,关于当时的可重构核算、高速信号处理、FPGA运用规划甚至IC 规划都有着重要含义 ,其要害的问题在于给用户供给数学算法向硬件逻辑转化的东西,以此来协助用户愈加快速的树立运用。

研讨的含义

探究和树立数学算法向硬件逻辑转化的理论办法,关于当时的可重构核算、高速信号处理、FPGA运用规划甚至IC 规划都有着重要含义 ,其要害的问题在于给用户供给数学算法向硬件逻辑转化的东西,以此来协助用户愈加快速的树立运用。依据FPGA的可重构高功用核算将有或许大大下降关于超级核算机的需求,许多的科学核算问题将有或许供给FPGA的硬件逻辑得以完结 . 一同 ,依据FPGA的可重构高功用核算体系的硬件本钱比较高功用超级核算机来说较低,愈加有利于遍及和推行。

1.3研制方案

科学核算东西的研讨一向是科学研讨的前沿范畴,其现在首要方向会集在更高功用的超级核算机构建方面,其首要是运用CPU阵列的规划优势来完结高功用。本研讨选用FPGA可重构数字电路硬件加快的办法在Scilab中完结高功用科学核算,研讨运用图形化办法把数学算法转化到硬件逻辑的办法和软件,方针完结PC与FPGA相结合的科学核算体系:完结 Scilab – FPGA运算使命的协同作业 ,关于用户来说整个体系通明,用户运用Scilab/Scicos编程,硬件生成和加快作业由体系主动完结,整个体系构成一个具有硬件加快功用的科学核算渠道。

-

依据前期开发的Scilab/Scicos-HDL软件,进一步完善,构建起配套的FPGA可重构硬件环境,树立Scilab-FPGA软硬件联合仿真运算渠道,并且在其上树立大规划科学运算运用)。

-

开发与Scilab体系彼此通讯交FPGA硬件模块,完结Scilab/Scicos-HDL与FPGA硬件模块联合仿真;

-

在该体系上规划树立大规划科学核算运用来进行大规划矩阵运算等。可行性:依据4年时刻的前期作业,课题组现已开宣布 科学核算算法(代码办法和图形化办法)转化为 硬件描绘言语(支撑 VHDL、Verilog、 SystemC)的软件,本项目恳求所要完结的是其FPGA硬件模块和其协同作业办法有较高的可行性 。

本项目建在在充沛的前期作业根底之上。项目组成员自主开发了在开源的科学核算软件上进行硬件电路算法规划和仿真的软件Scicos-HDL (2005-2010). 该项意图研讨一向在中科院主动化所中法试验室和法国 INRIA的支撑下进行。

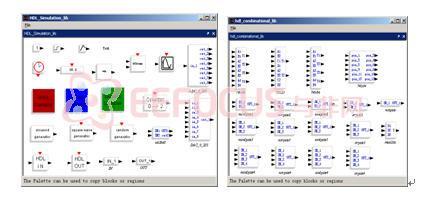

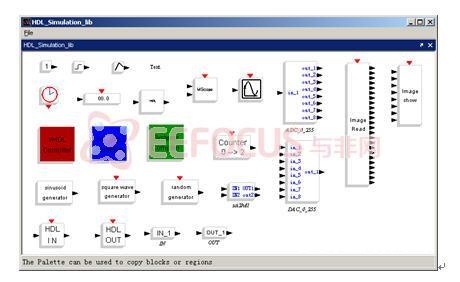

现在Scicos-HDL 0.7运转在Windows渠道。具有5个硬件电路仿真库,包含50多个硬件电路仿真元件和VHDL、verilog、systemc言语编译器模块。当时能够完结组合逻辑电路规划、时序逻辑电路规划和根本的数字信号处理,支撑VHDL、verilog、SystemC 3种硬件描绘言语,支撑主动文档生成,并且生成的HDL代码均为可归纳。Scicos-HDL还支撑与其它Open Source的EDA软件进行集成,构建完好的规划东西链。用户在Scilab / Scicos环境下对电子电路进行高档描绘,并可对自己的规划方案进行体系仿真和批改,然后经过编译生成依据VHDL的RTL级结构模型。该模型可经过各种商业化的IC-CAD接口,终究发生对应于所描绘体系的硬件渠道。运用这样的开发东西,用户在规划%&&&&&%体系时,即便不了解硬件电路的内部细节,甚至不了解 HDL言语,也能够依据自己的需求进行电子电路的规划。还能够使规划数字电路和数字信号处理电路的作业变得方便,门槛更低。

Scicos-HDL元件库示例

课题组前期与中科院主动化所中法试验室(LIAMA)和法国INRIA Scilab安排在科学核算算法转化到硬件描绘言语方面有着长时刻协作根底,协作开发Scilab/Scicos-HDL软件体系现已数年,在开源范畴有必定的知名度。本项目规划把科学核算软件与FPGA技能可重构体系相结合,构建出低本钱和易于运用的高功用科学核算渠道。本体系研讨完结了依据FPGA可重构核算技能的科学核算渠道体系原型,完结了Scilab-FPGA运算使命的协同作业,关于广阔用户,整个体系通明,将其间的数学算法转化为数字电路硬件逻辑的理论办法和软件,开发与Scilab体系彼此通讯交互的FPGA硬件模块,完结Scilab/scicos-HDL与FPGA硬件模块联合仿真,在高功用科学核算范畴,有较强的运用价值。

1.4研讨含义

探究和树立数学算法向硬件逻辑转化的理论办法,关于当时的可重构核算、高速信号处理、FPGA运用规划甚至IC 规划都有着重要含义 ,其要害的问题在于给用户供给数学算法向硬件逻辑转化的东西,以此来协助用户愈加快速的树立运用。依据FPGA的可重构高功用核算将有或许大大下降关于超级核算机的需求,许多的科学核算问题将有或许供给FPGA的硬件逻辑得以完结 . 一同 ,依据FPGA的可重构高功用核算体系的硬件本钱比较高功用超级核算机来说较低,愈加有利于遍及和推行。

2规划与完结

本章来阐明关于项目整个体系的规划结构进行了阐明,并且阐明晰现在完结的部分。

2.1全体规划

2.1.1全体规划图

体系中 Scicos-HDL模块担任 硬件电路的规划、仿真和HDL代码输出。当用户完结了一个 硬件规划后 ,能够先行在Scicos-HDL中进行软件仿真,仿真完结后,用户能够导出VHDL、Verilog、SystemC这三种硬件描绘言语的代码(可归纳)。导出的HDL代码经过用户手动处理,下载到NETFPGA板子上后,经过千兆以太网接口,与Scicos-HDL进行软硬件联合仿真。

在NETFPGA板子上,经过以太网衔接MicroBlaze处理中心,运用HTTP协议进行数据交流Scicos-HDL导出的代码以用户自界说IP的办法参加到体系中。

2.1.2技能开展道路

本节来论述项目技能的根本原理和开展的技能道路。

(1)数学算法转化成硬件逻辑原理

图形化的算法描绘和仿真是一种常见的算法表达办法,其也最接近于什物性质的描绘,现在核算机软件中选用图形化仿真办法的许多,如MatlAB,SystemView、labView等.本研讨规划了一套依据硬件常识的图形化算法仿真机制,使得用户在软件中依据算法需求画出算法流程图,由体系处理后构成硬件逻辑描绘,其根本的结构描绘如下:

|

用处 |

核算机程序结构 |

FPGA结构 |

|

加法 |

+ 运算 |

硬件加法器 |

|

乘法 |

X 运算 |

硬件乘法器 |

|

循环结构 |

FOR 循环 |

计数器 |

|

判别结构 |

IF |

数值比较器+数据挑选器 |

|

递加结构 |

i++ |

加法计数器 |

|

递减结构 |

i– |

减法计数器 |

|

矩阵加法 |

多条程序完结 |

矩阵加法器 |

|

矩阵乘法 |

多条程序完结 |

矩阵乘法器v |

|

赋值 |

赋值句子 |

寄存器 |

|

功用模块 |

函数 |

算法硬件模块 |

|

数组 |

数组 |

RAM |

核算机程序结构与FPGA程序结构比照

经过能够看出在程序规划中能够完结的程序根本结构在FPGA均有对应的硬件完结。本体系中数学算法转化成硬件逻辑是经过树立图形化运算机制根底上:增加FPGA流水线运算根本元件、运用图形化办法衔接各个元件构成算法逻辑图、把算法逻辑图转化成为可归纳HDL描绘这三个进程进行完结。

(2)协同作业中FPGA模块并行核算

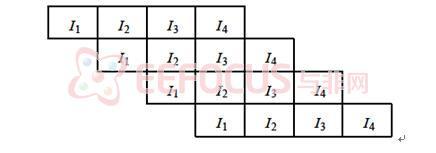

FPGA运算与核算机运算的一个很大的差异在于FPGA中的各个运算单元都是实践硬件存在而核算机运算中的各个运算单元首要是在软件体系中树立次序履行,因而FPGA能够完结一切运算单元的和谐并行核算,可是FPGA并不能主动完结并行核算使命,这需求选用流水线技能来完结。

流水线处理源自现代工业出产装置线上的流水作业,是指将待处理的使命分解为相对独立的、能够次序履行的,而又彼此相关的一个个子使命.图1 是选用流水线技能的一个指令集的操作进程,咱们将某一操作分为4 个子使命:取指令I1 ,译码I2 ,取操作数I3 和运算I4 ,假设每个操作履行的时刻均为T ,则履行4 个操作的履行时刻为4 T ,将这4 个子使命在时刻上堆叠,用4 个子部件来完结,相应的4 个子部件衔接成串行办法,每个子部件履行的时刻为T ,每隔T 时刻就可输出一个操作处理成果,平均速度前进了4 倍,在参加恰当的搬运操控之后,即成为流水线操作的作业办法.

选用流水线技能的一个指令集的操作

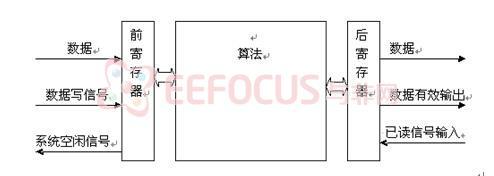

选用流水线技能,能够大大前进体系运转速度,特别合适于需求进行大批量简略运算的场合,如数字信号处理中的卷积操作、FIR 或FFT滤波器等。本研讨中作为算法流程机制的FPGA模块均选用流水线结构,其根本结构如下:

根本算法流程模块

一个根本的算法流程模块选用前寄存器和后寄存器,使得体系模块的作业只取决于自身的运算是否完结,在全体中相对独立,体系中有多个此类算法模块是独立并行作业。

(3) FPGA-PC协同科学核算

此项包含2个方面的内容:一个是FPGA算法体系中自身就有支撑科学核算的算法模块;一个是FPGA运算体系能够和核算机端的科学核算体系衔接起来完结FPGA-PC协同科学核算作业。

关于第一个方面本研讨在体系的元件库中设置了矩阵运算元件库在完结根本的矩阵运算:矩阵运算是科学核算中的一个重要办法,要完结高功用的科学核算在体系内部就必须装备多种硬件矩阵运算处理模块,如矩阵硬件加法器、乘法器。

关于第二个问题,本研讨运用netfpga硬件体系,与开源的科学核算软件Scilab进行接口,完结FPGA运算体系与科学核算体系协同作业。

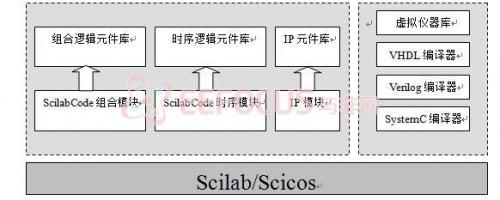

本研讨中体系软件依据Scilab/Scicos开发,完结三个首要功用:

-

运用Scilab/Scicos进行图形化算法规划;

-

把图形化数学算法转化成为硬件逻辑的功用;支撑 VHDL、Verilog、 SystemC 三种硬件描绘言语,生成的硬件逻辑可归纳;

-

与NETFPGA硬件体系完结 FPGA-PC协同使命运算;

2.2软件规划

软件模块的主体功用是硬件规划、仿真、输出、软硬件联合运算。

软件模块的结构如下

软件结构图

软件体系现在现已完结的有组合逻辑元件库、时序逻辑元件库、虚拟仪器库、VHDL编译器、Verilog编译器、SystemC编译器。

组合逻辑元件库

时序逻辑元件库 超级元件库

虚拟仪器库

IP 元件库

2.2.1组合逻辑元件

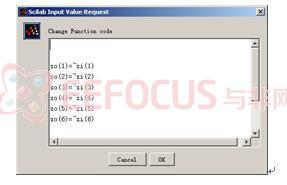

一切的组合逻辑元件,均派生自ScilabCode组合模块 ,运用者只需运用scilab 言语在ScilabCode组合模块 中界说模块功用 和 模块的引脚 ,体系会主动生成相应的硬件描绘。

例如:

用户翻开一个ScilabCode组合模块 放置于 规划区后 ,点击元件的SET菜单,弹出界面进行引脚的功用的设置:

组合逻辑元件引脚设置界面

组合逻辑元件功用设置界面(运用纯Scilab言语描绘)

设置完结点击“QUIT”按钮,体系主动生成元件

组合元件 74ls04

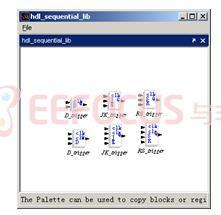

2.2.2时序逻辑元件

一切的时序逻辑元件,均派生自ScilabCode时序模块 ,运用者只需运用scilab 言语在ScilabCode时序模块 中界说模块功用 和 模块的引脚 ,体系会主动生成相应的硬件描绘。

例如:

用户翻开一个ScilabCode时序模块 放置于 规划区后 ,点击元件的SET菜单,弹出界面进行引脚的功用的设置:

时序逻辑元件引脚设置界面

时序逻辑元件功用设置界面(运用Scilab言语描绘,状况转化图)

设置完结点击“QUIT”按钮,体系主动生成元件

时序逻辑元件比如

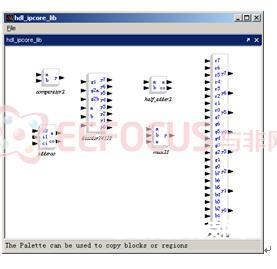

2.2.3IP Core元件

一切的IP Core元件,均派生自IP Core模块 ,运用者只需在IP Core模块 中界说模块功用 和 模块的引脚 ,体系会主动生成元件。

例如:

用户翻开一个IP Core模块放置于 规划区后 ,点击元件的SET菜单,弹出界面进行引脚的功用的设置:

IP Core元件引脚设置界面

进行引脚设置今后,体系会主动生成VHDL、Verilog、SystemC这三种硬件描绘言语的模板,用户依据所需功用修正模板,即可完结模块规划。

VHDL言语模板

Verilog言语模板

SystemC言语模板- 头文件

SystemC言语模板- 程序文件

修改完结,点击:“QUIT”按钮,体系后主动完结元件的树立。

IP Core元件比如

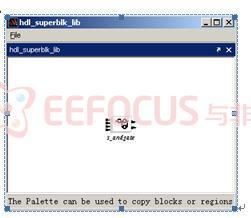

2.2.4超级模块元件

超级元件是指由多种不同的元件组合起来的元件,用户能够依据需求运用 组合逻辑元件、时序逻辑元件、IP Core元件 来树立超级元件,别的超级元件也可由数个超级元件组成。

超级元件内部

超级逻辑元件比如

2.2.5编译器模块

VHDL编译器,能够将Scicos-HDL中规划的硬件电路输出成为可归纳的VHDL言语代码。

VHDL编译器,能够将Scicos-HDL中规划的硬件电路输出成为可归纳的VHDL言语代码。

Verilog编译器,能够将Scicos-HDL中规划的硬件电路输出成为可归纳的Verilog言语代码。

Verilog编译器,能够将Scicos-HDL中规划的硬件电路输出成为可归纳的Verilog言语代码。

SystemC编译器,能够将Scicos-HDL中规划的硬件电路输出成为可归纳的SystemC言语代码。

SystemC编译器,能够将Scicos-HDL中规划的硬件电路输出成为可归纳的SystemC言语代码。

2.2.6虚拟仪器模块

虚拟仪器模块首要是针对元件电路调试和仿真中常常运用的几种元件和仪器进行虚拟化。但更多的Scicos-HDL中能够Scicos自身很多的元件作为虚拟仪器元件。

8位的ADC 与 DAC 元件

图画的读取和显现元件

示波器元件

波形发生器元件

2.2.7接口模块

接口模块至关重要,它担任了Scicos-HDL仿真引擎与 Scilab\Scicos体系仿真引擎的接口。

接口元件

2.3硬件规划

体系的硬件部分依据NETFPGA完结。

2.3.1NETFPGA

NetFPGA渠道具体的组成框图如下:

NetFPGA是由美国斯坦福大学(Stanford University)开发规划的一个低本钱可重用硬件渠道。一个完好的NetFPGA体系由NetFPGA开发板、双口千兆以太网卡、运转于CentOS操作体系的PC机(或服务器)以及其他软件程序组成,经过各个层次软硬件的相互配合完结杂乱的网络结构测验。其间NetFPGA开发板是整个渠道的中心,为用户供给了及其丰厚的硬件资源。

中心部分是一个Xilinx公司的Virtex-II Pro 50型FPGA,这个比较大的FPGA由用户自界说的逻辑来编程,其间心时钟频率为125 MHz。别的还有一个小的Xilinx Spartan型FPGA用来完结衔接主机处理器的PCI接口的操控逻辑。

在外部存储器方面,两片4.5MB的Cypress公司SRAM与FPGA中心逻辑同步运转于125 MHz时钟频率,字长36比特。一共64 MB的两片Micron公司DDR2型SDRAM与FPGA异步运转,其时钟频率为200MHz,字长32比特,存储带宽400 M字/秒(12,800Mb/s)。

在外部接口方面,除了衔接PC主机的PCI总线插口,一个Broadcom公司的物理层收发器(PHY)包含了四个千兆位以太网接口,使该渠道能够衔接四根规范的category 5、category 5e、或category 6以太网双绞线来收发数据分组,并组成网络拓扑;四端口的PHY内部衔接着作为FPGA软核的四个千兆位以太网MAC操控器。此外,两个SATA衔接口使得体系内部的多个NetFPGA能够经过SATA数据线衔接起来,相互之间直接以很高的速度交流数据,而不用再经过PCI总线。

NetFPGA经过PCI总线与主机CPU衔接,供给了硬件加快的数据通道,分管CPU的处理使命。主机CPU依照DMA办法读写NetFPGA上的寄存器和存储器来装备NetFPGA的作业形式,并对NetFPGA的作业状况进行监控。

此外,双口千兆以太网卡用来给主机供给本地网络接口,并与NetFPGA衔接,完结特别的用法。

NetFPGA渠道的组成框图

NetFPGA开发板的首要硬件组成:

Xilinx Virtex-II Pro 50 FPGA

内嵌两颗高功用PowerPC处理器

世界通用的JTAG测验端口

4.5 MB高速静态随机存取器

内嵌64MB二代内存

4组速率高达1Gbps的规范以太网接口

支撑 Cat5E和Cat6规范电缆

NetFPGA体系框图:

|

2.3.2硬件结构

硬件部分依据NETFPGA的硬件,主体结构如下图:

依据NETFPGA的硬件结构图

以MicroBlaze为中心,千兆以太网作为与PC交互接口,Scicos-HDL输出的代码,用户手动增加到 用户自界说模块中 ,完结硬件布置。

由于NETFPGA体系依据LINUX,所以本规划选用了一个外部的 XILINX Platform Cable USB设备,进行下载与调试的作业,使得NETFPGA硬件能够独立作业。

NETFPGA硬件衔接图

2.3.3微处理器

MicroBlaze 是依据Xilinx公司FPGA的微处理器IP核,和其它外设IP核一同,能够完结可编程体系芯片(SOPC)的规划。MicroBlaze 处理器选用RISC架构和哈佛结构的32位指令和数据总线,能够全速履行存储在片上存储器和外部存储器中的程序,并和其它外设IP核一同,能够完结可编程体系芯片(SOPC)的规划。MicroBlaze处理器选用RISC架构和哈佛结构的32位指令和数据总线,能够全速履行存储在片上存储器和外部存储器中的程序,并拜访其的数据。

Micro Blaze处理器选用RISC架构和哈佛结构,32位地址总线,独立的指令和数据缓存,并且有独立的数据和指令总线衔接到IBM的OPB总线,使得它能很简略和其它外设IP核一同完结全体功用。图3.2.2显现了MicroBlaze的接口衔接和架构布局,图3.2.3显现了MicroBlaze的内部功用块图。

MicroBlaze的接口衔接和架构布局

MicroBlaze内部的功用块图

(1)内部结构

MicroBlaze内部有32个32位通用寄存器和2个32位特别寄存器—PC指针和MSR状况标志寄存器。为了前进功用,MicroBlaze还具有指令和数据缓存。一切的指令字长都是32位,有3个操作数和2种寻址形式。指令按功用区分有逻辑运算、算术运算、分支、存储器读/写和特别指令等。指令履行的流水线是并行流水线,它分为3级流水:取指、译码和履行,如图2所示。

(2)存储结构

MicroBlaze是一种大端存储体系处理器,运用如图3所式的格局来拜访存储器。

(3)中止操控和调试接口

MicroBlaze能够呼应软件和硬件中止,进行反常处理,经过外加操控逻辑,能够扩展外部中止。运用微处理器调试模块(MDM)IP核,可经过JTAG接口来调试处理器体系。多个MicroBlaze处理器能够用1个MDM来完结多处理器调试。

(4)快速单一衔接路接口

MicroBlaze处理器具有8个输入和8个输出快速单一链路接口(FSL)。FSL通道是专用于单一方向的点到点的数据流传输接口。FLS和MicroBlaze的接口宽度是32位。每一个FSL通道都能够发送和接纳操控或数据字。

运用EDK(嵌入式开发套件)能够进行MicroBlaze IP核的开发。东西包中集成了硬件渠道出产器、软件渠道发生器、仿真模型生成器、软件编译器和软件调试东西等。EDK中供给一个集成开发环境XPS(Xilinx渠道作业室),以便运用体系供给的一切东西,完结嵌入式体系开发的整个流程。EDK中还带有一些外设接口的IP核,如LMB、OPB总线接口、外部存储操控器、SDRAM操控器、UART、中止操控器、定时器等。运用这些资源,能够构建一个较为完善的嵌入式微处理器体系。

在FPGA上规划的嵌入式体系层次结构为5级。可在最低层硬件资源上开发IP核,或或已开发的IP核树立嵌入式体系,这是硬件开发部件;开发IP核的设备驱动、运用接口(API)和运用层(算法),属软件开发内容。

运用MicroBlaze构建根本的嵌入式体系。经过规范总线接口—LMB总线和OPB总线的IP核,MicroBlaze就能够和各种外设IP核相连。

EDK中供给的IP核均有相应的设备驱动和运用接口,运用者只需运用相应的函数库,就能够编写自己的运用软件和算法程序。关于用户自己开发的IP核,需求自己编写相应的驱动和接口函数。

2.3.4MAC

MAC的操控选用了XILINX的IP EthernetLITE,简化以太网子体系。关于长途监督或操控运用中所需求的简略网络接口来说,最小化网络子体系就足够了。

MicroBlaze “Lite” Ethernet Subsystem:MicroBlaze以太网简化子体系

简化以太网子体系

运用不带中止的Ethernet Lite IP在简略的查询形式下完结规划就能够了。一同还能够将悉数软件,包含简略的运用层,都存储在Xilinx FPGA中的本地存储器中。运用XPS中的根本体系构建导游(Base System Builder wizard)能够简略地创立这样的MicroBlaze规划。

2.3.5HTTP接口

·lwip网络协议栈

Lwip是Light Weight IP的缩写,它是专门为嵌入式体系运用的TCP/IP协议栈。Lwip既能够移植到操作体系上,又能够在无操作体系的状况下独立运转。Lwip支撑多网络接口下的IP转发,%&&&&&%MP协议,UDP协议,TCP协议。不同于一般的TCP/IP协议栈,在Lwip的处理器模型中,一切TCP/IP协议栈都在一个进程傍边完结,而不是在每一层都有一个独自的进程。这样TCP/IP协议栈就和操作体系内核分开了,避免了跨层传输数据时频频的上下文操作。而运用层程序既能够是独自的进程也能够驻留在TCP/IP进程中。假设运用程序是独自的进程,能够经过操作体系的邮箱、音讯行列等和TCP/IP进程进行通讯。假设运用层程序驻留TCP/IP进程中,那运用层程序就运用内部回调函数接口和TCP/IP协议栈通讯。

·SOCKET编程

网络的Socket数据传输是一种特别的I/O,Socket也是一种文件描绘符,它具有类似于翻开文件的函数调用Socket()。依据操作体系的Socket编程有三种类型:流式套接字,数据报式套接字,原始式套接字。其间只要流式套接字供给一个面向衔接的牢靠的数据传输服务。

·服务器端HTTP协议的完结

HTTP协议是一种较为常用的运用层协议,它是Hypertext Transfer Protocol的缩写。HTTP协议选用客户端和服务器的形式,经过客户端向服务器宣布恳求,取得服务器端的呼应。在本体系规划中SOPC体系作为HTTP协议的服务器。HTTP恳求和呼应的报文格局是类似的,报文有一个恳求行/状况行和一个头部组成,有时还或许包含主体。在恳求行中包含了恳求类型,URL,版别等。在呼应行中包含状况码,状况短语等。头部格局为:(头部姓名:头值)。下面是一个HTTP恳求的比如。

|

恳求 |

应对 |

|

GET /usr/bin/image HTTP/1.1 Accept: image/gif Accept: image/jpeg |

HTTP/1.1 200 OK Date: Mon,08-Jan-05 13:15:14 GMT Server: Challenger MIME-Version: 1.0 Content-length: 2048 (图画文件主体) |

表4-1 一个HTTP恳求的比如

在EDK中,每一个外设IP模块都有自己的软件函数库。运用Libgen东西,将所需外设函数数库的头文件增加进工程中,经过调用这些函数能够操作和操控这些外设。例如对串口的操作如下:

//初始化串口,设置波特率等参数,清空发送和接纳缓冲,制止中止;

运用规范C言语进行运用程序的开发,编写相应的算法软件,完结体系功用。

将编写的程序代码运用mb-gcc编译东西,依据体系的软件一起,生成.ELF文件。在编译链接之前,若挑选调试办法,就会在生成文件中参加调试接口SMDstub,进行程序的硬件调试。

运用体系的硬件模型以及RAM块的安排结构文件、ELF文件和用户完毕文件,运用FPGA归纳完结东西(如Xilinx XST)进行归纳,然后下载生成的装备BIT文件到方针板上。运用EDK中供给的GDB调试东西能够进行程序调试。有两种调试办法:软件仿真和硬件调试。软件仿真能够进行程序的功用调试,在开发东西内部就能够进行,不需求硬件支撑。硬件调试便是经过JTAG接口或串口(可在硬件规划时挑选),衔接到方针板上的运用体系中的XMD调试接口,将软件程序下载到体系中进行调试。本课题运用的方针板上的主芯片为Xilinx Spartan IIE 30万门的FPGA,体系时钟为50MHz。实践运转彻底满意规划要求。

H TTP 协议及其完结

嵌入式Web 服务器技能的中心是HTTP (超文本传送协议) 引擎。HTTP 是WWW 上的协议。HTTP 协议使Web 服务器和阅读器能够经过Web 交流数据。他是一种恳求/ 呼应协议,即服务器等候并呼应客户方恳求。当用户要阅读服务器上的一个网页时,一个HTTP 恳求就会从用户的阅读器发到HTTP 服务器。服务器呼应这个恳求, 把指定的网页传送回来, 用户才看到了网页。

HTTP协议不保护与客户方的衔接,他运用牢靠的TCP衔接,一般选用TCP 的80 端口。客户/ 服务器传输进程可分为4 个根本进程:阅读器与服务器树立衔接;阅读器向服务器恳求文档;服务器呼应阅读器恳求;断开衔接。服务器程序开端运转时,主进程就创立一个套接字,

并与主机地址绑定到一同,随后置为被迫监听状况,等候客户端衔接恳求的到来。一旦接纳一个衔接,就回来一个新的套接字描绘符,主程序则拓荒一个新的子程序来处理这个新的衔接。这样体系能够一同

接纳多个客户端的恳求。首要创立套接字,将套接字与本地地址和端口绑定,并设置套接字处于监听状况。Web 服务器在接纳一个衔接恳求后,读取用户的恳求,依据用户的恳求进行相应的处理。当恳求位静态文本时,文档直接提交输出,当恳求位动态文本时,恳求模块主动调用脚本引擎,将脚本替换位现场数据,再提交输出,当恳求为带参数的履行指令时,恳求解析器调用指令履行模块剖析指令并操控监控前端。

Http 规划模型

CPU 自身是以软核的办法完结,其功用可依据需求进行定制,十分灵敏。EDK 不光在硬件规划上供给了支撑,在软件上也为规划者供给了较好的支撑,供给了现成的网络协议栈。加上EDK供给的集成开发环境使得软件开发愈加便当。选用这种办法的操控体系具有操控涣散、开放性好、运用简略、安稳性好等长处,并且能够经过阅读器进行长途多点监控和长途支撑,是未来操控体系开展的一个趋势。

2.3.6IP核封装

规划运用输入GPIO 32位,输出GPIO 32位。

2.3.7规划进程

Software:Xilinx ISE Design Suite 10.1 SP3

ISE主界面

新建一个工程

挑选FPGA信号和嵌入式处理器类型

挑选时钟频率和调试办法

增加 ETHERNET模块、GPIO模块和内存模块

增加体系时钟

设置调试办法和体系测验

体系设置清单

设置完结并保存

设置完结后的工程

界说内存类型

界说体系中止

挑选操作体系 petalinux

2.3.8规划截图

规划完结之后的体系规划图

2.3.9编译代码

关于嵌入式LINUX体系代码的编译,本项目选用虚拟机的办法在Ubuntu下完结。

虚拟机选用开源的 Sun VirtulBox

发动Ubuntu

装置短少的库

设置环境变量

设置环境变量

Petalinux文件

Petalinux文件

设置Petalinux

转化autoconfig.in的格局。输入指令:

>vi autoconfig.in

将呈现vi的修改界面,在vi的指令行形式输入以下指令:

>:set ff=unix

然后保存退出。输入指令:

>:wq

这样,就完结了autoconfig.in的导入作业。

编译Petalinux

开端编译

编译完结

3试验与剖析

3.1试验规划

3.1.1试验标题

24位五颜六色图画的2值化处理

3.1.2完结结构

依据RGB图画灰度公式 :

Gray =0.299*R+0.587*G+0.114*B (公式1)

Gray = (R^2.2 * 0.2973 + G^2.2 * 0.6274 + B^2.2 *0.0753)^(1/2.2) (公式2)

本试验中运用 公式1 进行核算

灰度图画二值化办法:

阈值法二值化

试验中选用一个依据参数可调整的规划,以表现本体系在算法可重构方面的长处。

试验原理图

3.2模块剖析

本节关于试验中所运用的各个模块进行剖析。

3.2.1输入模块

担任图画的输入:

图画读取模块

3.2.2数值核算模块

担任处理图画数据的灰度改变和二值化核算。

3.2.2.1R重量元件

核算: 0.299*R 选用ScilabCode组合元件形式完结

引脚设置

功用设置

3.2.2.2G重量元件

核算 0.587*G选用ScilabCode组合元件形式完结

界面设置

功用设置

3.2.2.3B重量核算元件

核算 0.114*B选用ScilabCode组合元件形式完结

引脚设置

功用设置

3.2.2.4RGB_ADD

核算 R重量+G重量+B重量 选用IP Core形式完结

引脚设置

功用设置

功用设置

3.2.3数据比较模块

二值化元件 选用ScilabCode组合元件形式完结

引脚设置

功用设置

3.2.4输出模块

图画显现模块

3.3试验进程

3.3.1运转环境

体系软件

Scilab 5.1

Scicos-HDL 0.7 for Windows

体系硬件

Hardware:NETFPGA board

Software:Xilinx ISE Design Suite 10.1 SP3

3.3.2装置 Scilab 5.1 for Windows

在 http://www.scilab.org/ 进行下载

留意 只支撑 scilab5.1 的windows版, scilab5.1今后的版别中由于Scicos改作xcos , 此版别正在开发中。

3.3.3装置Scicos-HDL

1.Download Scicos-HDL package, save it, like (D:/scicoshdl_nv/scicos-hdl)

2. open /scilab-5.1/modules/scicos/etc/scicos.start

before (//end // if %scicos)

please add the following sentence:

exec(D:/bak/scicoshdl_nv/scicos-hdl/ScicosHDL_start.sce);

3. Run Scilab/Scicos, you can use Scicos-HDL now.

Scicos-HDL is a free software.

Under Scilab licence.

Scicos-HDL Copyright (c) 2004-2010

ZhangDongKangCai (NXU, LIAMA,SCILAB)

scicoshdl@gmail.com

4. all examples :/scicos-hdl/example

5. Contact: scicoshdl@gmail.com

装置完结之后,发动Scilab5.1 , 能够看到Scilab加载的时分,Scicos-HDL现已发动。

Scicos-HDL装置后Scilab发动界面

3.3.4装置SIVP

Scilab图画读取等作业咱们运用了SIVP作为东西,因而需求装置 SIVP (http://sivp.sourceforge.net/ 下载 )

发动Scilab后,点击Toolboxes菜单的SIVP菜单,发动SIVP.

3.3.5发动Scicos

在Scilab中输入 scicos 指令, 即可发动Scicos

发动scicos

Scicos发动后界面如下:

Scicos界面

点击Palette菜单的Palette选项

Scicos元件菜单

点击今后能够看到Scicos-HDL的各个库文件现已装置

Scicos元件菜单

3.3.6Scicos-HDL

时序逻辑元件库

超级元件库

虚拟仪器库

IP 元件库

组合逻辑元件库

3.3.7翻开试验工程

运用Scicos 翻开 规划工程

翻开试验工程

图画处理工程

加载图片

加载的图片显现

点击simulate菜单中的RUN选项

处理进程开端

处理完结的成果

代码输出

运用VHDL、Verilog、SystemC编译器对规划好的代码进行输出。

输出的VHDL代码

输出的Verilog代码

输出的SystemC代码 (带一个VC++ 2008的工程文件做调试用,Scicos-HDL体系内置 BCC5.5)

硬件衔接图

NETFPGA直接经过JTAG接口与核算机相连

NETFPGA与Scicos-HDL协同运算部分,部分完结,本项目未彻底完结,需要持续尽力。(略)

3.4提交的内容

本项意图软件部分和规划部分完结,硬件部分部分完结。

提交的内容:

-

Scicos-HDL 0.7

-

试验规划和测验文件 imgray.cos

-

试验输出的SystemC 、VHDL、Verilog代码

-

FPGA代码模板