4.3锁相环电路

4.3.1倍频电路规划思路

CPLD的FLASH中存储的正弦波的一个周期用256个点来输出,而正弦波的频率要求是在1300Hz~3000Hz规模内可调,步长为0.1Hz.这就要求FLASH模块的时钟频率在333KHz~768KHz规模内按步长25.6Hz可调。CPLD用的外部晶振为125MHz,假如这个时钟频率由CPLD分频发生,不能到达规划要求。可是CPLD能够完结频率在1300Hz~3000Hz规模内按步长0.1Hz可调,再把这个频率进行256倍频就能够到达规划要求了。

4.3.2锁相环电路芯片挑选

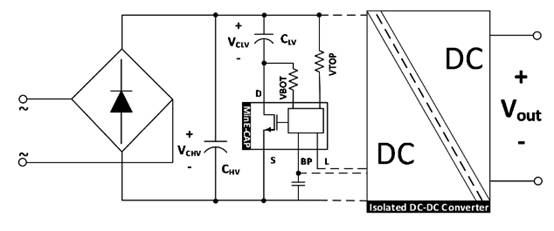

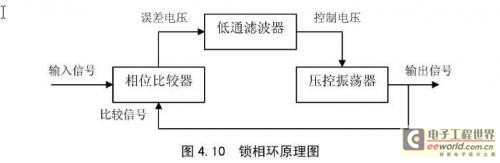

运用锁相环能够完结十分安稳的倍频电路。锁相环是一个相位负反应的闭合环路,其频率盯梢原理图如图4.10所示.

锁相环是由相位比较器(也称鉴相器)、低通滤波器LPF和压控振动器VCO三个环路部件组成的一个反应操控系统。相位比较器(也称鉴相器)对基准输入信号和压控振动器引进的信号进行比较,当基准信号和压控振动器信号频率与相位相一起,鉴相器的输出为零;当两信号的频率和相位不一起,鉴相器的输出就发生一个差错电压,这个差错电压通过滤波环节,操控压控振动器,使其输出频率和相位与输入信号的频率和相位肯定匹配,锁相环路既完结了“锁相”。

将压控振动器输出信号通过N分频后再输入到相位比较器中,那么锁相环确定后压控振动器输出的信号频率便是基准信号频率的N倍,这便是锁相环完结倍频电路的原理,如图4.11所示。

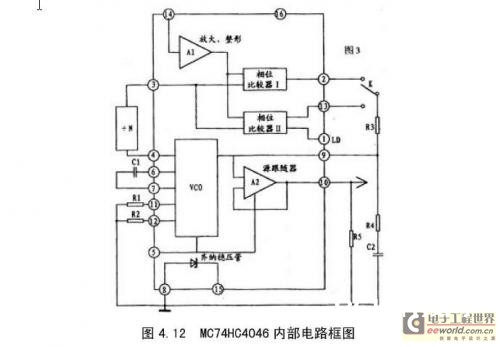

现在常运用%&&&&&%锁相环74HC4046,它的内部电路框图如图4.12所示。

主要由相位比较器Ⅰ、Ⅱ、压控振动器(VCO)、线性放大器、源跟从器、整形电路等部分构成。比较器Ⅰ选用异或门结构,当两个输人端信号Ui、Uo的电平状况相异时(即一个高电平,一个为低电平),输出端信号UΨ为高电平;反之,Ui、Uo电平状况相一起(即两个均为高,或均为低电平),UΨ输出为低电平。当Ui、Uo的相位差Δφ在0°-180°规模内变化时,UΨ的脉冲宽度m亦随之改动,即占空比亦在改动。从比较器Ⅰ的输入和输出信号的波形(如图4.13所示)可知,其输出信号的频率等于输入信号频率的两倍,而且与两个输入信号之间的中心频率坚持90°相移。对相位比较器Ⅰ,它要求Ui、Uo的占空比均为50%(即方波),这样才能使确定规模为最大。本规划中要发生的时钟频率为占空比为50%的方波,所以运用相位比较器Ⅰ.

74HC4046锁相环选用的是RC型压控振动器,有必要外接电容C1和电阻R1作为充放电元件。当PLL对盯梢的输入信号的频率宽度有要求时还需要外接电阻R2.因为VCO是一个电流操控振动器,对守时电容C1的充电电流与从9脚输入的操控电压成正比,使VCO的振动频率亦正比于该操控电压。当VCO操控电压为0时,其输出频率最低;当输入操控电压等于电源电压VDD时,输出频率则线性地增大到最高输出频率。VCO振动频率的规模由R1、R2和C1决议。因为它的充电和放电都由同一个%&&&&&%C1完结,故它的输出波形是对称方波。