摘要:为了满意外场配备检测设备的便携化和信号收集的实时化要求,根据PC104总线的高效数据传输特色,选用了上位机操控板和信号收集板相结合的嵌入式体系建立办法,在信号收集板中经过FPGA操控逻辑完结了多通道开关、信号调度电路和A/D转化器的配备,并把收集的信号数据传输给上位机操控板进行实时显现。运用结果表明,该实时信号收集处理体系操作简略,具有较高的实时性和稳定性。

关键词:PC104;FPGA;数据收集;嵌入式体系;逻辑操控

0 导言

PC104是嵌入式工控机的一种,其外部总线接口为PC104总线。运用堆叠的方法可以将多个PC104主板结合到一同,并经过螺栓固定,确保体系的结实牢靠,应对恶劣的运用环境。因为PC104具有功耗低,体积小,扩展性高,功能强大等长处,其已经在航空航天、军用武器配备、工业操控等范畴得到了广泛的运用。

在对武器配备进行测验保护时,常常需求对设备中的各类模仿信号进行剖析,从而对武器体系的运转状况做出判别。现在常见的测验设备往往实时性不高,无法更多地进行人机交互。一起因为测验设备体积过于巨大,并不便利在外场对武器配备进行直接的测验和保护。跟着现阶段军用配备外场测验的信息化程度逐步进步,迫切需求研制出体积小、结构紧凑的便携式实时测验设备。

现在干流的实时信号收集方法是经过高速A/D转化器材来完结的,其长处是信号精度高,实时的信号收集带来了很多的数据需求处理,对后端的信号处理体系提出了较高的要求。因而本文建立了根据PC104总线的实时信号收集处理体系,凭仗FPGA的高速处理才能操控A/D转化器完结数据的收集,并经过PC104总线将数据提供给上位机完结用户对实时信号的监测。

1 整体规划方案

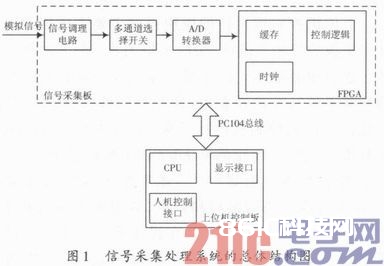

本文的实时信号收集处理体系首要包含信号收集板和上位机操控板2部分,两者之间经过PC104总线进行通讯。上位机操控板以CPU为中心,扩展出VGA,RJ45等人机交互所需求的外围设备接口。信号收集板首要包含了FPGA逻辑操控、A/D转化器、通道挑选开关、前端信号调度器等。实时信号收集处理体系的整体结构图如图1所示。

信号收集处理体系进行作业时,上位机操控板的CPU经过PC104总线向底层信号收集板发送指令,对其作业参数进行设置。CPU与FPGA之间经过地址和数据总线完结指令及数据的交互。多通道挑选开关对外部输入的模仿信号进行通道挑选,在信号调度芯片对模仿信号进行相应的预处理之后,在FPGA的逻辑操控下由A/D转化器完结信号的收集。FPGA经过PC104总线实时地将收集的信号数据传输给CPU,经过运转在上位机操控板的运用程序完结数据的终究剖析和处理。信号收集处理体系可以经过FPGA逻辑操控模块灵敏地调整采样速率,来满意多种信号不同速率的采样要求。

2 硬件体系规划

2.1 上位机操控板

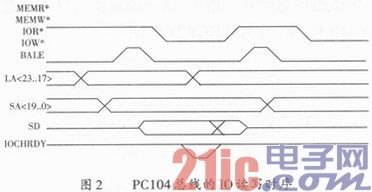

本体系选用深圳盛博公司的PC104模块SCM9022作为上位机操控体系硬件渠道,其处理器为英特尔凌动N455处理器,运用了1 GB的DDR3内存,支撑2 GB的SSD和1路SATA接口,支撑2个100 Base-T以太网口,具有8路GPIO接口和6个串口,4个USB 2.0接口,规范鼠标键盘接口,支撑18位的LVDS和VGA显现。SCM9022的硬件资源可以满意对所需求收集信号的处理,用户可以便利地运用其通用的外设接口完结必要的人机交互。上位机操控板包含了64针脚的双排单列插针J1和40针脚的双排单列插针J2,一共104根信号总线。上位机操控板是规范的PC104模块,其尺度为96 mmx90 mm。当作业在8 b数据形式下时,J2的针脚信号无效,只要J1针脚有用;当作业在16 b数据形式下时,J1和J2一切针脚都有用。在104个针脚中,包含了16个数据针脚,7个锁存地址针脚,20个地址针脚,32个操控针脚,14个地线和电源线,1个14 MHz的OSC,1个8 MHz的BCLK。其间,SA[0..11]为地址总线;SD[0..7]为数据总线;IOR为输入/输出接口的读操控,低电平有用;IOW为输入/输出接口的写操控,低电平有用;DATA为串行数据;BALE为地址锁存信号;CLK为移位脉冲;SY-CLK为总线时钟;IOCHADY为输入/输出接口的准备就绪信号,该信号由集电极开路门或三态门驱动,低电平时处于无效状况,表明输入/输出接口设备需求将总线的周期延伸。时序如图2所示。

2.2 信号收集板

为了能快速高效确保上位机操控板与信号收集板之间的PC104总线数据通讯,底层的信号收集板运用了Altera公司的CycloneⅢ系列FPGA芯片EP3C25F256C7N,经过操控逻辑来依照PC104总线的时序进行数据传输。该芯片具有200 Kb逻辑单元、8 Mb嵌入式存储器以及396个嵌入式乘法器可以在操控信号收集芯片的一起,将收集的信号数据传输给上位机。需求留意的是,因为PC 104总线的针脚都是5 V电平,而FPGA芯片选用了3.3 V的电平信号,所以在信号收集板上运用了74LVH162245芯片对电平进行转化,调整电气特性,完结由TTL电平向LVTTL电平的转化,并增强驱动才能。在信号的收集过程中,因为外部的多路模仿输入信号往往比较弱小,其电平的起伏很小,为了确保A/D转化模块收集到满足强的信号起伏,在信号收集板中运用了扩大器INA103把输入信号进行调度扩大到0~10 V之间。INA103是由BB公司出产的低功率增益可调通用仪器扩大器,其具有高精度宽带宽的特色。在增益为100时,对应的带宽仍到达200 kHz。该芯片选用了可调电阻调整扩大倍数,详细公式如式(1)所示:

G=1+6 kΩ/R (1)