12.5体系硬件装备计划

12.5.1FPGA的装备

FPGA作可编程器材,能够依据用户的需求进行现场可编程。体系可选用了JTAG形式和AS形式进行FPGA编程装备。

JTAG形式编程直接对FPGA进行编程,运用JTAG形式,在QuartusII东西中输出sof文件(SRAMObjectFile)。其优点是编程速度快,而且由所以对FPGA的SRAM结构进行编程,编程次数要多得多;可是掉电后,SRAM保存的编程信息将会丢掉。

当程序调试结束,需求固化的时分,能够通过AS形式将终究文件(pof文件)烧写到装备芯片里边。

本体系选用的装备芯片是EPC1441PC8。装备芯片具有掉电保存才能,在体系上电时,FPGA首先从装备芯片中读取编程数据,并对FPGA进行加载。

12.5.2VideoDecoder(SAA7113H)的装备

体系上电后,VideoDecoder芯片正常作业之前是需求进行装备的。所谓的装备,便是通过I2C接口对它的内部寄存器进行读写。装备的首要意图是告诉VideoDecoder体系当时选用的信号输入端口、格局和特殊要求。

本体系的作业要求是:1路PAL制式视频,AI11管脚输入,输出为ITU656格局,YUV份额为4∶2∶2。对应的SAA7113H的寄存器装备如表12.1所示。

表12.1 SAA7113H寄存器装备值

|

地址 |

内容 |

地址 |

内容 |

地址 |

内容 |

地址 |

内容 |

地址 |

内容 |

地址 |

内容 |

|

0 |

00 |

10 |

38 |

20 |

00 |

30 |

00 |

40 |

02 |

50 |

FF |

|

1 |

08 |

11 |

0C |

21 |

00 |

31 |

00 |

41 |

FF |

51 |

FF |

|

2 |

C0 |

12 |

E8 |

22 |

00 |

32 |

00 |

42 |

FF |

52 |

FF |

|

3 |

33 |

13 |

00 |

23 |

00 |

33 |

00 |

43 |

FF |

53 |

FF |

|

4 |

00 |

14 |

00 |

24 |

00 |

34 |

00 |

44 |

FF |

54 |

FF |

|

5 |

00 |

15 |

00 |

25 |

00 |

35 |

00 |

45 |

FF |

55 |

FF |

|

6 |

E0 |

16 |

00 |

26 |

00 |

36 |

00 |

46 |

FF |

56 |

FF |

|

7 |

0D |

17 |

00 |

27 |

00 |

37 |

00 |

47 |

FF |

57 |

FF |

|

8 |

B8 |

18 |

00 |

28 |

00 |

38 |

00 |

48 |

FF |

58 |

00 |

|

9 |

01 |

19 |

00 |

29 |

00 |

39 |

00 |

49 |

FF |

59 |

00 |

|

A |

80 |

1A |

00 |

2A |

00 |

3A |

00 |

4A |

FF |

5A |

07 |

|

B |

47 |

1B |

00 |

2B |

00 |

3B |

00 |

4B |

FF |

5B |

80 |

|

C |

40 |

1C |

00 |

2C |

00 |

3C |

00 |

4C |

FF |

5C |

00 |

|

D |

00 |

1D |

00 |

2D |

00 |

3D |

00 |

4D |

FF |

5D |

00 |

|

E |

01 |

1E |

00 |

2E |

00 |

3E |

00 |

4E |

FF |

5E |

00 |

|

F |

2A |

1F |

00 |

2F |

00 |

3F |

00 |

4F |

FF |

5F |

00 |

12.5.3VideoEncoder(SAA7128)的装备

体系上电后,VideoEncoder芯片正常作业之前是需求进行装备的。所谓的装备,便是通过I2C接口对它的内部寄存器进行读写。装备的首要意图是告诉VideoEncoder体系当时选用的信号输出端口、格局和特殊要求。

本体系的作业要求是:1路PAL制式视频输出,CVBS管脚输出,输入为ITU656格局,YUV份额为4∶2∶2。对应的SAA7128H的寄存器装备如表12.2所示。

表12.2 SAA7128H寄存器装备值

|

地址 |

0 |

1 |

2 |

3 |

4 |

5 |

6 |

7 |

8 |

9 |

A |

B |

C |

D |

E |

F |

|

内容 |

00 |

00 |

00 |

00 |

00 |

00 |

00 |

00 |

00 |

00 |

00 |

00 |

00 |

00 |

00 |

00 |

|

地址 |

10 |

11 |

12 |

13 |

14 |

15 |

16 |

17 |

18 |

19 |

1A |

1B |

1C |

1D |

1E |

1F |

|

内容 |

00 |

00 |

00 |

00 |

00 |

00 |

00 |

00 |

00 |

00 |

00 |

00 |

00 |

00 |

00 |

00 |

续表

|

地址 |

20 |

21 |

22 |

23 |

24 |

25 |

26 |

27 |

28 |

29 |

2A |

2B |

2C |

2D |

2E |

2F |

|

内容 |

00 |

00 |

00 |

00 |

00 |

00 |

0D |

00 |

1F |

1F |

75 |

3F |

06 |

3F |

00 |

00 |

|

地址 |

30 |

31 |

32 |

33 |

34 |

35 |

36 |

37 |

38 |

39 |

3A |

3B |

3C |

3D |

3E |

3F |

|

内容 |

00 |

00 |

00 |

00 |

00 |

00 |

00 |

00 |

1A |

1A |

13 |

00 |

00 |

00 |

00 |

00 |

|

地址 |

40 |

41 |

42 |

43 |

44 |

45 |

46 |

47 |

48 |

49 |

4A |

4B |

4C |

4D |

4E |

4F |

|

内容 |

00 |

00 |

00 |

68 |

10 |

97 |

4C |

18 |

9B |

93 |

9F |

FF |

7C |

34 |

3F |

17 |

|

地址 |

50 |

51 |

52 |

53 |

54 |

55 |

56 |

57 |

58 |

59 |

5A |

5B |

5C |

5D |

5E |

5F |

|

内容 |

00 |

83 |

83 |

80 |

8C |

0F |

C3 |

06 |

02 |

80 |

34 |

7D |

AF |

2D |

3F |

3F |

|

地址 |

60 |

61 |

62 |

63 |

64 |

65 |

66 |

67 |

68 |

69 |

6A |

6B |

6C |

6D |

6E |

6F |

|

内容 |

00 |

02 |

46 |

CB |

8A |

09 |

2A |

77 |

41 |

88 |

41 |

12 |

02 |

20 |

A0 |

B4 |

|

地址 |

70 |

71 |

72 |

73 |

74 |

75 |

76 |

77 |

78 |

79 |

7A |

7B |

7C |

7D |

7E |

7F |

|

内容 |

41 |

C3 |

00 |

3E |

B8 |

1E |

15 |

16 |

15 |

16 |

2B |

D9 |

80 |

00 |

00 |

00 |

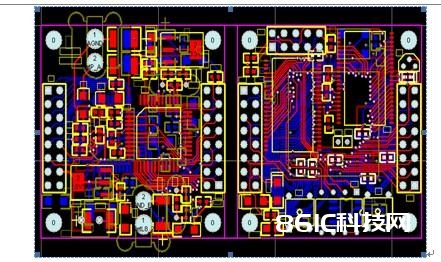

12.5.4印刷电路板(PCB)规划

本体系选用了层叠式的电路板结构,两块电路板通过双排连接器组合成一个体系。其间,FPGA相关电路在一块板上,视频的编解码器在别的一块板上。

传输一路数字视频信号需求9个有必要的ITU656信号(DATA0~DATA7,CLOCK)和两个可选的同步信号(HSync,VSync)。别的,I2C装备接口还需求2个信号(SCL,SDA),加上1个电源信号,2个地信号等,总共16个信号。

通过布局布线后,得到两个板子的地图如图12.5所示。

将这个地图文件提交给制版厂就能够加工规划了。

图12.5数字图像倍焦体系PCB