跟着数字年代的到来,数字技能的运用现已浸透到了人类日子的各个方面。数字体系的开展在很大程度上得益于器材和集成技能的开展,闻名的摩尔定律(Moore’s Law)的预言也在集成电路的开展进程中被印证了,数字体系的规划理念和规划办法在这进程中发生了深入的改变。从电子CAD、电子CAE到电子规划主动化(EDA),跟着规划杂乱程度的不断添加,规划的主动化程度越来越高。现在,EDA技能作为电子规划的通用渠道,逐步向支撑体系级的规划开展;数字体系的规划也从图形规划计划向硬件描绘言语规划计划开展。可编程器材在数字体系规划范畴得到广泛运用,不只缩短了体系开发周期,而且运用器材的现场可编程特性,可依据运用的要求对器材进行动态装备或编程,简单易行地完结功用的添加和修正。

在现代工业的开展中,实时测控体系得到广泛运用,这就对高速数字信号处理体系提出了更高的要求。因为要触及很多的规划,为了进步运算速度,运用了很多DSP器材。数字收集体系是整个体系的中心部分之一,传统办法是运用MCU或DSP经过软件操控数据收集的模/数转化,这样必将频频间断体系的运转然后削弱体系的数据运算,数据收集的速度也将受到限制。因而,DSP+CPLD的计划被认为是数字信号处理体系的最优计划之一,由硬件操控模/数转化和数据存储,然后最大极限地进步体系的信号收集和处理才能。

1 体系总体计划

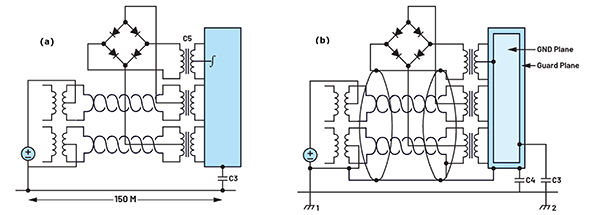

数据收集体系是依据DSP的信号处理体系中的一部分。框图如图1所示。该数字信号处理体系用于随机共振理论在弱信号检测中的运用研讨中。整个体系由信号扩大、信号滤波、信号采样、高速数字信号处理、与主计算机的高速数据传输接口等部分组成。其间,信号扩大是对输入信号进行调度 以满意采样的要求;信号滤波是避免信号发生“混叠现象”;信号采样是完结模仿信号的数字化;高速数字信号处理是在树立随机共振模型的基础上完结各种算法;与主计算机的高速数据传输接口是满意信号检测的实时性,将DSP处理的数据传给计算机以进行进一步的处理。

依据Verilog HDL规划的主动状况机由硬件操控A/D转化以

及主意向FIFO中存储数据,采样频率由DSP体系输出时钟确认,当采样数据到达一帧时,FIFO向DSP恳求间断,DSP体系发动DMA完结数据读取。这期间数据收集不间断,然后完结接连的实时数据收集和实时数据处理。数据收集体系由A/D芯片MAX196、逻辑操控芯片EPM7128、FIFO芯片CY7C425组成。操控逻辑用Verilog HDL言语描绘,并进行了仿零点和实践验证。

2 硬件电路规划

2.1 A/D转化芯片

体系A/D转化由MAX196芯片完结。MAX196的特色为:

①12位A/D转化精度,1/2 LSB线性度;

②单5V电源供电;

③软件挑选模仿量输入规模,别离为:±10V、±5V、0~5V、0~10V;

④6模仿量输入通道;

⑤6μs转化时刻,100ksps采样速率;

⑥内部或外部采样操控;

⑦内部或外部时钟操控转化。

在MAX196的操控字中:

①A2A1A0为通道挑选字:000~101别离代表经过0~5;

②BIP、RNG为输入规模和极性挑选;

③ACQMOD:采样操控形式,0为内部操控采样,1为外部操控采样;

④PD1、PD0为时钟与省电形式挑选。

内部转化形式时序如图2所示。当向MAX196写入包括通道挑选、量程挑选、极性挑选的操控字时,完结A/D转化的初始化。操控字的ACQMOD位用来挑选内部转化形式和外部转化形式,当写入ACQMOD位为0的操控字时,将发动内部转化形式,这儿选用内部采样形式,一次转化需求12个时钟周期,转化周期由芯片内部时钟确认。写入一个写脉冲(WR+CS)能够发动一次转化。当在A/D转化期间写入新的操控字时,将间断转化并发动一次新的采样周期。A/D转化完毕,输出低电平信号INT有用,信号RD读取A/D转化成果并复位INT信号,完好的一个转化周期完毕。

2.2 数据缓存器

体系收集的数据常常放在数据缓存器中。数据缓存区要求既要有与A/D芯片的接口,又要有与体系DSP的接口以进步数据吞吐率,因而常选用双口RAM或FIFO。因为FIFO不需求地址寻址,为了简化操控信号,本模块选用FIFO芯片CY7C425作为数据缓存区。FIFO存储器答应数据写入和读出不依赖于数据速率,而且总是以写入的次序读出。依据Full和Empty标志来判别存储器全满或空。FIFO芯片能够进行数据宽度和存储深度的扩展而不会添加额定的时刻延迟。当写信号(W)为低电平时发和写操作,当读信号(R)为低电平时发生读操作。A/D转化的成果经过写操作不断存入FIFO中,当FIFO满时,Full标志有用,向体系恳求间断,DSP呼应间断,当即发动DMA读FIFO中的数据,当读到空时,Empty标志有用,DSP中止读入操作。选用两片CY7C425扩展为18位1024字的高速异步FIFO存储器,数据处理速度到达50MHz,能够完结数据的高速写入和高速读出。FIFO异步读写时序见图3。

2.3 状况机模块

状况机(FSM)完结主动A/D转化和数据存储,操控芯片是EPM7128SQC100。该状况机由体系时钟驱动,发生RD、WR、INT信号,状况机能接连运转,不断地写指令字以发动A/D转化,然后读出A/D的转化成果并一起写入FIFO。时序图见图4。

复位时,发生写脉冲WR,芯片MAX196在WR的上升沿锁存外部输入的指令操控字,开端A/D转化。当A/D转化完毕时,芯片INT变为低电平,鄙人一个时钟的上升沿,RD变为低电平,数据总线上输出数据。当RD信号低电平有用时,INT信号变为高电平,下一个时钟的上升沿,RD信号变为高电平,在RD的上升沿数据被锁存进FIFO。RD信号回到高电平后,WR信号变为低电平,所以又开端下一次转化。

3 体系的Verilog HDL描绘

电子体系规划中一般遵从自上而下的规划思路,对体系进行规划、描绘与仿真。考虑到模块的通用性和可移植性,常常运用HDL言语来描绘数字体系,如Verilog HDL、VHDL、AHDL言语等。其间Verilog HDL言语具有结构明晰、文法简明、功用强壮、高速模仿和多库支撑等长处,被近90%的半导体公司运用,成为一种强壮的规划东西。

3.1 用Verilog HDL言语描绘MAX196

用Verilog HDL程序描绘MAX196模块,能够把模块用于收集体系的仿真,以验证状况机规划的正确性。该模块主要有三个输入信号和一个输出信号,与芯片的操控信号是共同的。程序阐明如下:

module adc(reset,rd_adc,wr_adc,int_adc);

input reset,rd_adc,wr_adc;

output int_adc;

reg int_adc;

always @(posedge wr_adc or negedge rd_adc or negedge reset)

begin

if(!reset)int_adc=1;

else if(rd_adc==0)begin int_adc=1;end

else begin #10 int_adc=0;end

end

endmodule

3.2 用Verilog HDL言语描绘主动状况机

主动状况机有三个输入信号和两个输出信号,输入信号中clk由DSP体系输出以操控采样速度,reset信号复位主动状况机,int_adc是A/D芯片转化完毕的呼应信号;输出信号rd_adc、wr_adc操控A/D芯片的转化开端和数据的读出,以及操控FIFO将数据写入FIFO。程序阐明如下:

module fsm(int_adc,clk,reset,rd_adc,wr_adc);

output rd_adc,wr_adc;

input int_adc,clk,reset;

reg rd_adc,wr_adc;

reg[1:0]present;

parameter reset_ad=2’h0,start_ad=2’h1,wait_ad=2’h2,read_ad=2’h3;

always @(posedge clk or negedge reset)

if(reset)begin present=reset_ad;rd_adc=1;wr_adc=0;end

else

begin

case(present)

reset_ad:if(rd_adc)

begin present=start_ad;wr_adc=1;end

start_ad:if(int_adc)

begin present=wait_ad:rd_adc=0;end

wait_ad:if(rd_adc)

begin present=read_ad;wr_adc=0;end

read_ad:if(int_adc)

begin present=reset_ad:rd_adc=1;end

endcase

end

endmodule

3.3 数据收集体系

MAX196模块和状况机模块组成高层模块——主动采样体系,经过模块实例的调用和端口映射句子完结模块的组合。特别设定输出信号int_adc,可使仿真波形看得愈加清楚。程序阐明如下:

Module simuadc(clk,reset,rd_adc,wr_adc,int_adc);//体系模块

Output rd_adc,wr_adc,int_adc;

Input clk,reset;

Reg rd_adc,wr_adc,int_adc;

Adc adcmax196(reset,rd_adc,wr_adc,int_adc);//A/D芯片模块

Fsm fsmasp(int_adc,clk,reset,rd_adc,wr_adc);//状况机模块

endmodule

3.4 仿真图形

图5为收集体系的时序仿真图。CLK是体系外部时钟,用于操控采样频率;RESET接外部复位信号,能够操控采样的开始时刻;MAX196的WR_ADC、RD_ADC、INT_ADC别离与逻辑芯片EPM7128的操控引脚相连接。仿真图标明,复位后,只需有CLK时钟输出,A/D转化将接连进行,转化数据顺次存入FIFO,当FIFO满时,向DSP宣布断恳求,DSP及时呼应并发动DMA高速读入FIFO中的值,因为DSP读入的速度足够快,因而A/D转化并不需求中止,然后完结实时采样和实时处理。

本文提出的主动收集体系选用CPLD芯片,用硬件描绘言语规划主动状况机,完结硬件操控数据收集和存储。现在收集体系运用于DSP运用板卡上,免去了DSP监控A/D芯片的时刻,使信号处理体系能高效地完结杂乱的随机共振体系的研讨。实践运用证明该收集体系作业十分安稳,若选用更高数据转化速度的A/D芯片、频率更高的体系时钟,能够进一步进步体系的数据收集速度。