一.运用布景

示波器作为基础性的通用时域仪器,广泛运用于电子相关范畴的丈量。一般示波器最多装备4个通道。而一些运用需求测验的通道数或许大于4个。例如多通道的高速串行总线(PCI Express x8,x16,x32)、DP-QPSK、天线阵列、相控阵雷达、卫星导航设备等等。这些运用有时需求在时域上收集多个信号,这就需求多通道且高带宽、高采样率的时域仪器。

为了完成更多收集通道,传统的做法是将多台示波器同步起来运用。所谓示波器同步,便是每台示波器的参阅时钟同源(相参)、触发时刻共同(收集时刻共同)。多台示波器同步办法如图 1,一个外部的时钟源输出到每台示波器,而且每台示波器由同一个信号进行触发。

图 1同步多台示波器衔接示意图

美国力科公司针对这类运用,推出了解决计划:多通道、高带宽、模块化示波器体系LabMaster,外观如图 2 所示。收集通道模仿带宽可达45GHz,采样率可达120G Sample/s,通道数则能够到达20个。

图 2 示波器体系LabMaster (左边为20通道,右侧为8通道)

多通道收集体系很大一部分运用的意图是测验各信号之间的时序或相位差,或许要求收集体系不影响信号之间的相位和时序联系。这要求收集体系具有比较高的同步精度,特别是关于一些高频、高速信号的测验,同步精度要求到达ps量级。能够按下面办法来评价收集体系的同步精度:将两个相位相同的正弦信号一起输入到收集体系恣意两个通道,通过收集后,丈量两个信号的相位差,这个相位差便是这两个收集通道之间的同步精度,或许称为时序偏斜(skew)、相位差错。

本文首要从同步精度的视点来比照传统的多台示波器同步方法和LabMaster示波器体系,

二.同步精度剖析

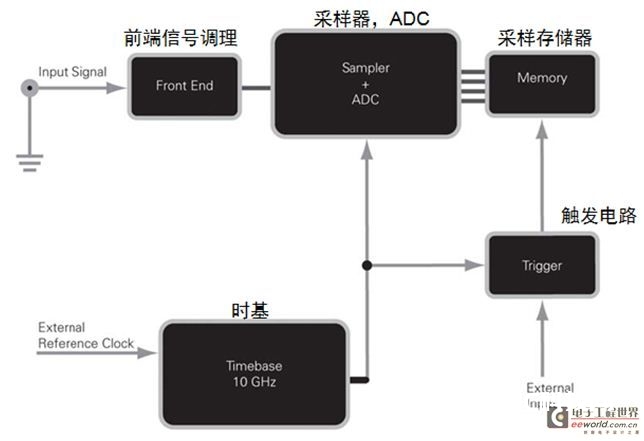

为了便于评论示波器的同步精度,先来剖析一下示波器收集电路的结构。单台示波器收集电路框图如图 3。信号先通过前端调度后,由模数转化器(ADC)进行量化。ADC由一个10GHz时钟驱动,称为时基(Timebase)时钟,产生时基时钟的电路称为时基电路。ADC量化的数据存入收集存储器(Memory)中,这是一个先入先出(FIFO)存储器,受触发电路操控。假如没有触发,收集存储器的内容不断被更新。假如触发条件到来,触发电路操控存储器中止更新,并把此时刻保存的数据送去显现和处理。随后康复更新,触发电路等候下一次触发条件。

图 3示波器收集电路框图

一台4通道的示波器,包括4套前端信号调度电路、ADC和收集存储器,它们共用一个时基电路和一个触发电路。

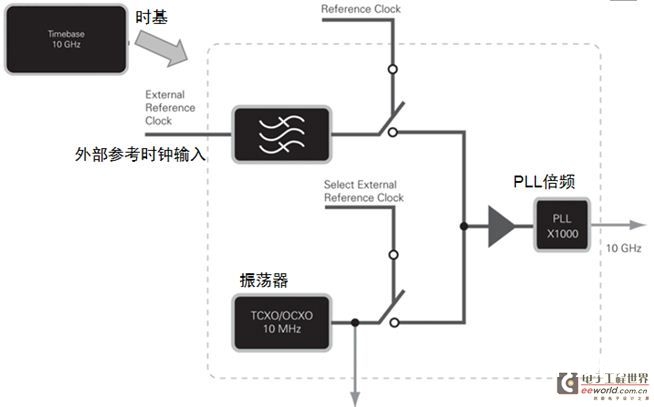

再将时基电路的结构细化,如图 4。10GHz时基时钟由一个10MHz的低频时钟通过PLL倍频1000倍得到,这个低频时钟称为参阅时钟,它能够由示波器内部的晶体振荡器(TCXO/OCXO)产生,也能够由外部输入(External Reference Clock)。内部产生的10MHz也能够输出给其他示波器。示波器一般都有参阅时钟的输入和输出接口,输入的时钟只能是低频,在内部还要通过倍频。

图 4示波器采样体系的时钟

把多台示波器同步起来运用时,示波器引进的时序偏斜首要包括以下部分:

时钟的偏斜和颤动

触发信号偏斜和颤动

通道推迟

1)时钟的偏斜和颤动

时基时钟通过散布网络传输到各通道ADC的推迟不免有差异,而每个通道的ADC都在时基时钟上升沿50%时刻进行采样和量化,这样各通道ADC采样时刻有误差。这种误差是固有的、静态的,能够通过校准的方法消除。但时钟难以避免颤动(jitter),颤动也会导致各通道采样时刻有误差,而且这种颤动是动态的、时变的,无法消除。只能挑选时基时钟颤动小的示波器。高带宽数字示波器一般都有一个标准目标称为颤动噪底(Jitter Noise Floor),该目标是时钟颤动、笔直噪声等示波器本身引进“搅扰”在终究测验成果上的方法的反映。例如力科四通道示波器WaveMaster 8Zi-A的颤动噪底为125fs。

单台四通道示波器的时基时钟颤动或许很小。但用同步方法完成多通道时,时钟颤动就很难操控在比较小的水平了。多台示波器同步需求一个额定的信号源输出10MHz时钟分配到每个示波器的参阅时钟输入接口,如图 1中的红线所示,也能够把一台示波器的参阅时钟输出给其他各台示波器。不管哪种参阅时钟产生方法,都需求一个时钟分配网络,这往往是测验体系集成者定制的,难以确保高安稳度,简单遭到噪声的影响。而低频的参阅时钟更简单受噪声影响。

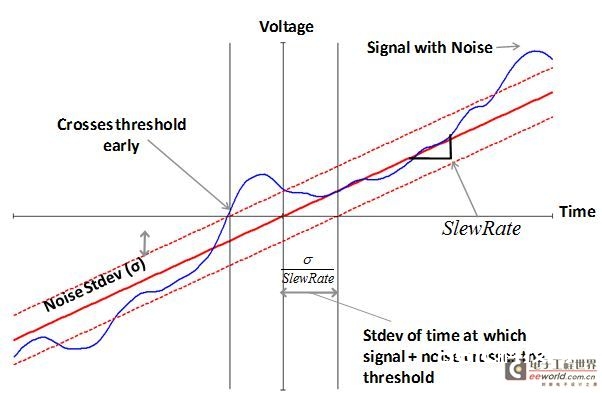

为什么低频时钟对噪声更灵敏呢?低频意味着信号摆率(slew rate)较小。信号摆率用来描绘信号边缘改变的快慢程度,数值上SlewRate=dv/dt,能够等同于边缘的斜率。相同起伏的时钟信号,频率低的边缘摆率小。因为噪声的影响,时钟上升沿50%电平的产生时刻或许提早或拖延,从而使起伏噪声转化为时刻颤动,如图5,转化联系为dt=dv÷SlewRate,这意味参阅时钟摆率越小,相同起伏噪声引起的颤动更大。

图5起伏噪声转化为时刻颤动

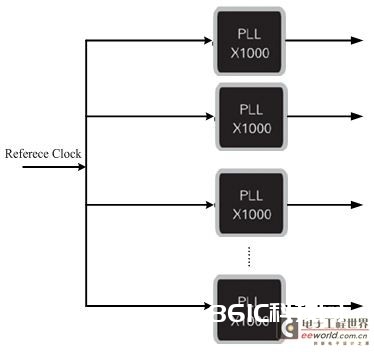

因为低频参阅时钟进入示波器后还需求通过PLL倍频才干作为ADC的采样时钟,所以多台示波器同步方法的时钟结构是如图6,一个参阅时钟一起输入到多个PLL,

图6多台示波器同步计划的时钟拓扑结构

一方面PLL倍频会加剧时钟的颤动。另一方面因为多个PLL输入并联在一起,它们之间彼此搅扰,也会加剧时钟颤动。

总结一下多台示波器同步方法的时钟颤动功能:外部输入的低频参阅时钟简单受搅扰,而且多个PLL倍频会加剧时基时钟的颤动,终究影响各个通道之间的同步精度。