晶振作业原理及参数详解

晶振又称石英晶体,是电子产品中最常用的元件之一,首要用于振动器电路中。晶振首要由晶片、导电胶、电极等器材组成,常见的HC49S、HC49U型晶振的结构示意图别离如图1、图2所示。

晶振的效果是为体系供给根本的时钟信号。一般一个体系共用一个晶振,便于各部分坚持同步。有些通讯体系的基频和射频运用不同的晶振,而经过电子调整频率的办法坚持同步。

晶振一般与锁相环电路合作运用,以供给体系所需的时钟频率。假如不同子体系需求不同频率的时钟信号,能够用与同一个晶振相连的不同锁相环来供给。

晶振是石英晶体谐振器(quartz crystal oscillator)的简称,也称有源晶振,它能够发作中央处理器(CPU)履行指令一切必要的时钟频率信号,CPU全部指令的履行都是建立在这个基础上的,时钟信号频率越高,一般CPU的运转速度也就越快。

只要是包含CPU的电子产品,都至少包含一个时钟源,就算外面看不到实践的振动电路,也是在芯片内部被集成,它被称为电路体系的心脏。

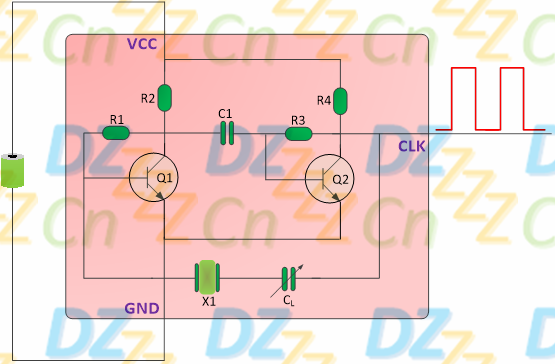

如下图所示的有源晶振,在外部施加恰当的电压后,就能够输出预先设置好的周期性时钟信号,

这个周期性输出信号的标称频率(Normal Frequency),便是晶体元件标准书中所指定的频率,也是工程师在电路规划和元件选购时首要重视的参数。晶振常用标称频率在1~200MHz之间,比方32768Hz、8MHz、12MHz、24MHz、125MHz等,更高的输出频率也常用PLL(锁相环)将低频进行倍频至1GHz以上。

输出信号的频率不可避免会有必定的差错,咱们用频率差错(Frequency Tolerance)或频率安稳度(Frequency Stability),用单位ppm来表明,即百万分之一(parts per million)(1/106),是相对标称频率的改动量,此值越小表明精度越高。

比方,12MHz晶振差错为±20ppm,表明它的频率差错为12×20Hz=±240Hz,即频率规模是(11999760~12000240Hz)

别的,还有一个温度频差(Frequency Stability vs Temp)表明在特定温度规模内,作业频率相关于基准温度时作业频率的答应违背,它的单位也是ppm。

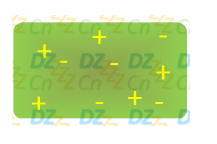

咱们常常还看到其它的一些参数,比方负载电容、谐振电阻、静电容等参数,是神马状况?这些与晶体的物理特性有关。咱们先了解一下晶体,如下图所示

石英晶体有一种特性,假如在晶片某轴向上施加压力时,相应施力的方向会发作必定的电位

相反的,在晶体的某些轴向施加电场时,会使晶体发作机械变形;

假如在石英晶片上加上交变电压,晶体就会发作机械振动,机械形变振动又会发作交变电场,虽然这种交变电场的电压极端弱小,但其振动频率是非常安稳的。当外加交变电压的频率与晶片的固有频率(与切开后的晶片尺度有关,晶体愈薄,切开难度越大,谐振频率越高)持平时,机械振动的起伏将急剧添加,这种现象称为“压电谐振”。

将石英晶片按必定的形状进行切开后,再用两个电极板夹住就构成了无源晶振,其符号图如下所示:

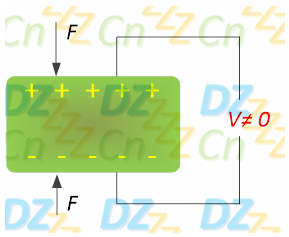

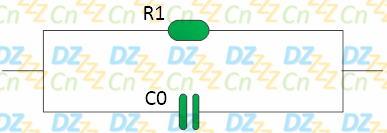

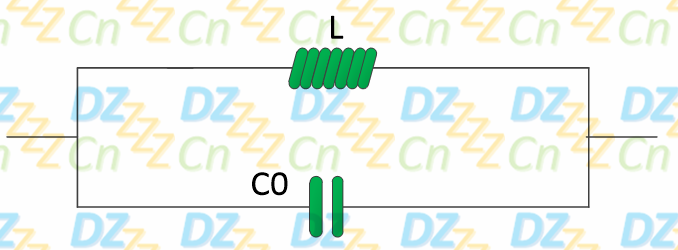

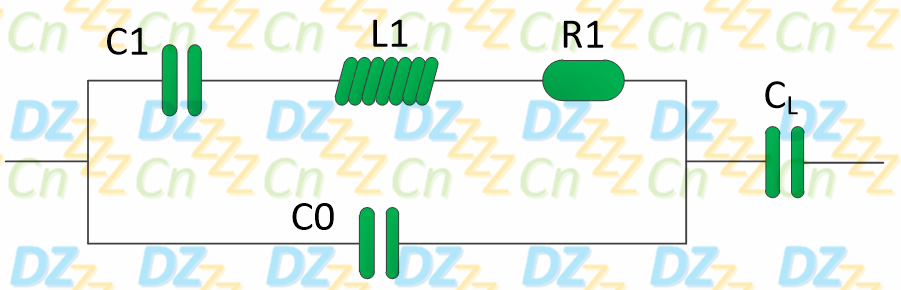

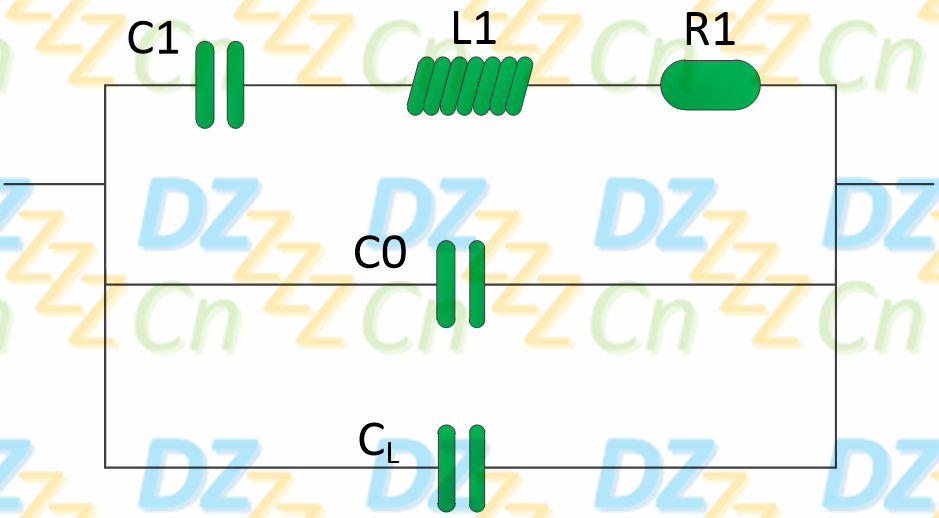

下图是一个在谐振频率邻近有与晶体谐振器具有相同阻抗特性的简化电路。

其间:C1为动态等效串联电容;

L1为动态等效串联电感;

R1为动态等效串联电阻,它是晶体内部冲突性当量

C0为静态电容,相当于两个电极板之间的电容量;

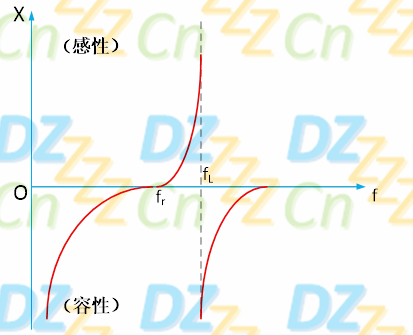

这个等效电路有如下图所示的频响特性曲线:

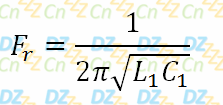

当R1、L1、C1串联支路发作谐振的频率即串联谐振频率(Fr),此刻容抗与感抗彼此抵消,因而,支路相当于只要等效串联电阻R1。

这个频率是晶体的天然谐振频率,它在高稳晶振的规划中,是作为使晶振安稳作业于标称频率、确认频率调整规模、设置频率微调设备等要求时的规划参数(但不是标称频率),其表达式如下所示:

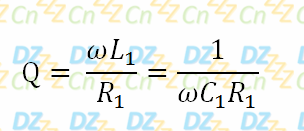

等效串联电阻R1决议晶体元件的质量因数,质量因数又称机械Q值,它是反映谐振器功能好坏的重要参数,它与L1和C1有如下联系:

R1越大,Q值越低,会导致频率不安稳,反之,Q值越高,频率越安稳,晶体的特色在于它具有很高的质量要素。

等效电路还有一个反谐振频率fL(并联谐振频率),此刻串联支路呈现为感抗,相当于一个电感,如下图所示:

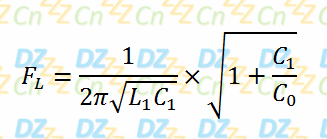

此刻的频率如下图所示:

一般厂家的晶振元件数据手册给出的标称频率不是Fr或FL,实践的晶体元件应用于振动电路中时,它一般还会与负载电容相联接,一同效果使晶体作业于Fr和FL之间的某个频率,这个频率由振动电路的相位和有用电抗确认,经过改动电路的电抗条件,就能够在有限的规模内调理晶体频率。

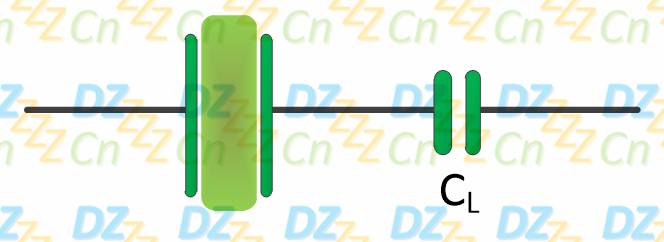

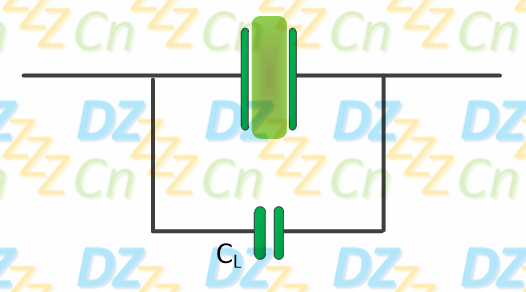

当负载电容与晶体串联时,如下图所示:

串接的小电容CL能够使石英晶体的谐振频率在一个小规模内调整,此刻新的负载谐振频率如下式所示:

其间,C1远远小于C0+CL

当负载电容与晶体并联时,如下图所示:

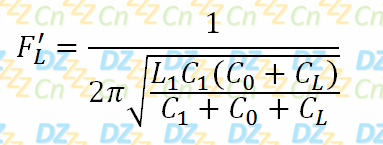

相同,并联的负载CL也能够小规模调整谐振频率,相应的负载谐振频率如下式:

从实践效果上看,关于给定的负载电容值,F’r与F’L两个频率是相同的,这个频率是晶体的绝大多数应用时所体现的实践频率,也是制作厂商为满意用户对产品契合标称频率要求的测验目标参数,也便是本文最最初介绍的晶振标称频率,

当晶体元件与外部电容相连接时(并联或串联),在负载谐振频率时的电阻即为负载谐振电阻RL,它总是大于晶体元件自身的谐振电阻。

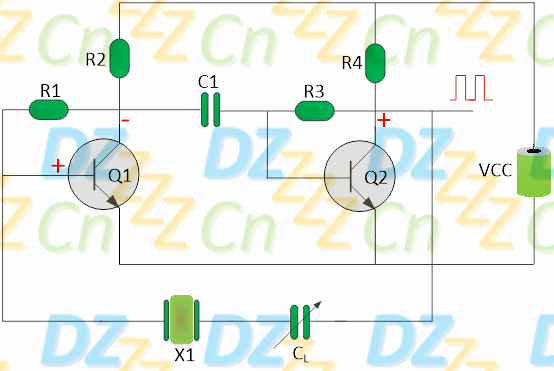

晶体自身是不能发作振动信号的,有必要借助于相应的外部振动器电路才干完成,下图是一个串联型振动器电路,其间,晶体管Q1、Q2构成的两级放大器,石英晶体X1与电容CL构成LC电路。在这个电路中,石英晶体相当于一个电感,CL为可变电容器,调理其容量即可使电路进入谐振状况,输出波形为方波。

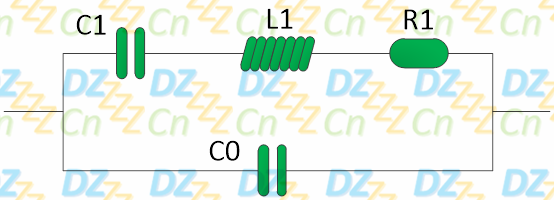

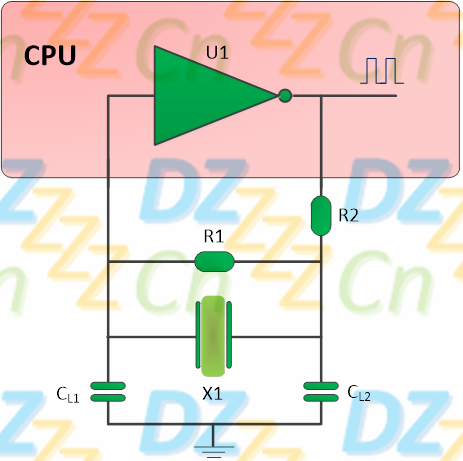

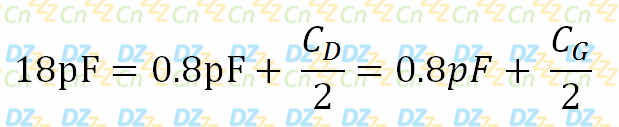

并联型振动器电路如下图所示,这种方式读者或许见得更多些,一般单片机都会有这样的电路。晶振的两个引脚与芯片(如单片机)内部的反相器相连接,再结合外部的匹配电容CL1、CL2、R1、R2,组成一个皮尔斯振动器(Pierce oscillator)

上图中,U1为增益很大的反相放大器,CL1、CL2为匹配电容,是电容三点式电路的分压电容,接地址便是分压点。以接地址即分压点为参阅点,输入和输出是反相的,但从并联谐振回路即石英晶体两头来看,构成一个正反应以确保电路继续振动,它们会略微影响振动频率,首要用与微调频率和波形,并影响起伏。 X1是晶体,相当于三点式里边的电感

R1是反应电阻(一般≥1MΩ),它使反相器在振动初始时处于线性作业区,R2与匹配电容组成网络,供给180度相移,一同起到约束振动起伏,避免反向器输出对晶振过驱动将其损坏。

这儿涉及到晶振的一个非常重要的参数,即负载电容CL(Load capacitance),它是电路中跨接晶体两头的总的有用电容(不是晶振外接的匹配电容),首要影响负载谐振频率和等效负载谐振电阻,与晶体一同决议振动器电路的作业频率,经过调整负载电容,就能够将振动器的作业频率微调到标称值。

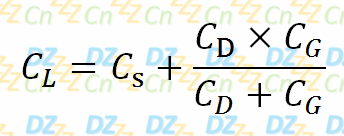

负载电容的公式如下所示:

其间,CS为晶体两个管脚间的寄生电容(Shunt Capacitance)

CD表明晶体振动电路输出管脚到地的总电容,包含PCB走线电容CPCB、芯片管脚寄生电容CO、外加匹配电容CL2,即CD=CPCB+CO+CL2

CG表明晶体振动电路输入管脚到地的总电容,包含PCB走线电容CPCB、芯片管脚寄生电容CI、外加匹配电容CL1,即CG=CPCB+CI+CL1

一般CS为1pF左右,CI与CO一般为几个皮法,详细可参阅芯片或晶振的数据手册

(这儿假定CS=0.8pF,CI=CO=5pF,CPCB=4pF)。

比方标准书上的负载电容值为18pF,则有

则CD=CG=34.4pF,核算出来的匹配电容值CL1=CL2=25pF

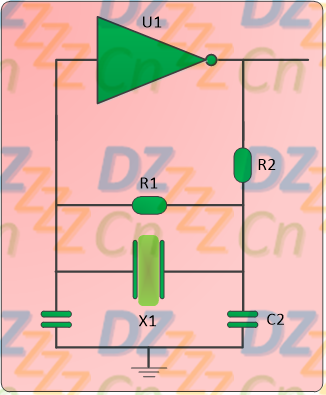

这么杂乱,我看不懂,我想用更简略更安稳更准确的器材,有木有?有!

有源晶振将一切与无源晶振及相关的振动电路封装在一个“盒子”里,不用手动准确匹配外围电路,不同的输出频率应用时,只需求收购一个相应频率的“盒子”即可,不再运用冗杂的公式核算来核算去,能够节约许多脑细胞做其它更多含义的作业。

封装后的“盒子”示意图如下所示: