1 导言

数字下变频DDC(digital down lonvwrsionl作为体系前端A/D转换器与后端通用DSP器材间的桥梁,通过下降数据流的速率,将低速数据送给后端通用DSP器材处理,其功用的好坏将对整个软件无线电体系的安稳性发生直接影响。选用专用DDC器材完结数字下变频,虽具有抽取比大、功用安稳等长处,但价格昂贵,灵活性不强,不能充分体现软件无线电的优势。FPGA工艺发展迅速,处理才能大大增强,相对于ASIC,DSP,其具有吞吐量高、开发周期短、可完结在线重构许多优势。根据这些长处,FPGA在软件无线电的研制中具有重要作用。

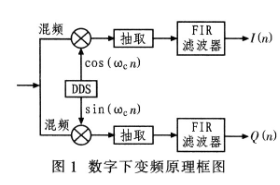

2 数字下变频体系

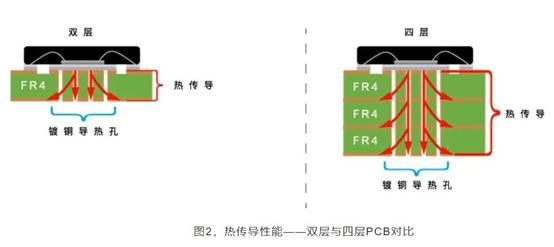

数字下变频器在软件无线电体系中完结的功用结构如图1所示,其间包含直接数字频率组成器DDS(direct digital synthesizer)、数字混频器、FIR滤波器、抽取等模块。原始模仿中频信号经A/D转换器带通采样后得到数字中频信号,输入DDC后先与DDS发生的两路正交本振信号相乘(数字混频),将数字中频搬移到基带。混频后得到的数据率和采样率共同,后级FIR滤波器要抵达该处理速率。硬件完结适当困难,因而首要通过抽取模块大大下降数据速率,然后运用高阶FIR低通滤波器对整个信道整形滤波。滤波输出的两路正基带信号交由下一级DSP器材进行处理。

2.1 混频器的FPGA完结

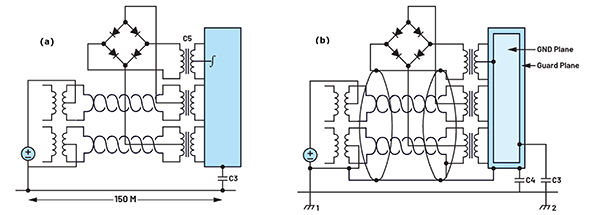

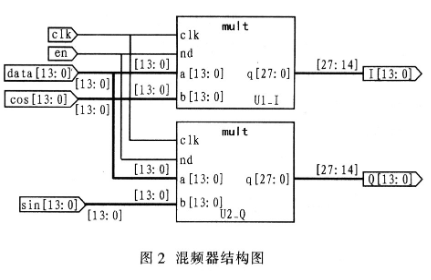

数字混频器将原始采样信号与查找表生成的正、余弦波形别离相乘,终究得到两路互为正交的信号。因为输入信号的采样率较高,因而要求混频器的处理速度大于等于信号采样率。单通道的数字下变频体系需求两个数字混频器.也便是乘法器。XC2V1000器材内嵌64个18×18位硬件乘法器,其最高作业频率为500 MHz,因而选用硬件乘法器彻底能够满意混频器的规划要求。运用Xilinx公司的Multiplier IP核能够轻松完结硬件乘法器的装备。该规划中选用两路14位的输入信号,输出信号也为14位。图2为混频器的结构图。

2.2 DDS的FPGA完结

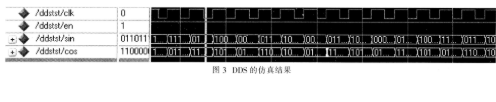

选用ISE中的IPCORE完结DDS,因为原始信号为60±7 MHz带通信号,通过100 MHz MD转换器发生一个中频为40 MHz的信号,将DDS输出频率设为40 MHz,发生频率为40 MHz两路正交I/Q信号,并与原始信号混频后发生两路零中频正交信号,完结下变频。其间DDS参数设置动态规模 (SFDR)为80 dB;频率分辨率(Frequency ResoluTIon)为0.4Hz;DDS输出频率(Frequency)为40 MHz。DDS的仿真成果如图3所示。

2.3 抽取模块的FPGA完结

经混频后,抵达抽取模块的是两路速率为100 MHz,位宽为14位的正交信号,为了更便利处理这两路正交信号,需下降信号速率。该规划中,依照4:1的份额抽取信号,抽取完结后,变为速率为25 MHz,位宽为14位的信号。

抽取模块的完结是在ISE中选用VHDL言语编写。首要对时钟4分频,将体系时钟100 MHz经分频变成25 MHz.再利用该25 MHz时钟操控两个D触发器.将经混频后速率为100 MHz,位宽为14位的两路I,Q正交信号别离作为这两个D触发器的输入信号,即可完结4:l抽取。经抽取模块后,信号变为速率为25 MHz,位宽为14位的信号。图4为分频的仿真波形。

2.4 FIR滤波器的FPGA完结

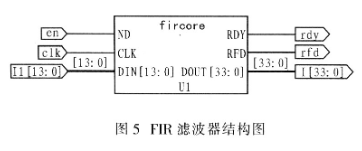

FIR滤波器也是由ISEIPCORE完结,因为经DDS后的信号是带宽为14 MHz的零中频信号,只考虑正频率规模,故PFIR的通带截止频率为7 MHz,在MATLAB中规划一个通带截止频率为7 MHz的FIR,将系数量化为14位二进制数值存入系数文件*.coe,将其导入FIR即可;FIR的阶数(系数长度)越高,功用越好,但考虑资源占用状况,FIR的阶数不宜过高,该规划选用35阶FIR。故FIR参数设置为:成果分辨率(Result ResoluTIon)为16位;滤波器阶数(Fiher Length)为35;系数精度(Precision)为14位。图5为FIR滤波器的结构。

2.5 FPGA器材选型

规划将对采样率为100 MHz的高速带通信号进行数字下变频处理,对体系的处理速度要求较高。因为Xilinx公司的FPGA处理速度较Ahera公司的更快,并且在体系安稳性和可操作性方面均优于Altera。考虑到数字下变频对体系的处理速度、可靠性、安稳性均有较高的要求.因而选用Xilinx公司的Virtex一2系列的XC2V1000器材。XCl2V1000器材内部包含1 280个CLB,每个CLB由4个Slice构成,共5 120个Slice,满意规划需求。

3 体系调试与成果剖析

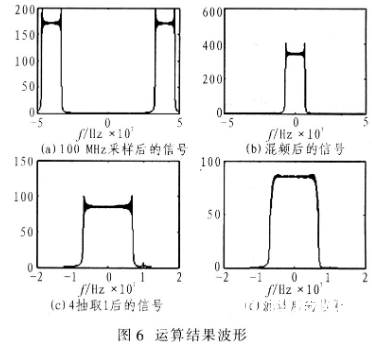

Xilinx的FPGA的开发东西为ISE,现在版本已更新到lO.2。ISE是一个集成的开发环境,包含HDL编辑器、IP—CORE Cenerator System、束缚编辑器、静态时序剖析东西、功耗剖析东西等十多种东西。这些东西能够协助规划人员进步作业效率。ISE能够便利集成第三方东西,如仿真东西Mod一elsim、归纳东西Synplify。此外Xmnx的东西Clfipseope能够在线调查FPGA内部信号波形,Plan Ahead东西能够通过简化归纳与布局布线间的过程,大大削减设计时间,与ISE结合运用时能够完结30%的功用提高。在ISE环境下选用VHDL言语完结DDC的各个模块。通过硬件调试,体系功用正常,将FPGA发生的各部分数据导入MARLAB中,得出的运算成果波形如图6所示。

DDC模块本来不改动输入信号的位宽,输入为14位,100 MHz的单路信号,输出本应为两路位宽14位,速率100MHz的零中频正交信号。而实践输出为两路位宽30位,速率100 MHz的零中频正交信号,所以先要截取该两路30位信号,康复至14位宽度,然后再抽取。经试验验证,在规划中,对两路(1/Q路)位宽为30位的信号进行13~26位截位,其作用最佳,信号质量功用都能得到确保。

4 结语

选用FPGA完结DDC,具有速度快,灵活性强等长处。该体系规划选用Xilinx的FPGA渠道,其间有许多免费的IP核可供选用,在完结较好功用的一起,可有用减小开发的周期和难度,因而,该规划方案具有广泛的使用潜力。

责任编辑:gt