导言:全新改版,关于MSP430x5xx时钟体系与低功耗形式介绍。用到低功耗的时分,不得不细心的看文档,做比较试验,真繁琐。

1. 时钟模块总览

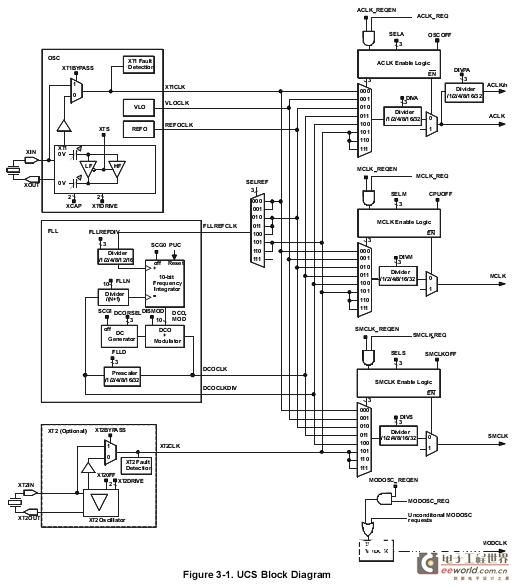

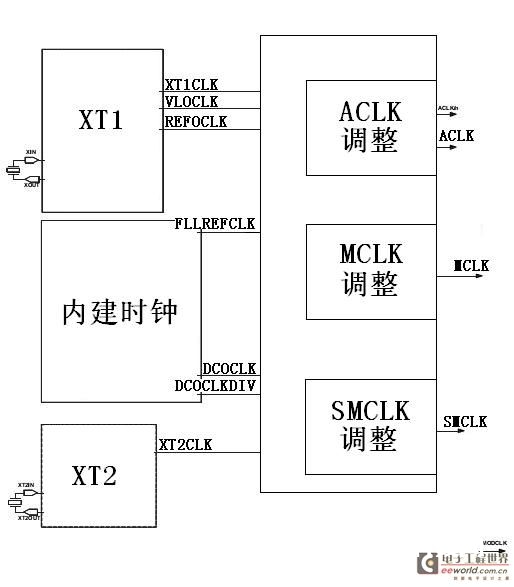

整个体系首要分为左右两大块,左面是时钟源模块,右边是时钟调整模块。

左面的模块——XT1、内建时钟(DCO)、XT2用来发生时钟源,也便是右边终究输出的时钟信号的基准信号。

而时钟调整模块担任将源时钟信号选通、分频输出成体系运用的三大时钟信号——MCLK,ACLK和SMCLK,分别是体系的主时钟(供CPU运用),辅佐时钟(可给外设模块运用,也能够从管脚引出),子体系时钟(外设模块时钟,可从管束引出)。

2. 调整模块

调整模块的首要作业分为两步:选通、分频。ACLK调整模块如下图所示

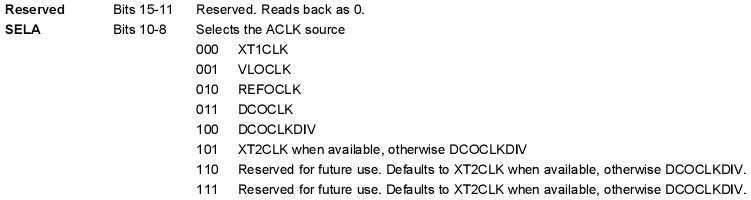

UCSCTL4 |= SELA_2;

// Set ACLK = REFO

这句话将ACLK的源设置为REFO。

SELA详细的意义如下图所示:

趁便说一句,TI的这个比如没有设置DIVA,用了默认值。

3.REFO、VLO和DCO

有了上述的了解,再参照slau208e,我信任不难写出咱们想要的代码。不过整个UCS中最有特征的部分还没有介绍,那便是REFO、VLO和DCO。

REFO是内建的参阅时钟,它很安稳,能够作为FLL的时钟基准(FLL是什么待会再说)。MSP430F5418上的REFOCLK是32.768kHz的。

VLO是一个内建的低频时钟。在5418上,它的频率是8.6kHz。

DCO是Digitally-Controlled Oscillator,数控晶振。它能够发生频率很高的时钟。经过装备,它能够发生百兆以上的时钟信号。在5418上,电压等级1的时分,不必XT2,有FLL(这个FLL究竟是什么呢?),我调出的最高频率是26MHz。