蜂鸣器是一种一体化结构的电子讯响器,选用直流电压供电,广泛应用于计算机、打印机、复印机、报警器、电子玩具、轿车电子设备、电话机、定时器等电子产品中作发声器材。在一般规划中,可利用蜂鸣器检测有些按键是否按下,或许有些功用是否正常等,当然假如满足浪漫,也能够让蜂鸣器演奏音乐。

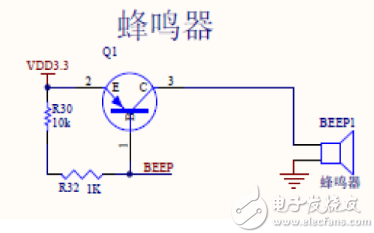

简略蜂鸣器电路图

本规划运用的是无源蜂鸣器,也可称为声响器,原理电路图如下所示。它没有内部驱动电路,无源蜂鸣器作业的抱负信号为方波,假如给直流,蜂鸣器是不响应的,由于磁路稳定,钼片不能轰动发音。

依据电路图可知,由于FPGA的驱动才能不行,这儿增加了一个三极管来驱动这个无源蜂鸣器。在驱动时,只需求向蜂鸣器发送必定频率的方波,就能够使蜂鸣器发声。那么应该发送怎样的频率呢?详细则可参阅下表(音节频率表):

乐曲能接连演奏所需求的两个根本数据是:组成乐曲的每个音符的频率值(腔调)和每个音符持续的时刻(音长)。因而只需操控FPGA输出到蜂鸣器的鼓励信号频率的凹凸和持续时刻,就能够使蜂鸣器宣布接连的乐曲声。

蜂鸣器音乐程序

在本规划中,由于至芯开发板的晶振为50MHz,所以咱们需求一个一个分频模块(PLL)发生一个较低的基准频率(1MHz)。还需求一个空间贮存曲谱,由于曲谱是固定的不需求更改,所以咱们挑选ROM IP 核进行存储。

基准频率1MHz可分频得到一切不同频率的信号。最大的分频比为1_000_000/262/2。既然是音乐,那么就需求节拍,一般选用4拍,即音长为0.25s,所以还需规划一个模块,操控每0.25s,ROM地址加1,。假如需求发送一个低声1并坚持1秒,则只需求在ROM的接连四个地址中写入低声1的对应信息即可。

在规划中为了方便在ROM中贮存数据,这儿数据格式为8’hAB,其间A暂时为三个值1、2、4,别离表明低声、中音、高音。B暂时为七个值1、2、3、4、5、6、7。比如要发生一个低声1,只需在ROM中存储8’h11,如要发生一个高音7,只需在ROM中存储8’h47,以此类推即可。这时,就需求一个解码模块,将ROM中的数据还原成音乐发生器所需求的数据。

规划架构图:

依据上述的剖析,得到如下的架构图:

本规划包含6个模块,PLL模块把50MHz的时钟信号降到1MHz,rom模块存储音乐数据,time_counter是一个计数模块,发生节拍,每到0.25s,输出的TIme_finsh变为一个周期的高电平。并发送给addr_gen模块,发生addr,让rom输出下一个地址的数据。rom输出的数据rom_data输入到decode解码模块,将解码后的数据music_data输入到music_gen模块,经过计数器,假如计数器小于music_data的值,则beep坚持不变,不然,beep取反,而且计数器清1,然后发生特定的方波频率。

规划代码:

TIme_counter模块代码如下:

0 module TIme_counter(clk, rst_n, TIme_finsh);

1

2 input clk, rst_n; //输入1Mhz时钟信号,复位信号

3 output time_finsh; //输出时刻计数标志位(没0.25s变高电平一次)

4

5 reg [17:0]count; //计数器count

6

7 always@(posedge clkor negedge rst_n)

8 begin

9 if(!rst_n)

10 count <= 18'd0; //计数器复位

11 else if(time_finsh)

12 count <= 18'd0; //每到0.25s计数器归零

13 else

14 count <= count + 1'd1; //未到0.25s,计数器持续累加

15 end

16 /*****每到0.25s,time_finsh拉高,表明现已到达0.25s*****/

17 assign time_finsh = (count== 18'd249_999)? 1'd1 : 1'd0;

18 /*****用于仿真,由于真实的0.25是会仿真很长*****/

19 //assign time_finsh = (count == 22'd25_00)? 1'd1 : 1'd0;

20

21 endmodule

addr_gen模块代码如下:

0 module addr_gen(clk, rst_n, addr, time_finsh);

1

2 input clk, rst_n; //输入1Mhz时钟信号,复位信号

3 input time_finsh; //输入时刻计数符号位(每0.25s变高电平一次)

4 output reg [6:0]addr; //输出给ROM的地址信号

5

6 always@(posedge clkor negedge rst_n)

7 begin

8 if(!rst_n)

9 addr <= 7'd0; //输出给ROM的地址信号复位

10 else if(time_finsh) //输出给ROM的地址信号自加1(每0.25s自加1)

11 addr <= addr + 1'd1;

12 else

13 addr <= addr; //未够0.25s,ROM的地址信号不变

14 end

15

16 endmodule

decode解码模块代码如下:

0 module decode(clk, rst_n, rom_data, music_data);

1

2 input clk, rst_n; //输入1Mhz时钟信号,复位信号

3 input [7:0]rom_data; //输入的ROM的数据

4 output reg [10:0]music_data; //输出ROM的解码数据

5

6 always@(posedge clkor negedge rst_n)

7 begin

8 if(!rst_n)

9 music_data <= 11'd0; //输出ROM的解码数据复位

10 else

11 case (rom_data)

12 8'h11 : music_data <= 11'd1911; //(1Mhz/261.63Hz)/2)=1191 低声1

13 8'h12 : music_data <= 11'd1702; //(1Mhz/293.67Hz)/2)=1702 低声2

14 8'h13 : music_data <= 11'd1517; //(1Mhz/329.63Hz)/2)=1517 低声3

15 8'h14 : music_data <= 11'd1431; //(1Mhz/349.23Hz)/2)=1431 低声4

16 8'h15 : music_data <= 11'd1276; //(1Mhz/391.99Hz)/2)=1276 低声5

17 8'h16 : music_data <= 11'd1136; //(1Mhz/440.00Hz)/2)=1136 低声6

18 8'h17 : music_data <= 11'd1012; //(1Mhz/493.88Hz)/2)=1012 低声7

19

20 8'h21 : music_data <= 11'd939; //(1Mhz/532.25Hz)/2)=939 中音1

21 8'h22 : music_data <= 11'd851; //(1Mhz/587.33Hz)/2)=851 中音2

22 8'h23 : music_data <= 11'd758; //(1Mhz/659.25Hz)/2)=758 中音3

23 8'h24 : music_data <= 11'd716; //(1Mhz/698.46Hz)/2)=716 中音4

24 8'h25 : music_data <= 11'd638; //(1Mhz/783.99Hz)/2)=638 中音5

25 8'h26 : music_data <= 11'd568; //(1Mhz/880.00Hz)/2)=568 中音6

26 8'h27 : music_data <= 11'd506; //(1Mhz/987.76Hz)/2)=506 中音7

27

28 8'h41 : music_data <= 11'd478; //(1Mhz/1046.50Hz)/2)=478 高音1

29 8'h42 : music_data <= 11'd425; //(1Mhz/1174.66Hz)/2)=425 高音2

30 8'h43 : music_data <= 11'd379; //(1Mhz/1318.51Hz)/2)=379 高音3

31 8'h44 : music_data <= 11'd358; //(1Mhz/1396.51Hz)/2)=358 高音4

32 8'h45 : music_data <= 11'd319; //(1Mhz/1567.98Hz)/2)=319 高音5

33 8'h46 : music_data <= 11'd284; //(1Mhz/1760.00Hz)/2)=284 高音6

34 8'h47 : music_data <= 11'd253; //(1Mhz/1975.52Hz)/2)=253 高音7

35

36 8'h00 : music_data <= 11'd0; //0HZ,中止节拍

37 endcase

38 end

39

40 endmodule

music_gen模块代码如下:

0 module music_gen (clk, rst_n, music_data, beep);

1

2 input clk, rst_n; //输入1Mhz时钟信号,复位信号

3 input [10:0]music_data; //输入音乐频率操控字

4 output reg beep; //输出方波

5

6 reg [10:0]data, count; //存放音乐操控字的data,计数器count

7

8 always@(posedge clkor negedge rst_n)

9 begin

10 if(!rst_n)

11 data <= 11'd0; //存放器data复位

12 else

13 data <= music_data; //data存放音乐操控字

14 end

15

16 always@(posedge clkor negedge rst_n)

17 begin

18 if(!rst_n)

19 begin

20 count <= 11'd1; //计数器复位

21 beep <= 1'd0; //输出方波复位

22 end

23 else if(data== 11'd0) //当data==11‘d0,(中止节拍)

24 begin

25 count <= 11'd1; //计数器归一

26 beep <= 1'd0; //输出方波归零

27 end

28 else if(count <= data) //当计数器小于等于data的值

29 count <= count + 1'd1;//计数器持续累加

30 else

31 begin

32 count <= 11'd1; //当计数器大于data的值,计数器归一

33 beep <= ~beep; //输出方波取反

34 end

35 end

36

37 endmodule

beep顶层模块代码如下:

0 module beep(clk, rst_n, beep);

1

2 input clk, rst_n; //输入50Mhz时钟信号,复位信号

3 output beep; //输出的方波

4

5 wire clk_1M, time_finsh; //1Mhz时钟信号线,0.25s时刻计数符号位

6 wire [6:0]addr; //rom地址线

7 wire [7:0]rom_data; //rom数据线

8 wire [10:0]music_data; //rom数据解码数据线

9

10 /*****PLL模块*****/

11 my_pll my_pll_inst(

12 .areset(~rst_n),

13 .inclk0(clk),

14 .c0(clk_1M)

15 );

16

17 /*****0.25s时刻计数器模块*****/

18 time_counter time_counter_inst(

19 .clk(clk_1M),

20 .rst_n(rst_n),

21 .time_finsh(time_finsh)

22 );

23

24 /*****ROM地址发生器*****/

25 addr_gen addr_gen_inst(

26 .clk(clk_1M),

27 .rst_n(rst_n),

28 .addr(addr),

29 .time_finsh(time_finsh)

30 );

31

32 /*****ROM模块*****/

33 my_rom my_rom_inst(

34 .address(addr),

35 .clock(clk_1M),

36 .q(rom_data)

37 );

38

39 /*****解码模块*****/

40 decode decode_inst(

41 .clk(clk_1M),

42 .rst_n(rst_n),

43 .rom_data(rom_data),

44 .music_data(music_data)

45 );

46

47 /*****音乐发生器模块*****/

48 music_gen music_gen_inst(

49 .clk(clk_1M),

50 .rst_n(rst_n),

51 .music_data(music_data),

52 .beep(beep)

53 );

54

55 endmodule

beep_tp顶层测验模块代码如下:

0 `timescale 1ns/1ps

1

2 module beep_tb;

3

4 reg clk, rst_n;

5 wire beep;

6

7 initial begin

8 clk= 1;

9 rst_n= 0;

10 #200.1 rst_n=1;

11

12 //#100000000 $stop;

13 end

14

15 beep beep_dut(

16 .clk(clk),

17 .rst_n(rst_n),

18 .beep(beep)

19 );

20

21 always #10 clk= ~clk;

22

23 endmodule

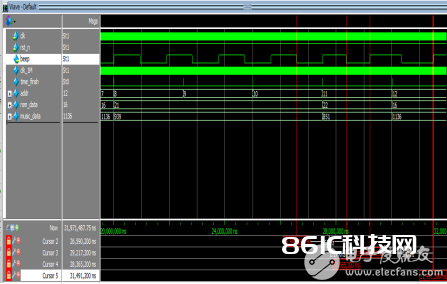

仿真图:

仿真成果如下:

由仿真图可知:当rom输出rom_data为8’h16时,代表输出低声6,解码后成果music_data为1136,输出的beep频率为440Hz,与实践低声6的音节频率表的值共同;当rom输出rom_data为8’h22时,代表输出中音2,解码后成果music_data为851,输出的beep频率为563Hz,与实践中音2的音节频率表的值相差24Hz,存在必定的差错,可是不影响乐曲的播映。假如想进步beep频率的精度,减小差错,则能够将1MHz的基准频率进步。