张 哲,余先银,张启辉(电子科技大学 电子科学与工程学院,成都 611731)

摘 要:依据经典的带隙基准电路原理,通过优化电路结构和选用寄生NPN晶体管,提出了一种能够下降运放失调电压和等效输入噪声影响的低噪声带隙基准电路。使用运放钳位流过晶体管的电流的份额,下降了运放失调电压和等效输入噪声至带隙输出电压的增益,完成了更安稳的基准电压输出。电路规划选用GSMC 0.18 µm工艺,通过Hspice仿真验证,在2.5 V电源电压下,基准输出电压为1.2 V;在(-40~125)℃温度范围内,基准电压温度系数为3.16×10 -5 /℃;在10 Hz处,噪声密度为2.67μV/ Hz √ ,低频下电源按捺比(PSRR)在95dB以上。

关键词:带隙基准电压源;下降运放失调电压影响;低噪声

0 导言

基准电压模块是数模转换器(DAC),模数转换器(ADC)、锁相环(PLL)等电路中不行短少的根本模块,其功能直接影响体系的精度和安稳性,其间带隙基准电路是使用最为广泛的一种基准电压模块。可是,因为规范CMOS工艺中运放的高失谐和高噪声现象,带隙基准电压的精度低,功耗大,而且带隙基准输出电压中包含了扩大的运放输入失谐和噪声,极大地约束了带隙基准电路在高精度电路体系中的使用 [1-3] 。

本文在剖析带隙基准电路原理的基础上,通过优化电路结构和选用寄生NPN晶体管,提出了一种能够下降运放失调电压和等效输入噪声影响的低噪声带隙基准电路。使用运放钳位流过晶体管的电流的份额,下降了运放失调电压和等效输入噪声至带隙输出电压的增益,完成了更安稳的基准电压输出。

1 电路规划

1.1 传统带隙基准结构

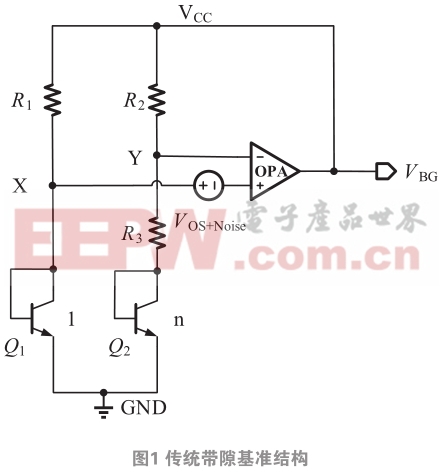

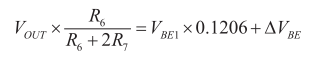

图1为传统带隙基准的等效架构图。在该电路中,运算扩大器用于钳位 V X 和 V Y 点电压,使得 VX=VY。

三极管的电压电流关系为:

图1中,R 1 =R 2 ,所以Q 1 和Q 2 的集电极电流持平,因为Q 1 只要一个“单位三极管”,而Q 2 为 n 个“单位三极管”并联,由式(1)可得到:

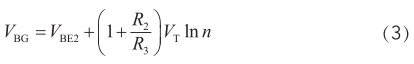

所以有VR3=VBE1-VBE2=∆VBE=VTln(n), 其间,ΔV BE 为不同三极管基极与发射极电压差的差值,由此得到的带隙基准电压V BG 为:

其间,R 2 和R 3 为同类型的电阻, n 为三极管Q 1 与Q 2的个数比。为了发生零温度系数的带隙电压,要求正温度系数和负温度系数彼此抵消,即式(3)中, VT的系数应为1.5/0.087=17.2,即 (1+R2/R3)×ln(n)=17.2,由此发生的带隙基准电压为V VBG≈VBE2+17.2×VT≈1.2V[4] 。

可是,因为在集成电路制作过程中不行避免会存在工艺差错,即便在规划时彻底对称的输入晶体管对,在制作完成后也会呈现不对称的现象,由此发生了运放输入为“零”而输出不为“零”的现象,该现象一般称为“失调”。一起,运放中各个MOS管发生的热噪声和闪耀噪声,也会极大地影响运放的钳位作用。集成电路领域中,一般将运放的失谐和噪声发生的影响折合到运放输入端,别离以等效输入失调电压 V OS 和等效输入噪声电压 V Noise 来表明,均以恣意极性叠加在运放输入端,以类似的办法对电路发生影响,在此用 V OS+Noise 来代表他们在运放输入端的全体值。

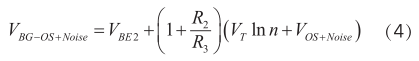

在图1所示的带隙基准电路中,考虑运放失调电压和噪声电压之后的输出电压为:

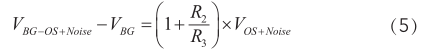

其间,V OS+Noise 为运放输入端的失调电压和噪声电压。那么由运放输入端失谐和噪声所引起的输出端电压的差错就等于:

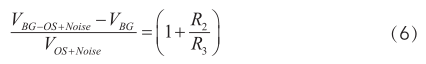

由此可见,运放输入端的失谐和噪声到输出端的电压增益等于:

即运放的失谐和噪声电压会被扩大(1+R2/R3)倍,然后在输出端引进较大的差错。假定要使 V OS+Noise 对输出的影响尽可能小,则需求(1+R2/R3)尽可能小,而依据式(4),在减小(1+R2/R3)时,有必要增大ln( n ),这样才干确保零温度系数电压的完成。当(1+R2/R3)=2时,则ln( n )约为8.5,由此核算得到的 n (晶体管个数比)为4 915左右 [5] 。

可是,过多数量的三极管会占用很大的芯片面积,使制作本钱添加,故上述核算得到的晶体管的个数(n=4 915)在集成电路规划中是不合理的(带隙基准电路中晶体管的个数大约在100以内)。一般晶体管的个数比为8,即n=8,由此可得ln(n)≈2.08,(1+R2/R3)≈8.3,导致运放的失调电压和噪声电压V OS+Noise 被扩大8.3倍;即便 n =100,依据式(4),运放的失调电压和噪声电压V OS+Noise 也会被扩大3.7倍。

由此可见,传统的带隙基准结构中运算扩大器的失调电压和等效输入噪声电压以极大的倍数扩大至带隙基准电压输出端,严峻恶化了基准输出电压的噪声和安稳性 [6-8] 。

1.2 下降失调影响的低噪声带隙基准电路规划

依据带隙基准原理,使用工艺中供给的寄生NPN晶体 管 , 提 出 由 N P N 晶 体 管 ( Q 1 和 Q 2 ) 、 电 阻(R1、R2、R3、R4、R5、R6、R7)、PMOS晶体管M1及运算扩大器OP1构成的基准中心电路,如图2所示。图中,Q 1 与Q 2 的发射极面积之比为1:8,电阻R3=R4,R2=R5。

电路功能剖析如下:

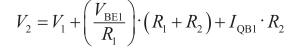

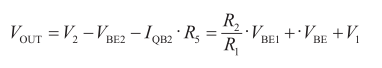

因为电阻R 1 两头的电压 VR1=VBE1,那么流过 R 1 的电流即为 IR1=VBE1/R1,由KCL有流过电阻 R 2 的电流IR2=IR1+IQB1,其间 I QB1 是流过NPN晶体管 Q1基极的电流。那么V 2 点的电压就等于:

流过 R5 的电流等于NPN晶体管 Q 2 的基极电流I QB2 ,那么带隙基准电路输出端电压 V OUT 等于:

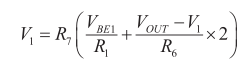

由KCL规律得,V 1 的电压等于:

收拾得到:

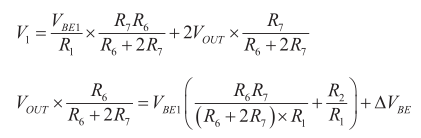

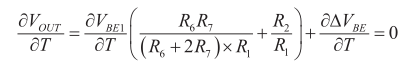

为了到达基准电压的零温度系数,要求:

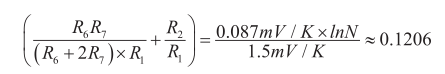

其间,晶体管的基极发射极电压 V BE 温度系数一般为 −1.5mV/K , 热 电 压 V T 的 温 度 系 数 一 般 为0.087mV/ K,核算得到:

那么:

在TT Corner下, V BE 为600 mV左右,即:

终究基准电压的值能够通过 R 7 和 R 6 的比值进行调理。

现在论述一下为什么这种结构能够有效地减少运放的噪声和失调对输出电压的影响:

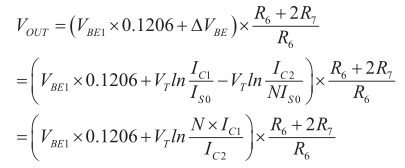

在抱负情况下,假定电路没有任何噪声,那么输出电压应该为:

现在假定运放存在等效输入噪声电压和等效输入失调电压,那么这个电压会导致流过 R 3 的电流发生动摇,然后使得IC1/IC2的份额发生动摇,然后影响到终究的输出电压 V OUT 。

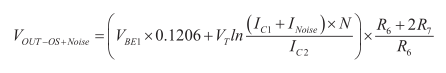

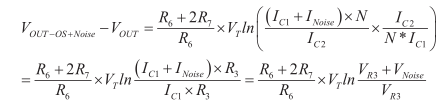

用 V OS+Noise 来代表运放的等效输入噪声电压和等效输入失调电压的全体影响,那么,在考虑运放的噪声和失调后,输出电压变为了:

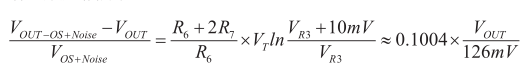

其间, ∆I Nois 是运放的噪声和失调作用于 R 3 时使I C1发生的动摇,即噪声电流。那么此刻,噪声引起的输出端电压的差错就为:

V R3 是DC下电阻 R 3 两头的压降。此可见,电阻 R 3和 R 4 上的压降决议了运放的噪声和失调对输出端电压的影响,电阻R 3 和R 4 上的压降越大,运放噪声到输出端的电压增益就会越低。假定DC下R 3 和R 4 的压降规划为250 mV,那么关于10 mV量级左右的失调电压,该电路的扩大倍数为:

关于10 µV量级左右的输入噪声电压,该电路的扩大倍数为:

可见,扩大倍数正比于终究的基准输出电压值,基准输出电压越高,扩大倍数越大。为了与传统结构的带隙基准电路进行合理的比较,核算该电路V OUT =1.2 V时的运放失调电压和运放噪声电压至基准输出的增益,别离为0.956 2倍和0.975 2倍,仅仅为传统结构扩大倍数8.3倍的11.5%和11.7%。

由此可见,在这种结构中,运放的失调电压和噪声电压折合到基准输出端时,均得到了极大地按捺,有效地下降了运放失调电压和噪声电压对基准输出电压的影响。

2 仿真验证成果

电路规划选用GSMC 0.18 µm工艺,通过Hspice仿真验证,在(-40~125)℃温度范围内,仿真成果如图3所示,核算可得带隙基准电压温度系数是3.16×10 -5 /℃。

图4所示为室温下基准输出噪声电压的仿真曲线(2.5 V电源电压,无任何滤波电路),在10 Hz处,噪声密度为2.67μV/ Hz √ ,在不添加任何功耗和电路复杂度的基础上,较大的减少了基准输出电压的噪声。

图5所示为带隙基准电路的电源按捺比曲线,低频下到达了95dB,高频下均在0dB以下,阐明电路具有杰出的电源噪声按捺才能。若要想持续进步该电路的高频PSRR,能够在输出端接入RC滤波电路,可是会添加电路的本钱和面积。

参考文献

[1]刘家楠,黄鲁.一种选用斩波调制技能的高精度带隙基准源[J].微电子学与核算机[J],2016,33(12):161-164.

[2]侯音.2.5V CMOS基准电压源的规划[[D];哈尔滨:哈尔滨工业大学,2010.

[3]Lv B,Wang P. A Low Noise and Low Temperature CoefficientCMOS Bandgap Reference for MEMS Micro-accelerometer[J].IEEE Journal of Solid-State Circuits,978-1-4244-5513-3/10/

[4]Leung K N,Mok P K T,Leung C Y. A 2-V 23-uA 5.3-ppm/’C Curvature Compensated CMOS Bandgap VoltageReference[J]. IEEE Journal of Solid state Circuits,2003,38(3):561-564.

[5]吴国平,黄年亚,刘桂芝.一种二阶曲率补偿带隙基准的研讨[J].电子器件[J],2005,28(3):696-698.

[6]Malcovati P,Maloberti F,Fiocchi C,Prnzzi M.Curvature-compensated BiCMOS Bandgap Reference[J]. IEEE Journal ofSolid state Circuits[J],2001,36(July): 1076-1081.

[7]Lee I,Kim G.Exponential Curvature-compensated BiCMOSBandgap References[J].IEEE Journal of Solidstate Circuits,1994,29: 1396-1403.

[8]IVanov V,Brederlow R,Gerber J.An UltraLow Power Bandgap Operational at SupplyFrom 0.75 V[J].IEEE,2012,47(7).

本文来源于科技期刊《电子产品世界》2019年第10期第62页,欢迎您写论文时引证,并注明出处。