现在比较盛行的低本钱、超小占用空间计划规划根本都是选用PSR原边反应反激式,经过原边反应稳压省掉电压反应环路(TL431和光耦)和较低的EMC辐射省掉Y电容,不只省本钱并且省空间,得到许多电源工程师选用。

下面结合实践来讲讲我对PSR原边反应开关电源规划的“共同”办法——以实践为根底。

要求条件:

全电压输入,输出5V/1A,契合动力之星2之规范,契合IEC60950和EN55022安规及EMC规范。因充电器为了便利带着,一般都要求小体积,所以针对5W的开关电源充电器一般都选用体积较小的EFD-15和EPC13的变压器,此类变压器按惯例核算办法或许会以为CORE太小,做不到,假如现在还有人这样以为,那你就OUT了。

磁芯以确认,下面就别离讲讲选用EFD15和EPC13的变压器规划5V/1A5W的电源变压器。

1.EFD15变压器规划

现在针对小变压器磁芯,特别是小公司根本都无从得知CORE的B/H曲线,因PSR线路对变压器漏感有所要求。

所以从对变压器作最小漏感规划下手:

已知输出电流为1A,5W功率较小,所以铜线的电流密度选8A/mm2,

次级铜线直径为:SQRT(1/8/3.14)*2=0.4mm。

经过丈量或查询BOBBIN材料能够得知,EFD15的BOBBIN的幅宽为9.2mm。

因次级选用三重绝缘线,0.4mm的三重绝缘线实践直径为0.6mm。

为了减小漏感把次级线圈规划为1整层,次级杂数为:9.2/0.6mm=15.3Ts,取15Ts。

因IC内部一般内置VDS耐压600~650V的MOS,考虑到漏感尖峰,需留50~100V的应力电压余量,所以反射电压需操控在100V以内,

得:(Vout+VF)*n<100,即:n<100/(5+1),n<16.6,

取n=16.5,得初级匝数NP=15*16.5=247.5

取NP=248,代入上式验证,(Vout+VF)*(NP/NS)<100,

即(5+1)*(248/15)=99.2<100,建立。

确认NP=248Ts.

假定:初级248Ts在BOBBIN上选用分3层来绕,因多层绕线考虑到出线空隙和次层以上不均匀,需至少留1Ts余量(空隙)。

得:初级铜线可用外径为:9.2/(248/3+1)=0.109mm,对应的实践铜线直径为0.089mm,太小(小于0.1mm不易绕制),不可取。

假定:初级248Ts在BOBBIN上选用分4层来绕,初级铜线可用外径为:9.2/(248/4+1)=0.146mm,对应的铜线直径为0.126mm,实践可用铜线直径取0.12mm。

IC的VCC电压下限一般为10~12V,考虑到至少留3V余量,取VCC电压为15V左右,

得:NV=Vnv/(Vout+VF)*NS=15/(5+1)*15=37.5Ts,取38Ts。

因PSR选用NV线圈稳压,所以NV的漏感也需操控,仍然按整层规划,

得:NV线径=9.2/(38+1)=0.235mm,对应的铜线直径为0.215mm,实践可用铜线直径取0.2mm。也可选用0.1mm双线并饶。

到此,各线圈匝数就确认下来了。

绕完屏蔽后,保TAPE1层;

再绕初级,按以上核算的分4层绕制,完成后包TAPE1层;

为减小初次级间的分布电容对EMC的影响,再用0.1mm的线绕一层屏蔽,包TAPE1层;

再绕次级,包TAPE1层;

再绕反应,包TAPE2层。 或许有人会说:怎样没有核算电感量?因前面说了,CORE的B/H不确认,所以得先从确认饱满AL值下手。

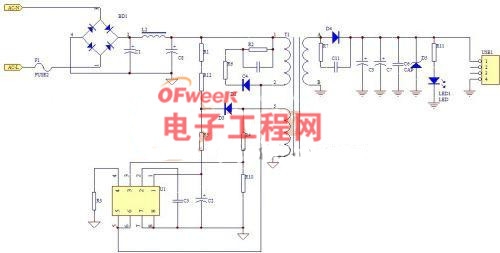

把变压器CORE中柱研磨一点,然后装上以上办法绕好的线圈装机,并用示波器检测Rsenes上的波形,见下图中R5。

输入AC90V/50Hz,渐渐加载,调查CORE有没有饱满,假如有饱满痕迹,拆下再研磨……直到负载到1.1~1.2A刚好呈现一点饱满痕迹。(此波形需把波形扩大到满屏调查最佳)

OK,拆下变压器丈量电感量,此刻所测得的电感量作为最大值依据,再依据厂商制作才能恰当留+3%~+5%的差错规模和余量,如:丈量为2mH,则取2-2*0.05=1.9mH,差错为+/-0.1mH。

现在再来验证以上参数变压器BOBBIN的绕线空间。

已知:E1和E2铜线直径为0.1mm,实践外径为0.12mm;

NP铜线直径为0.12mm,实践外径为0.14mm;

NS铜线直径为0.4mm,实践外径为0.6mm;

TAPE选用0.025mm厚的麦拉胶纸。

A.

NV若选用铜线直径为0.2mm,实践外径为0.22mm

线包单边厚度为:E1+TAPE+NP+TAPE+E2+TAPE+NS+TAPE+NV+TAPE

=0.12+0.025+0.14*4+0.025+0.12+0.025+0.6+0.025+0.22+0.025*2=1.77mm.

B.

NV若选用铜线直径为0.1mm双线并饶,实践外径为0.12mm

线包单边厚度为:E1+TAPE+NP+TAPE+E2+TAPE+NS+TAPE+NV+TAPE

=0.12+0.025+0.14*4+0.025+0.12+0.025+0.6+0.025+0.12+0.025*2=1.67mm.

丈量或查EFD15的BOBBIN的单边槽深为2.0mm,所以以上2种办法绕制的变压器都可行。

2.EPC13的变压器规划

仍然沿袭以上规划办法,丈量或查BOBBIN材料可得EPC13BOBBIN幅宽为6.8mm,

次级匝数为:6.8/0.6=11.3Ts,取11Ts.

初级匝数为:11*16.5=181.5Ts,取182Ts.

反应匝数为:15/(5+1)*11=27.5Ts,取28Ts.

EPC13的绕线办法同EFD15,在这里就不再重复了。

以上变压器规划出的各项差数是以操控漏感为起点的,各项参数(肖特基的VF,MOS管的电压应力余量……)都是零界或限值,实践规划中会因次级绕线同名端对应输出PIN位呈现穿插,或输出飞线套铁氟龙套管,或供货商的制程才能,都会使次级线圈削减1~2圈,对应的初级和反应也需依据匝比削减圈数;另,现在商场的竞赛导致制作商把IC内置MOS管的VDS耐压减小一点来节约本钱,为保存更大的电压应力余量,需再削减初级匝数;以上的修正都会对EMC辐射形成负面影响,对应的取舍还需权衡,但条件是有必要使产品作业在DCM形式。

从08年商场上推出PSR原边反应计划到现在我一向都有在用此计划规划产品,回忆看看,商场上也呈现了许多不同品牌的PSR计划,但相对曾经刚推出的PSR操控IC来说,有因商场反映不良而不断改进的部分,但也有由于恶性竞赛而COSTDOWN的部分。首要讲讲COSTDOWN的部分。

因受一些品牌在IC封装工艺上的专利约束,所以现在大部分的内置MOS的IC(不只是PSR操控IC,也包含PWM操控IC)选用的是在基板上置入操控晶圆和MOS晶圆,之间用金线作跳线衔接,这样就有2个问题产品了:

1.金线带来的EMC辐射。

2.研发操控晶圆的公司能够自己操控操控晶圆的本钱,但MOS晶圆一般选用的从MOS晶圆生产上购买,这样一来,MOS晶圆的本钱操控也成为IC本钱操控的案上肉。

辐射能够选用优化规划来操控。

但MOS晶圆的COSTDOWN的途径来源于下降其VDS的耐压,现在已有许多不同品牌的%&&&&&%将VDS为650V的内置MOS降到620~630V,乃至560~600V。这样一来,只操控漏感下降VDS峰值电压是不行的,所以还需为VDS保存更大的电压应力余量。

下面再以EPC13为实例,讲讲优化规划后的变压器规划。

办法同上,先核算出次级,因考虑到输出飞线套铁氟龙套管或输出线与BOBBINPIN位穿插,所以需预留1匝空间,得:次级匝数为:6.8/0.6-1=10.3,取10Ts.

再核算初级匝数,因考虑到为MOS管留更大的电压应力余量,所以反射电压取之前的75%

得:(Vout+VF)*n<100*75%

输出5V/1A,选用2A/40V的肖特基即可,2A/40V的肖特基其VF值一般为0.55V。

代入上式得:n<13.51,

取13.5,得NP=10*13.5=135Ts.

代入上式验证(5+0.55)*(135/10)=74.925<75,建立。

确认NP=135Ts.

下面再核算反应匝数,

仍然取反应电压为15V,

得,15/(5+0.55)*10=27Ts.

下面来确认绕线次序。

因要作业在DCM形式,且选用无Y规划,DI/DT比较大,变压器磁芯研磨气隙会发生穿透力强杂散磁通导致线圈测验涡流,影响EMC噪音,所以需先在BOBBIN上选用0.1mm直径的铜线绕满一层作为屏蔽,且引出端接NV的地线。