微机电(MEMS)陀螺广泛应用于航空、轿车自动化和消费类电子产品等范畴,依照振荡结构的不同,首要分为线振荡陀螺和旋转振荡陀螺。跟着MEMS陀螺本钱功耗不断下降、体积分量逐步减小,对其数字化计划也提出了新的要求如高精度、高采样频率等。为使MEMS陀螺能在高频率下作业,数字化电路就需求具有高采样频率,而现在MEMS陀螺的数字化首要是通过选用嵌入式现场可编程门陈设(FPGA)、数字信号处理器(DSP)芯片或许它们的组合来完结。

终究运用MEMS陀螺在该渠道上进行测验验证,使陀螺的信号解谐和操控能在PC端完结,实践的运用进程比一般的FPGA或许DSP愈加快捷。通过PCIe(PCIexpress)总线,完结PC和收集卡的高速传输,最大操控延时小于10μs.

1、计算机实时操控体系安稳低推迟优化规划

实时性作为陀螺测控体系的要害目标,本节将侧重规划和优化操控体系的低延时性和安稳性。榜首部分低推迟性优化首要包含硬件优化和软件优化。硬件优化需求考虑高速总线的类型和高速总线的传输操控方法;而软件优化则首要涉及到操作体系驱动层面的优化以及操控算法优化。第二部分安稳性优化是让计算机实时操控体系安稳地发生输出信号,在实践工程中则是防止该体系对陀螺设备的操控遭到中止延时和传输延时动摇的影响。

1.1、数据传输的低延优化

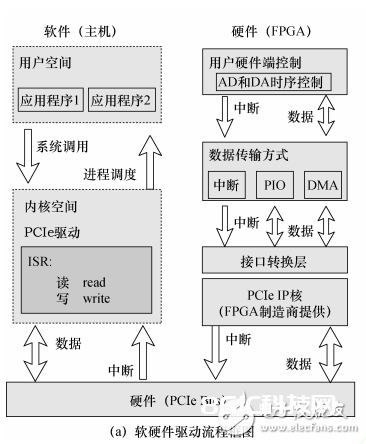

图1 实时测控渠道低推迟优化计划

图1a展现了实时测控渠道的软硬件结构和数据流向。硬件中止宣布后,AD收集到的数据需求通过接口转化层、FPGA的PCIeIP核、PCIe总线等才干抵达计算机IO内存空间。完结内存地址映射后,用户程序就可以从该内存读取数据,进行数据处理。在实践多线程的数据传输中,还会发生额定的延时,如图1b中所示,有中止延时、线程延时和线程上下文切换延时等。其间中止延时界说为计算机端硬件中止发生到中止服务程序(ISR)中榜首条指令履行的时刻差,首要与内核架构、CPU主频和负载有关。因为线程之间的调度,内核需求准备时刻,用于保存和康复线程上下文环境、获取或开释信号量等。线程延时界说为ISR中从发生唤醒正在等候的线程信号,到线程履行榜首条指令的时刻差。线程上下文切换时刻则为一个线程运转完到第二个线程榜首条指令履行的时刻差。