可重新装备的雷达体系选用FPGA和DSP制式的数字技能。数字技能与射频技能结合能够完结极高的灵敏度,习惯当时雷达运用对不同波形和装备的苛刻需求。因而,基带工程师团队一向运用与射频团队不同的规划办法和测验东西。不同技能的结合为体系集成测验带来了严重应战。

本文将介绍一个运用单一丈量渠道应对上述应战的办法。该渠道能够协助雷达体系集成商方便地验证和调试其规划。该办法支撑在雷达发射机或接收机途径中进行矢量信号剖析仪(VSA)丈量,以及结合逻辑剖析仪丈量FPGA硬件、结合示波器丈量模仿中频或射频电平、结合信号(频谱)剖析仪丈量射频鼓励器和接收机链路。三种仪器都能够导出捕获的信号并输入通用剖析环境,以协助规划人员查明混合信号链路恣意点或许存在的问题,终究成功完结体系集成。

线性调频雷达规划实例

脉冲紧缩是扩展雷达体系勘探间隔并提高分辨率的一个常用办法。对脉冲进行频率或相位调制,脉冲每个部分都将具有各自共同的频率或相位编码。凭借共同的频率和相位重量,咱们能够更轻松且更彻底地别离方针回波,扫除回波信号频域堆叠的搅扰。脉冲紧缩能够下降脉冲的峰值功率要求,并削减雷达脉冲被勘探到的概率。在整个脉宽内以“线性”方法对脉冲进行频率调制是一种脉冲紧缩类型。“线性”频率调制也称为“线性调频雷达”频率调制。

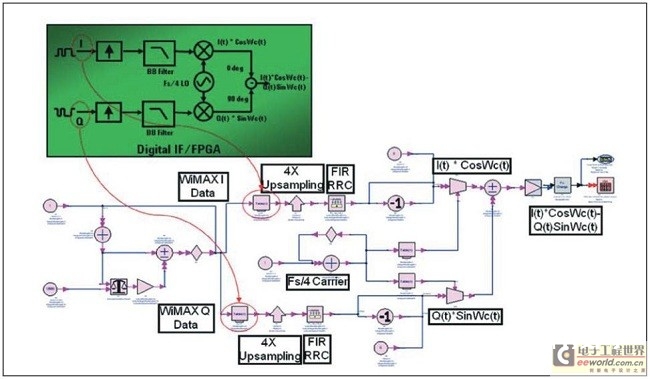

运用安捷伦的SystemVue能够获得高水平的雷达基带规划(参见图1)。生成I和Q矢量调制线性调频雷达信号,进行四倍因数上采样,运用根升余弦滤波并上变频至数字中频。运用SystemVue生成硬件描绘言语(HDL)代码,推进Xilinx Virtex-4 FPGA基带规划的FPGA完结。

图1:具有数字基带功用的线性调频雷达发射机部分。

然后,导出数字中频信号并输入数模转换器。终究,生成的模仿中频信号上变频至射频频率,经过功率放大器并由天线发射。

高档规划仿真

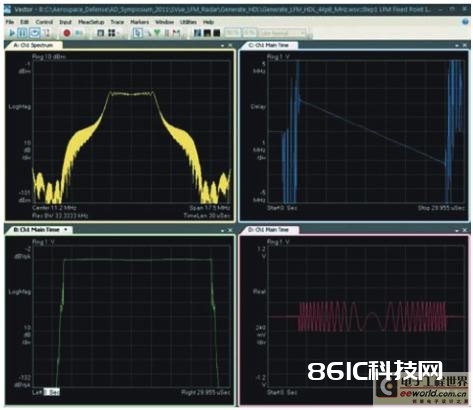

FPGA完结前可进行高档规划仿真。将仿真数字中频信号输入89600矢量信号剖析(VSA)东西(成果如图2所示)。在本例中,左上角面板显现的是需求的频率频谱内容,右上角面板显现的是整个雷达脉宽内的线性频移,左下角面板显现的是雷达脉冲幅度时域视图,右下角面板显现的是传统的数字矢量调制实部视图。四个视图是比较实在硬件测得信号的“黄金规范”。

图2:在VSA运用软件中解调仿真数字中频信号。

检查整个信号途径

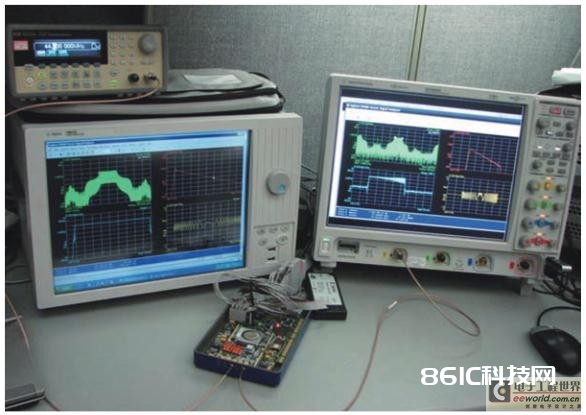

基带规划选用FPGA方法完结,因而在矢量调制途径中输入不同信号并结合逻辑剖析仪能够深化测验FPGA。测验设置如图3所示。左边为逻辑剖析仪,经过“飞线”将探头衔接至Digitech ExtremeDSP Xilinx Virtex-4渠道的0.1英寸头引脚。飞线探头能够为每个数字数据信号供给独立的同轴衔接。多个接地衔接能够保证勘探到的信号具有杰出的完整性。

图3:逻辑剖析仪勘探内部FPGA信号(L),示波器勘探数模转换器输出模仿中频(R)。两者都运转着VSA软件。

右侧为示波器,模仿中频信号经过SMB衔接器由DigiTech渠道的数模转换器输出,然后经由一条同轴电缆进入示波器。请注意,Xilinx USB JTAG编程电缆用于衔接Virtex-4 FPGA所在位置的JTAG链路。终究,JTAG衔接将用于切换FPGA内部的多路复用器,以经过内部FPGA路由资源获取所重视的信号。