前语 – LUCT是什么

第一层时钟树和第二层时钟树

时钟树规划及其规划办法是引起体系芯片功能差异的首要原因。

从前史视点看,ASIC时钟树规划人员运用商用主动化东西规划时钟树,以保证履行时刻等功能获得预期成果,可是,这种办法的时钟误差和刺进延时等功能却不尽人意,别的,高杂乱性、频率和尺度规划使得传统办法彻底没有可行性。

低不确定性时钟树[LUCT]规划及算法与在体系芯片上完结的第一层时钟树的物理界说有关,可以让规划人员战胜传统规划办法的一切低效率问题。

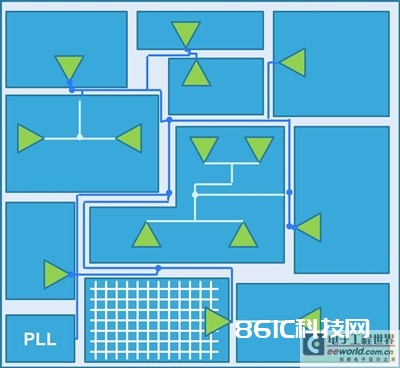

从顶层的根时钟网络(通常是PLL输出)到中层时钟网络,LUCT是一个高质量的负载均衡的时钟树,其方针是将时钟信号从中心锁相环PLL送到芯片的大部分区域,概况拜见参考文献[1]。该文献具体介绍了低不确定性时钟树[LUCT]办法和架构,归纳了从标准界说到单元布局和时钟组成的悉数相关规划流程。

依照参考文献[2]的界说,这种时钟分配办法归于结构化时钟树。文献[2]还归纳了现有的不同的时钟规划办法。从时钟源到寄存器,整个时钟树由第一层时钟树和第二层(或本地)时钟树组成。商用EDA东西需求完结本地时钟树。

LuctGenKit是意法半导体数字ASIC产品部的规划办法小组研制的时钟规划东西,可完结LUCT架构的物理完结进程。

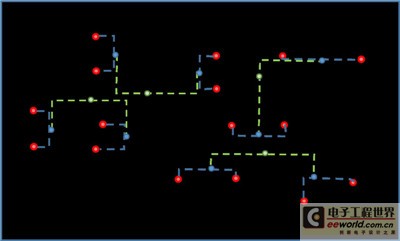

图1:在ASIC规划中优化时钟分配

LUCT东西首要特性

LuCT时钟组成东西供给LuCT办法中的一切重要特性:

o均衡的时钟树

-长度平等和主动负载匹配

-妨碍感知

-运用低电阻的高层金属层传输信号

-屏蔽和寄生匹配

o增强型订制单元库,满意各种信号强度需求

o支撑多种制作工艺,例如,32/28bulk,28fdsoi等

o模块布局,妨碍布局与避障

o与布局布线环境彻底集成

LuCT规划流程

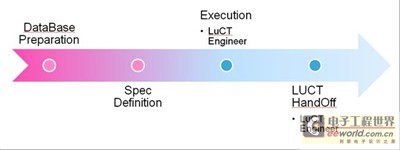

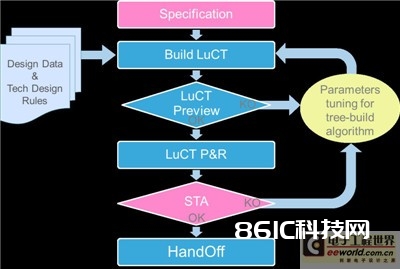

图2:LuCTgenKit规划流程

LuCTgenKit规划流程分为四个阶段,本文下面章节将给予具体评论。该东西可简化杂乱ASIC规划,在有多个工程师参加整个项目的物理完结的规划环境中作用特别显着。在一个典型规划安排内,物理完结的初始阶段是数据库预备和标准界说,最终阶段的作业首要是由专门的LuCT工程师来完结。一旦数据库预备和标准界说都完结后,仅一名LuCT规划工程师在一个作业日内即可完结整个顶层时钟树(或许不只一个时钟树)的完结和定案作业。

LuCT tool

数据库预备

数据库预备包括必要的规划查看、布局规划合理性验证、读取电源网格形状特点和布局布线东西。其间,布局布线东西用于衔接特别的增强型时钟库,并经过LuCT创立算法保证时钟库布局衔接。本阶段仍是使结构化时钟树运用现有技能获得最高功能的关键过程,特别是在下降电压降和抗串扰方面。

LuCT tool

LuCT标准界说

每一个时钟组成,都需求在该东西内输入下面信息:

o技能节点

o首要时钟树起点(PLL)

-X 和Y坐标

o首要时钟树结尾

-每个叶子上的X和Y坐标

o频率规模

o工艺-电压-温度角

o时钟单元参数挑选

规划人员可经过图形用户界面输入所需的悉数数据和规划办法。

LuCT tool

履行: 创立LuCT

低不确定性时钟树组成主动化东西绑缚下列目标:

-规划标准

-布局规划信息(包括布局妨碍和布线妨碍)

-电源网格

-规划和布局规矩

-网表

-布局

-图形用户界面

-陈述

-定案

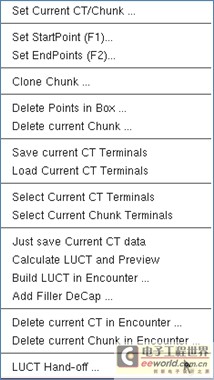

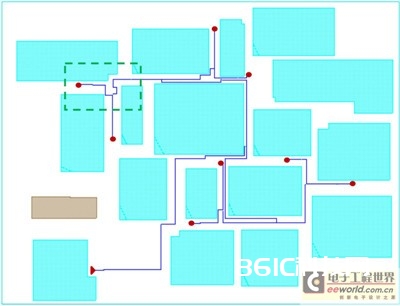

图3:LuCT应用软件图形用户界面菜单

LuCT东西经过意法半导体独有的算法生成时钟树拓扑。该算法根据均衡的途径长度和等长同质布线。芯片布局规划建模和初始化以及途径核算需求Lemon C++图形函数库[4]。时钟树创立进程包括下列过程:

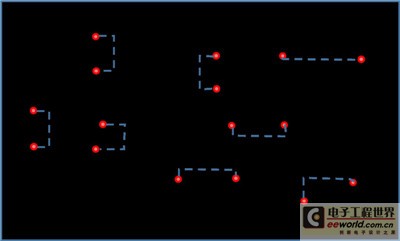

o网格生成: 在从布局规划读取数据后,生成妨碍模型和电源网格形状模型。从这些模型开端核算一个代表LuCT算法界说的布局布线间隔的点调集(网格)。

o构建二进制树:运意图法半导体独有算法将叶子分组,每组一对。经过核算长度平等的包括避障点的途径和兼并点(即该途径中心的一点)的办法将每对树叶兼并。经过这种办法依照递归办法兼并新的叶子(兼并点),直到只剩下一个点(树根)停止,详见图4到图6。

o刺进时钟驱动器和布线:刺进时钟驱动器和优化布线是选用一个自下向上的办法,别离考虑妨碍布局和妨碍布线。

图 4:结尾调集

图5:LuCT创立树算法配对决议计划与兼并

图 6:上一级发生的兼并点配对兼并

图7 :选用LuCT东西的规划流程

一旦生成时钟树结构,只要在布局布线CAD东西内运用脚本程序即可完结布局。关于多个并行时钟驱动器的高功能布线/走线、通孔布局和电源噪声感知布局,获得布局装备需求运用自界说规矩。

经过修正几个对二进制树架构和创立有很大影响的参数,可以优调算法。

下面是一些参数示例:

o叶子对生成:可主动或人工生成

o途径间隔核算:可以是纯Manhattan办法或可以感知妨碍

o弯折最小化:为布线网络挑选合适的招引力

o经过在每个布线/兼并阶段大局重映射中心,招引兼并区向现阶段的中心搬运

o时钟树功能指标:妨碍强度、时钟误差/刺进延时功能与妨碍的均衡性、时钟拥堵。

LuCT 东西

示例和成果

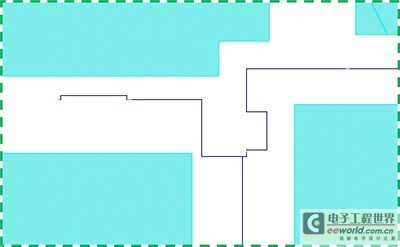

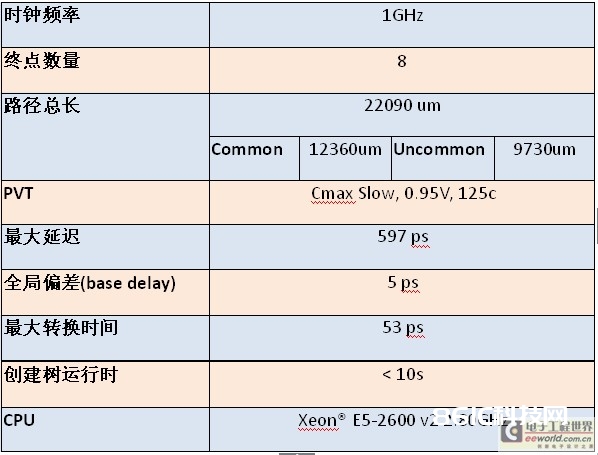

图8所示是依照上面评论的办法运用LuCTgenKit规划 28FDSOI芯片的时钟树。1GHz时钟信号从时钟源分配到8个树叶,避绕妨碍,平衡时钟误差,查觉妨碍。图9所示当衔接高层叶子对时怎么履行等长核算。

图 8

图 9

这个示例的首要结论是,依照基推迟(base delay)核算,时钟误差对错常有限的,不过,呈现很多的不常见途径。

时钟频率 1GHz

结尾数量8

途径总长 22090 um

Common12360umUncommon9730um

PVTCmax Slow, 0.95V, 125c

最大推迟 597 ps

大局误差(base delay)5 ps

最大转化时刻53 ps

创立树运行时< 10s

CPUXeon® E5-2600 v2 2.80GHz

表1:图8和图9的LuCT的数据和测验成果

参考文献

[1] Optimizing clock tree distribution in SoCs with multiple clock sinks

Alberto Ferrara and Pierpaolo De Laurentiis, STMicroelectronics

embedded.com

http://embedded.com/design/mcus-processors-and-socs/4409637/Optimizing-clock-tree-distribution-in-SoCs-with-multiple-clock-sinks-

[2] Myth busters: Microprocessor clocking is from Mars, ASICs clocking is from Venus

Kozhaya, J.;Restle, P.;Haifeng Qian

Computer-Aided Design (ICCAD), 2011 IEEE/ACM International Conference on

Digital Object Identifier:10.1109/%&&&&&%CAD.2011.6105340

Publication Year: 2011, Page(s): 271 –275

[3] Clocking Design Automation in Intel’s Core i7 and Future Designs

Ali M. El-Husseini and Matthew Morrise

Computer-Aided Design, International Conference on, pp. 276-278, 2011 IEEE/ACM International Conference on Computer-Aided Design, 2011

[4] LEMON Graph Library – Library for Efficient Modeling and Optimization in Networks

http://lemon.cs.elte.hu/trac/lemon

[5] The design and analysis of the clock distribution network for a 1.2 GHz Alpha microprocessor,

T. Xanthopoulos, D. Bailey, A. Gangwar, M. Gowan, A. Jain, and B. Prewitt,

Digest of Technical Papers IEEE International Solid-StateCircuits Conference (ISSCC 2001),

2001, pp. 402–403.

[6] Scalable sub-10ps skew global clock distribution for a 90nm multi-GHz IA microprocessor

N. Bindal, T. Kelly, N. Velastegui, and K. Wong,

Digestof Technical Papers IEEE International Solid-State Circuits Conference

(ISSCC 2003), 2003, pp. 346–347, 498.

[7] The clock distribution of the Power4 microprocessor

P. Restle, C. Carter, J. Eckhardt, B. Krauter, B. McCredie, K. Jenkins, A.Weger,and A. Mule,

Digest of Technical Papers IEEE International Solid-State Circuits Conference

(ISSCC 2002), vol. 1, 3–7 Feb. 2002, pp. 144–145

[8] Method of generating wiring routes with matching delay in the presence of process variation,

US Pat. 7865861

Habitz et al,

Filed 22 Apr 2008 – Issued 4 Jan 2011 – International Business Machines Corporation

[9] Method for the computer-aided ascertainment of a clock tree and Integrated Semiconductor Circuit, US Pat. 7707529

Heinz Endres, Thomas Zettler

Filed 13 Oct 2005 – Issued 27 Apr 2010 – Infineon Technologies AG

[10] Clocking Design and Analysis for a 600MHz Alpha Microprocessor

D.W.Bailey, B.J.Benscheider,

IEEE Journal of Solid-State Circuits, Vol. 33(11): pp.1627-1633, November 1998

[11] Automatic Synthesis of Clock Distribution Networks, US Pat. 8205182 B1

Zlatanovici et al,

Filed 22 Aug 2008 – Issued 19 Jun 2012 – Cadence Design Systems, Inc