简介

作为国内仅有一家具有彻底自主知识产权的FPGA与可装备运用渠道CAP(Configurable Application Platform)产品供货商,京微雅格一直在快节奏的改进与产品配套的软件开发环境。最近,新一代FPGA/CAP规划套件Primace5.0正式发布了。Primace5.0完好的支撑了依据时序驱动的布局布线完结流程(Timing-Driven PlacementRouting Flow),进步了布局布线的成功率,减少了规划与验证时刻。此外,Primace5.0还配套改进了Synopsys SDC兼容的规划束缚输入界面, 便利用户愈加精确高效的输入时序束缚。合作新式的主动寻觅最佳完结的优化东西iXplorer,Primace 5.0能够极大的加速用户规划时序收敛进程。为了便利用户精确描绘规划,改进RTL 代码质量,Primace5.0新增了RTL Template功用,其间包含了常用的Verilog规划元素。Primace5.0还第一次完好支撑了8051MCU的SoC仿真以及时序仿真(Timing Simulation)。相对上一代版别,新一代Primace明显改进了用户信息提示以及流程的安稳性。本文将扼要介绍这些改进以及对用户运用体会的影响,并引荐几种能够有用改进规划流程,加速规划进程的办法。

Primace5.0首要新增/改进的功用

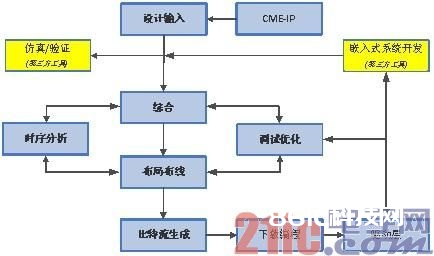

Primace5.0中底子规划流程坚持了一向的简练的特色,如图1所示,首要包含规划输入(RTL修正等),规划完结(归纳、布局布线等),时序收敛(以静态时序剖析为根底的规划、完结调整),以及码流下载和片上调试(DebugWare等)。

图1: Primace中FPGA/CAP开发流程

依据时序驱动的布局布线

时序驱动的布局布线是一种现已被广泛证明与承受的规划办法,规划人员经过描绘规划的时序束缚(包含中心频率束缚,I/O束缚,破例束缚,特定途径束缚,跨时钟域束缚等)能够有用辅导布局布线程序高效、高质量的完结规划完结。Primace5.0中承受的时序束缚包含:

Basic Timing Path

Clock Setup/Hold, Falling edge

Tsu/Th, Tco, Tpd

Advanced Timing Path

False path

Generated clock

User edited sdc

时序束缚输入辅佐

为了便利用户能够精确高效的输入时序束缚,Primace5.0还配套改进了兼容Synopsys SDC的规划束缚输入界面。如下图所示:

图2: 挑选时钟界面

图3:时钟束缚设置界面

各类SDC终究汇总在一致的SDC束缚文件里,用户能够会集修正:

图4:SDC修正界面

时序收敛东西iXplorer

合作新式的主动寻觅最佳完结的优化东西iXplorer,用户能够极大的加速规划时序收敛进程。

图5:iXplorer装备界面

Primace5.0对iXplorer进行了多项重要改进。首要,引入了支撑并行履行流程的新一代流程操控引擎,充沛的利用了干流多核体系的核算资源。其次,新开发的新式fMAX扫描算法Range-Scan,在充沛利用了并行核算优势的根底上,能够智能扫描时序束缚(现在首要是时钟频率束缚),用最短的时刻寻觅不同时序束缚下规划完结的最佳fMAX。此外,iXplorer支撑多种扫描完毕条件,便利用户在多种需求下的灵敏运用。终究,当用户得到最佳fMAX成果后,iXplorer供给了快捷的办法让用户把相应的束缚条件设置到用户环境,然后能够得到相应的成果。

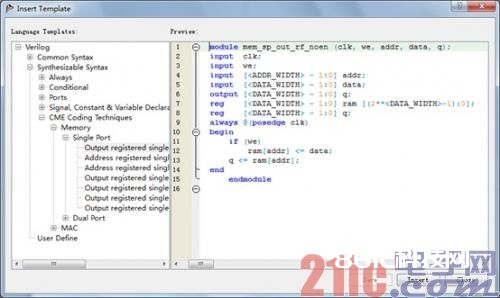

RTL模板

为了便利用户精确描绘规划,改进RTL 代码质量,Primace5.0新增了RTL Template功用,其间包含了常用的Verilog规划元素。经过运用RTL Template,用户能够便利快捷的在规划中刺进经过Primace软件验证的RTL代码,简化了用户规划输入进程并进步了规划代码质量。现在Primace RTL Template首要支撑了以下几类规划元素:

通用语法(注释,编译器操控语法等)

可归纳语法(现在仅支撑Verilog可归纳子集,以及Memory, Multiplier等能够主动揣度的代码形式)

用户自界说模板

图6:RTL模板阅览界面

SoC仿真与时序仿真

Primace5.0还第一次完好支撑了8051MCU的SoC仿真,以及时序仿真(Timing Simulation)。首要,经过简明易用的工程文件办理,便利用户对规划文件和测验渠道文件进行修正和办理;其次,引入了对8051MCU的SoC仿真支撑,彻底改动了曩昔调试8051MCU需求依靠第三方东西的调试形式,大大提升了用户SoC规划的调试功率,加速了用户SoC规划的整个验证和调试流程。终究,引入了对时序仿真的支撑,为处理用户规划中遇到的时序收敛问题供给了一条全新的剖析和调试的途径,加速了用户规划时序收敛的进程。

图7:仿真调用界面

流程及信息提示

相对上一代版别,新一代Primace明显改进了用户信息提示以及流程的安稳性。Primace 5.0对用户规划完结中各个阶段的流程信息从头进行了区分,将一切信息分为4类:指令信息,履行信息,正告信息和错误信息,对每一类信息逐条进行了编号,并引入了同类信息的折叠显现,便利用户经过流程信息了解规划完结的实时状况。此外,杰出的用户信息分类和显现也提升了流程日志的可用性,进一步便利用户了解规划完结的进程。

图8:信息提示界面

运用技巧

时序束缚设置办法

时序束缚设置底子能够遵从先全体后部分,先高层后低层的规则分阶段、分进程的逐渐细化设置。用户能够依照以下次序设置时序束缚:

中心频率束缚

经过束缚每个时钟的时钟频率以及相位联络,能够完结根底的中心频率束缚。现在Priamce5.0支撑的这类束缚包含Clock Setup,Clock Hold,Falling edge, Generated Clock。

I/O束缚

I/O束缚包含引脚分配方位、闲暇引脚驱动办法、外部走线延时(InputDelay、OutputDelay)、上下拉电阻、驱动电流强度等。参加I/O束缚后的时序束缚,才是完好的时序束缚。FPGA作为PCB上的一个器材,是整个PCB体系时序收敛的一部分。FPGA作为PCB规划的一部分,是需求PCB规划工程师像对待一切COTS器材相同,阅览并剖析其I/O Timing Diagram的。FPGA不同于COTS器材之处在于,其I/O Timing是能够在规划后期在必定范围内调整的;尽管如此,最好仍是在PCB规划前期给与充沛的考虑并归入规划文档。正因为FPGA的I/O Timing会在规划期间发生变化,所以精确地对其进行束缚是确保规划安稳可控的重要因素。许多在FPGA从头编译后,FPGA对外部器材的操作呈现不安稳的问题都有或许是由此引起的。现在Primace5.0支撑的这类束缚包含Tsu,Th,Tco,Tpd。

时序破例束缚

时序破例束缚能够指出在大局束缚下的特别途径调集,使得终究的时序束缚精确,严厉。正确的运用破例束缚能够进步时序剖析陈述质量,加速时序收敛进程。现在Primace5.0经过FalsePath来支撑时序破例束缚。

“好的时序是规划出来的,不是束缚出来的”,好的束缚有必要以好的规划为条件。没有好的规划,在束缚上下再大的功夫也是没有意义的。不过,经过正确的束缚也能够检查规划的好坏,经过时序剖析陈述能够检查出规划上时序考虑不周的当地,然后加以修正。经过几回“剖析-修正-剖析”的迭代也能够到达完善规划的方针。应该说,规划是束缚的底子,束缚是规划的确保,二者是相得益彰的联络。

依据iXplorer的时序收敛办法

时序收敛(Timing Closure)指时序的不断迫临,原理是选用屡次迭代(循环)的技能。因而时序收敛便是一个不断重复的进程,以确保规划中的每个途径都满意时序要求。iXplorer是京微雅格界说的,嵌入在Primace东西中的时序收敛规划流程。Primace有许多选项设置和战略,可是无法确保哪种选项或束缚会对一切的规划带来最佳的作用。iXplorer技能能够协助用户找到最佳的东西选项来完结时序要求或许找到规划的最高功能。iXplorer经过选用不同战略和选项来运转多个布局布线版别并找出满意时序要求的完结成果。现在iXplorer支撑三种查找算法来满意不同场景下的运用需求:

Target fMAX,用户指定希望的fMAX,发动iXplorer后,iXplorer开端测验不同束缚与选项,直到到达给定的fMAX中止。

Max Loop Count,用户指定最多iXplorer测验不同束缚与选项组合的次数,从给定次数的运转成果中找到最佳完结成果。

Ending Before Time,用户给定最晚完毕时刻,iXplorer会尽或许多的查找束缚与选项的组合,并在给定完毕时刻时中止。例如,用户能够设完毕时刻为第二天早上八点,然后鄙人班前发动,第二天上班时去检查成果。

iXplorer会用时序驱动的技能依据频率方针是否到达来加强或放松时序方针,这样就能够判别出所指定时钟域的最高频率约束。在优化完毕后,用户能够从iXplorer陈述中看到终究哪种战略和选项对现在的规划是最佳的。

总结

Primace5.0是京微雅格最新发布的FPGA/CAP规划套件。本文扼要介绍了Primace5.0包含依据时序驱动的布局布线等新功用,并针对时序收敛问题给出了两种依据Primace5.0的规划办法。限于篇幅,本文不能尽述Primace5.0对用户规划体会的改动,假如读者对Primace5.0有任何问题、定见或主张,请与京微雅格的出售支撑联络。