跟着工业生产与科学技能的开展,大型水轮机组的主动化水平也在不断提高。而这些设备一旦发生毛病,将会给人们的日子和生命财产形成极大的要挟。因而,对其工作状况进行监测,及时发现毛病预兆具有重要意义。现场可编程门阵列(FPGA,Field Programmable Gate Array )的出现是超大规模集成电路和核算机辅助规划技能开展的成果。它具有集成度高、多功用、低功耗、开发周期短等特色,并且能够很方便地对规划进行在线修正,因而获得了广阔用户的喜爱,运用规模也越来越广。本文首要介绍了ALTERA公司推出的低价位、高性能CYCLONE系列FPGA器材EP1C6Q的特色和内部结构,然后结合在水轮机组状况监测开发体系中遇到的实际问题,给出了相应的解决计划,终究就开发过程中遇到的一些实际问题,提出了自己的观点。

1、EP1C6Q的结构特色

EP1C6Q是ALTERA公司低价位CYCLONE系列FPGA的一种。它选用1.5V内核电压,内嵌92106位存储区间,可供给两个锁相环和双倍数据传输速率(DDR)的接口电路。其详细特色如下:

●选用240个引脚的FPQF封装方法,能供给185个IO用户引脚和5980个逻辑单元。

●具有20个4608位的RAM存储区,最高可支撑200MHz的数据传输。每个存储区均包含单口或双口RAM、ROM、FIFO等各类存储器件,并支撑8位、16位、32位、36位等数据存储类型。

●片上的锁相环电路能够供给输入时钟的1~32分频或倍频、156~417ps移相或可变占空比的时钟输出,输出时钟信号的特性可直接在开发软件QUARTUS2里设定。经过锁相环输出的时钟信号既能够作为内部的大局时钟,也能够输出到片外供其它电路运用。

●多功用的IO结构支撑差分和单端输入,并与3.3V、32位、66MHz的PCI部分总线兼容;IO输出能够依据需求调整驱动才能,并具有压摆率操控、三态缓冲、总线状况坚持等功用;整个器材的IO引脚分为四个区,每一个区能够独立选用不同的输入电压,并可供给不同电压等级的IO输出。

2、在水轮机组转速丈量中的运用

水轮机组的作业效率是体系状况监测中的一项重要目标,而机组的作业效率与当时时刻的转速密切相关。转速丈量的关键是对六十五路脉冲信号周期的丈量。选用了EP1C6Q器材内部的65个计数器一起作业的丈量方法。

2.1 水轮机组转速丈量原理

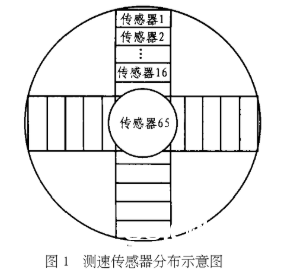

该水轮机组转速丈量设备如图1所示,它由六十五个微型机械传感器组成,其间六十四个传感器散布在对称的四个转轴上,第六十五个传感器在轴的中心交点。流经管道的水流将带动传感器的旋转。当传感器旋转一周后,触发电子线路发生一个脉冲信号。管道中水流的速度越快,脉冲信号的距离越短;管道中水流的速度越慢,脉冲信号的距离越长。这样?就能够依据脉冲信号的距离或者说两个信号上升沿的时刻长短来核算流速的巨细,然后依据相应的公式核算水轮机组转速的巨细。

2.2 全体规划计划及作业原理

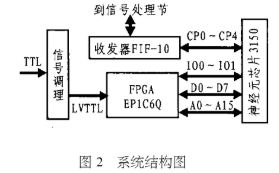

该水轮机组体系规划计划的全体框图如图2所示。水轮机组状况监测体系选用LonWorks现场总线技能,神经元芯片是构成体系收集节点的中心,它内部包含三个微处理器,即MAC处理器、网络处理器、运用处理器,而11个输入/输出引脚则可依据不同的外部设备来灵敏装备。收发器是节点之间通讯的桥梁。

因为水轮机组转速比较慢,传感器宣布的脉冲信号的时刻距离较长?因而?对缓变信号周期的丈量应选用测周的方法。首要是将输入的脉冲信号经去抖、限幅后变成契合EP1C6Q输入信号特性要求的信号,然后当EP1C6Q接到神经元信号的丈量指令后,再捕捉输入信号的上升沿。为了确保一切的通道在神经元芯片读取数据之前现已锁存,读取数据的时刻距离应确保不小于两个信号周期。神经元芯片将每个通道的计数值存储到片内RAM区,并将核算得到的转速值送到信号处理模块,以核算水轮机组的作业效率。因为流速丈量传感器的散布特色是边际传感器的信号周期比内部传感器的信号周期长,因而,笔者挑选一个最靠边的传感器作为标志传感器,并由标志传感器发生读取数据的标志位信号。

2.3 硬件完结

(1) 信号调度电路

因为EP1C6Q输入/输出逻辑高电平仅能支撑4.1V,而不能直接与规范的TTL电平信号相连,因而,神经元芯片和EP1C6Q之间的衔接以及脉冲输入电路都必须加限幅电路。芯片的规划现已考虑到与5V设备的衔接问题,其解决方法是在衔接线路中串接一个162Ω电阻。

(2) EP1C6Q和神经元间的物理衔接

在转速丈量模块中,EP1C6Q首要起信号边缘检测、脉宽丈量以及完结神经元芯片外围逻辑电路的效果。因为许多功用是在EP1C6Q内部运用软件完结的,所以二者之间的衔接很简略。操控信息的传递首要有两个途径:一是经过神经元芯片的I/O引脚,因为I/O引脚较长的树立时刻会影响体系的实时性,因而,规划电路仅运用IO0、IO1两个通道来作为整个体系的异步清零(clr)和读取数据标志(read_time);别的一个途径是经过神经元芯片的数据总线(D0~D7)和地址总线?A0~A15?,即在EP1C6Q的内部树立状况寄存器,并由神经元芯片向寄存器中写入不同的数据,然后由寄存器依据写入的数据来使相应的操控信号有用。

2.4 软件规划

a.EP1C6Q内部程序

EP1C6Q的内部程序是在QUARTUS2开发软件中完结的。QUARTUS2能够支撑原理图输入和硬件描绘言语两种编程方法。整个程序包含译码电路、分频电路、计数操控电路、计数器模块和数据的锁存和读取等五个部分。详细如下:

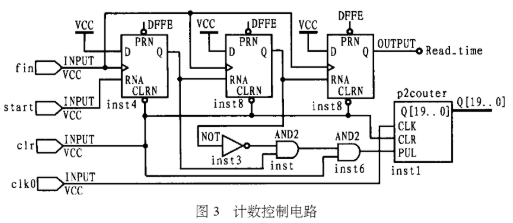

(1)计数操控电路

EP1C6Q内部的程序是在神经元芯片的操控下工作的。其操控部分电路如图3所示。信号fin代表六十五路脉冲输入信号的一路,clk0代表规范的计数时钟。在clr信号由低电平变为高电平、且start置为高电平后,脉冲信号fin输入有用。当第一个上升沿到来后,计数器的PUL引脚变为高电平,此刻,计数器开端计数;当第二个上升沿到来后,PUL变为低电平,计数器中止计数;而当第三个上升沿到来后,read_time信号变高电平,数据锁存。

(2)计数器的规划

因为水轮机组的转速比较慢,发生的脉冲信号频率一般在0.01Hz~10Hz之间,因而,转速快和转速慢时的信号周期不同比较大。为满意±1/10000个计数时钟的精度要求,计数器的计数位数应规划为20位。计数器的最大设定值为1000000,这样,当脉冲信号周期在10Hz~0.1Hz之间时,计数时钟为100kHz;而当脉冲信号的周期在0.1Hz~0.01Hz之间时,计数时钟主动转换为10kHz。计数时钟的主动切换是由计数器的溢出标志操控的,当计数器的计数值超出设定的最大值(1000000)后,溢出标志由低电平变为高电平,这样,经过大局时钟分频计数的时钟分频次数也会相应地扩展10倍,然后确保了计数器不会再次溢出。

(3)状况寄存器规划

为了减小神经元芯片操控功用对IO引脚的依靠,EP1C6Q在其内部树立了两个状况寄存器。这两个状况寄存器可依据神经元芯片写入的操控字来使相应的操控信号有用。运用的操控信号如下:

start:经过神经元芯片要求EP1C6Q进入信号收集状况操控,高电平有用。

lck:数据锁存信号,低电平有用。当EP1C6Q的输出信号read_time有用后,神经元芯片向状况寄存器写入指令字以使lck信号有用。为了确保一切通道的计数器现已中止作业,神经元芯片接收到read_time后将推迟ΔT时刻后再锁存计数器的数据。

h1?h2:计数值高八位、中八位、低八位的挑选操控。为了满意体系要求的丈量精度, EP1C6Q内部选用二十位计数器对每一路信号进行计数,而神经元芯片的数据总线是八位,因而需求分三次读出。

(4)译码电路规划

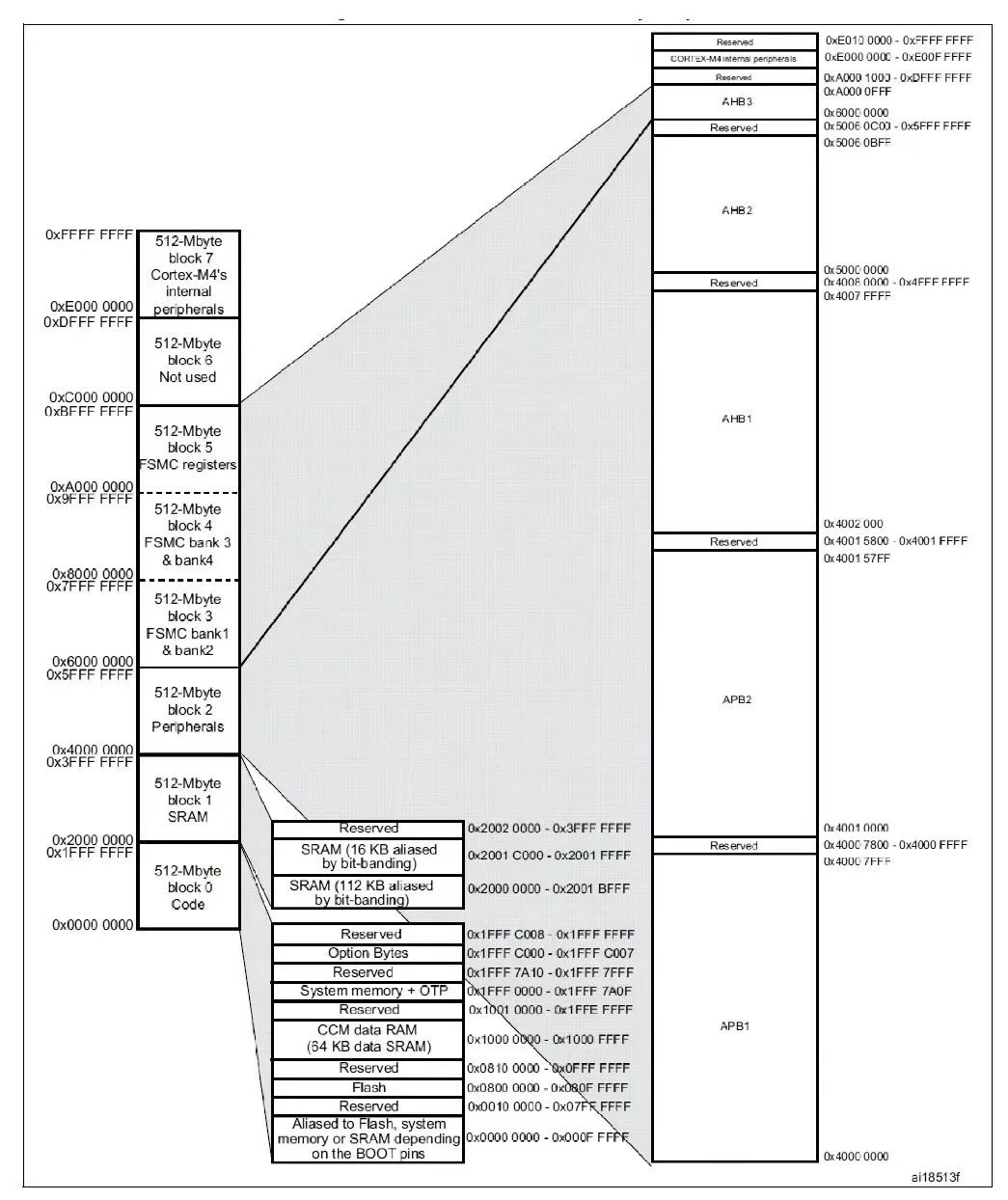

神经元芯片一般选用内存映象法进行数据的传递。所谓内存映象法,是指给芯片外部的寄存器、存储器或IO单元分配一个物理地址,以便于对外设操作,这相当于对该物理地址的操作。译码电路首要供给FLASH、状况寄存器和六十五个计数器的片选信号。体系的地址分配如下:

E800~EFFF?数据存储区,用于保存各个通道的计数值。

0000~7FFF?外围FLASH区。

8000~8040?六十五个计数器的内存地址。

8041~8042?状况寄存器的内存地址。

8042~E7FF?用户备用空间。

(5)分频电路

计数器单元的计数时钟是把输入的大局时钟分频得到的。12MHz的有源晶振输出一般可作为大局时钟,分频电路选用VHDL言语规划,分频次数设定值的改换由计数器的溢出标志操控。

b.神经元芯片的内部编程

本编程规划首要用于完结与体系的同步和操控EP1C6Q程序的工作。当接到信号处理模块发来的数据恳求信号后,该程序将发动EP1C6Q内部程序并开端计数,以将终究的计数值读到内部RAM区。

3、注意事项

在整个规划计划的完结过程中,应细心考虑以下两点:

第一是芯片的挑选。与一般电路开发不同的是,本规划计划的前期编译和仿真验证不需求拘泥于某一详细型号的芯片,只需满意计划所需的逻辑单元的数量、操控时序的精度和存储区间的巨细等要求,就能够在软件开发工具中编译仿真。可到计划成熟后,再考虑一些细节问题,如芯片以及所需电源和装备芯片是否简略买到,供给的IO接口类型是否满意需求,芯片的封装方法是否会影响到PCB板的制造等问题。

第二是时序电路和组合电路的转化。在一个体系中,时序电路和组合逻辑电路一般一起存在。两种类型的电路都作为输入时,为防止毛刺现象,能够在组合逻辑的输入之前加D触发器,以将组合逻辑电路转化为时序电路。在多级时钟体系中,为了满意树立和坚持时刻的要求,往往需求在低频时钟信号驱动的逻辑电路的输出端加一级高频时钟信号驱动的D触发器,以完结时钟之间的同步。但这样做会添加输入和输出之间的时刻推迟,严峻时或许通不过编译软件的时序验证。因而,能够将其转化为简略的组合逻辑电路,以使其比较简略完结。

4、结束语

该计划现现已过了试验验证,丈量成果能够满意规划要求。考虑到本钱问题,挑选的芯片不能与5V体系直接相连,这使得多路输入信号给整个电路的规划带来了必定的困难。假如扫除这些要素,该计划还能够得到进一步的改进。

责任编辑:gt