AD转化,也叫模数转化,是将模拟信号转化为数字信号。现在包含电脑CPU,ARM,FPGA,处理的信号都只能是数字信号,所以数据信号在进入处理芯片前必需求进行AD转化。

在高速的AD转化中,FPGA以其高速的处理才干,并行的运转结构,丰厚的IO资源,往往承当者不行代替的效果。

下面给出一个实践的规划计划。

AD芯片的时钟为25M,FPGA内部体系时钟频率为100M,FPGA内部处理AD数据的处理模块需求8个时钟周期才干处理完一个数据。

依据上述给出的条件,咱们可以知道。按正常思路规划计划,肯定会形成AD数据的丢掉,为什么会丢掉数据,试想一下,FPGA处理一个数据需求8个时钟周期,才干收集下一个数据,这样算下来AD需求的时钟是12.5M,而给定的AD时钟是25M,所以肯定会漏掉数据。

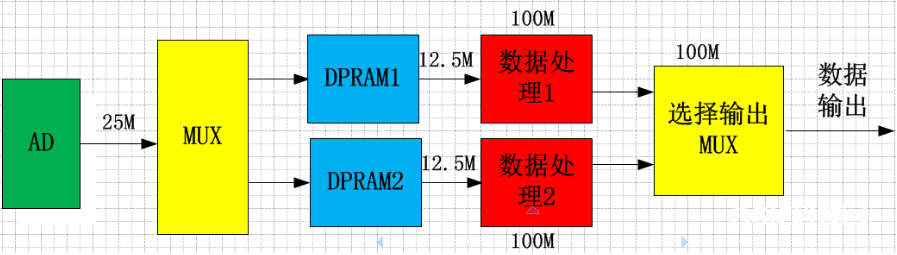

依据剖析,可以选用乒乓操作经过缓存下降数据采样率。

乒乓操作如下图:

详细乒乓操作为什么可以下降数据速率,这儿将不做详细介绍。

以上计划可以满意上述处理AD数据的需求。

紧接着持续增加需求条件,要求数据处理需求接连,不能打乱次序,前面数据的处理睬影响后续数据处理。这样乒乓操作将不合适,详细原因,读者可以自己想一下(乒乓操作会以数据块打乱数据次序)。

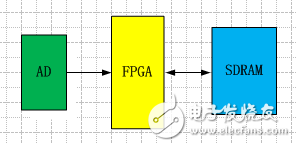

依据上述条件,规划计划需求修正。可以外加存储器,FPGA片上存储器资源有限。

增加SDRAM进步存储速度和存储量。

持续增加需求,假如AD数据接连不断,那么势必是形成SDRAM溢出。那么上述规划计划也不行采取了。

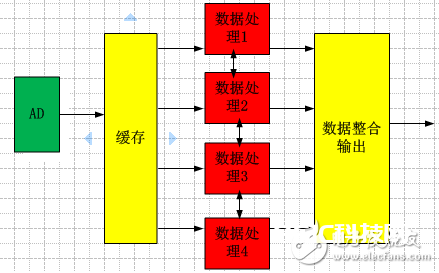

最终依据条件,数据需求接连处理,后边数据的处理要依据前面数据的处理状况决议,而且数据接连不断。

为了满意时序要求,而且不能遗失数据,从头对计划进行规划。

将数据处理模块分红几个小的处理模块。不只下降数据处理速率,一起个处理模块之间彼此联络,后续数据处理可以知道前面数据处理的状况。最终将处理后的数据次序输出即可。