本文给出了快速呼应FSK操控环路模仿前端的详细规划计划。用两片MAX176 ADC别离量化两个输入通道并操控FSK调制器的PLL。这一共同、简略的结构将电路尺度和环路延迟时刻降至最小,然后得到一个简略的FSK调制器。文中介绍了部份经过测验的根本操控回路。

操控回路根底

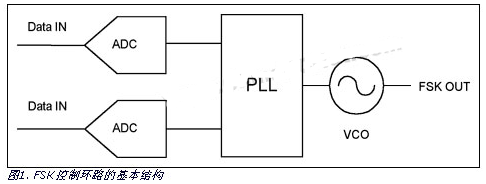

FSK操控回路的模仿前端包含三个首要部件:ADC、锁相环(PLL)、压控振荡器(VCO) (图1)。ADC对输入信号进行数字化处理并操控PLL。PLL确认频率并安稳VCO ,VCO针对给定电压输出一个特定频率。总而言之,这些电路将某一模仿电压转化成一个调制频率。FSK是一种结构简略且呼应速度快的调制计划。

原理图规划及器材选型

图2为模仿前端的结构框图和首要组件,该规划中的ADC有两个功用:数字化输入信号、运用ADC输出操控PLL。这种办法可削减元器材数目,缩小环路延迟时刻,然后简化规划。这儿,输入信号经过两个12 位ADC MAX176进行数字化处理。

运用ADC操控PLL时需求正确挑选PLL,并不是一切PLL都合适该规划。这儿选用Motorola的MC145151 PLL,因为该器材答应以并行办法装载操控数据。MC145151也作业在规划频率规模内:12.0MHz至12.5MHz。挑选1MHz晶振用于MC145151 PLL,divide-by-R装备为000 (divide-by-8)。得到的PLL步长是125kHz (1MHz / 8 = 125kHz)。PLL 的divide-by-N设置为00000001100xxx。divide-by-N设置为5个数值中的一个(终究三位由ADC的数字输出设置)。得到的5个数值是96、97、98、99和100。

本规划运用MiniCircuits POS-25 VCO,因为它在12.0MHz至12.5MHz规模内坚持线性。

别的,四路双输入与非门IC (74HC00)和双路4位计数器(74HC393)为ADC添加时序逻辑,将MAX176装备为接连转化状况。8位移位寄存器(74HC595)用来移出并行格局的ADC数据。带缓冲的可调份额、3位R2R DAC可缩短确认时刻,并放宽锁相环对滤波器目标要求。用R2R梯形结构完成分立的3位DAC,DAC的标称输出对进入VCO的电压进行微调。求和放大器(MAX474)用来对三个电压求和,别离是:

3位R2R DAC的输出,该输出被调整至由ADC输出设置的微调电压,并与粗调电压相加。这一进程使VCO输入电压挨近特定输出频率对应的电压。

粗调电压,该电压是预先设定好的,其值挨近VCO频率预先确认的电压。

相位检测电压,该电压由锁相环设置,并与微谐和粗调电压相加。其意图是调整终究电压以将VCO确认到指定频率。

用三个电压之和(而不是只是依托相位检测器输出)设置VCO,将大大减小PLL确认时刻。

当两个ADC对接踵而来的信号进行数字化时,它们的组合串行输出或许是四个值傍边的一个。输入ADC的EOC信号用来标明一个新的12位字的起点。然后得到以下五种或许的位装备(并得到五种除法值):

1XX – 或除以100或更大的数,合适VCO输出频率大于12.5MHz

(增量为1MHz / 8 = 125kHz,125kHz x 100 = 12.5MHz)

000 – 或除以96,合适VCO输出频率为12.0MHz

(增量为1MHz / 8 = 125kHz,125kHz x 96 = 12.0MHz)

001 – 或除以97,合适VCO输出频率为12.125MHz

(增量为1MHz / 8 = 125kHz,125kHz x 97 = 12.125MHz)

010和011时重复这一办法。假如知道是哪个ADC中的哪一位,能够很容易地确认对应于位格局的频率。运用MAX176时,EOC信号的上升沿标明下个时钟周期输出将呈现一个新字。接纳FSK数据时,有必要进行恰当的解码。

ADC挑选根据

ADC的挑选取决于几个详细规划参数。针对本规划而言,被数字化的信号其带宽相对较低(不到5kHz)。挑选12位ADC 如MAX176时,采样速率为250ksps或更高,留下很大的信号余量。这儿对非线性目标要求不太准确,低功耗特性有助于便携式运用;可是该规划合适接连转化。因为不需求微型操控器,因而简化了ADC接口。许多新式ADC供给了可下降功耗、节约空间,并简化微型操控器接口的计划。MAX1286就是具有这些特色的ADC,这一双通道12位ADC选用8引脚SOT23封装。

操控逻辑电路需求串行输出ADC,可是,假如带有其它逻辑电路,如并行-串行移位寄存器,那么也能够运用并行输出ADC。满意规划要求,具有更高采样率的ADC是MAX1304,它是高速、12位、多路、一起采样ADC,并行输出。

为完成准确丈量,能够运用分辨率更高的SAR ADC,如MAX1069 (14位)或MAX1169 (16位)。这些多路ADC具有较高的直流精度(±1 LSB的INL和DNL)、较大的动态规模(90dB的SNR),以及可选的I2C、SPI或并行接口。

为进行原型规划和根本验证,本规划运用了两片MAX176 ADC。MAX176选用DIP封装,易于在面包板上测验。ADC包含内部采样/坚持电路,0.4μs 收集时刻、内部基准、3.5μs (最大)转化时刻以及低至148mW的功耗。

总结

该规划开发了一个硬件衔接的FSK操控回路,作业在接连形式下,以有限的延迟时刻发送低频带数据。ADC对数据进行数字化处理,ADC输出作为操控位操控PLL,然后得到一个简练、紧凑、元件数最少的FSK解决计划。为使延迟时刻最小,将粗谐和细调电压与相位检测器输出相结合,使PLL确认时刻减到最小。ADC、PLL或VCO的选型取决于详细运用。

责任编辑:gt