这是一份关于ARM1176JZF-S芯片上MMU内存地址转化/映射进程的收拾,内容彻底来自ARM官网的技能手册。

ARM1176JZF-S归于ARMv6产品系列,支撑两种页表项的格局,一种是向ARMv4和ARMv5兼容的格局,另一新是ARMv6的新格局。v4/v5的格局在相应的技能手册里描绘得十分清楚,可是关于v6格局的描绘显得有点散,所以本文只重视ARMv6格局。

内容坚持英文原文,没有翻译避免形成误解画蛇添足。

Level 1 Translation

When the CP15 Control Register c1 Bit 23 is set to 1 in the corresponding world, the subpage AP bits are disabled and the page tables have support for ARMv6 MMU features.

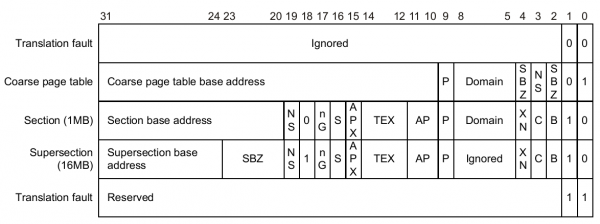

LEVEL 1 DESCRIPTOR FORMAT

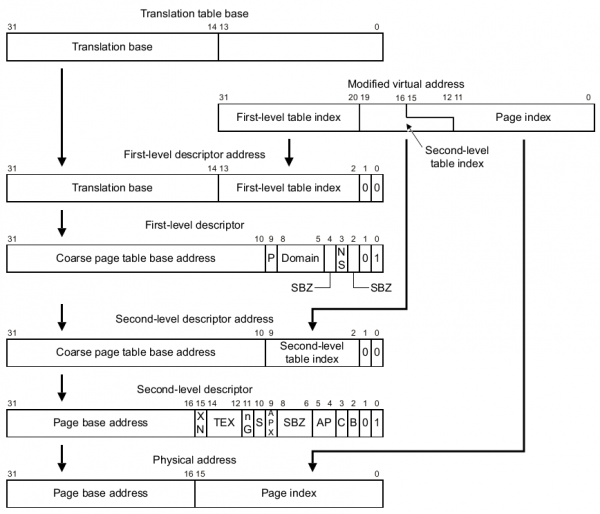

As shown in Figure above, bits [1:0] of a level 1 page table entry determine the type of the entry.

Explanation of each bit:

| Bits | Meaning |

| Bits [1:0] == b00 | Translation fault. |

| Bits [1:0] == b01 | The entry points to a second-level page table, called a Coarse page table. Figure 6.8 shows the formats of the possible entries in the Coarse page table. |

| Bits [1:0] == b10 | The entry points to a either a 1MB Section of memory or a 16MB Supersection of memory. Bit [18] of the descriptor selects between a Section and a Supersection. For details of supersections see Supersections. |

| Bits [1:0] == b11 | Reserved. |

| SBZ | SBZ = Should Be Zero, there bits should be set as 0 value. |

| NS | Defines the world for the processor:0 = Secure, reset value,1 = Non-secure. |

| Domain | A domain is a collection of memory regions. ARM1176JZF-S supports 16 Domains in the Secure world and 16 Domains in the Non-secure world. Domains provide support for multi-user operating systems. All regions of memory have an associated domain. |

| nG | The Not-Global (nG) bit, determines if the translation is marked as global (0), or process-specific (1) in the TLB. For process-specific translations the translation is inserted into the TLB using the current ASID, from the ContextID Register, CP15 c13. |

| S | The Shared (S) bit, determines if the translation is for Non-Shared (0), or Shared (1) memory. This only applies to Normal memory regions. Device memory can be Shared or Non-Shared as determined by the TEX bits and the C and B bits. |

| XN | The Execute-Never (XN) bit, determines if the region is Executable (0) or Not-executable (1). |

| APX | Three access permission bits.The access permissions extension (APX) bit, provides an extra access permission bit.See “Access Permissions”. |

| AP | |

| P | ARM1176JZF-S processors do not support the P bit. |

| TEX | See “TEX, C and B bits”. |

| C | |

| B |

TEX, C AND B BITS

TEX, C AND B BITS PROVIDE OPTIONS FOR INNER AND OUTER CACHABILITY.

The ARMv6 MMU architecture originally defined five bits to describe all of the options for inner and outer cachability. These five bits, the Type Extension Field, TEX[2:0], Cacheable, C, and Bufferable, B bits, are set in the descriptors.

Few applications make use of all these options simultaneously. For this reason, a new configuration bit, TEX remap, bit [28] in the CP15 Control Register, permits the core to support a smaller number of options by using only the TEX[0], C and B bits.

The OS can configure this subset of options through a remap mechanism for these TEX[0], C, and B bits. The TEX[2:1] bits in the descriptor then become 2 OS managed page table bits.

See detail of ARM1176JZF-S Technical Reference Manual 6.6.1 for TexRemap=0 configuration/TexRemap=1 configuration.

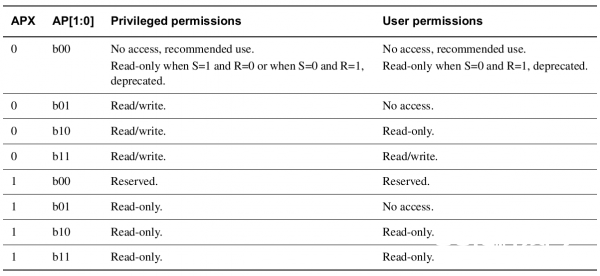

ACCESS PERMISSIONS

The access permission bits control access to the corresponding memory region. If an access is made to an area of memory without the required permissions, then a permission fault is raised.

The access permissions are determined by a combination of the AP and APX bits in the page table, and the S and R bits in CP15 Control Register c1. For page tables not supporting the APX bit, the value 0 is used.

Access permission bit encoding:

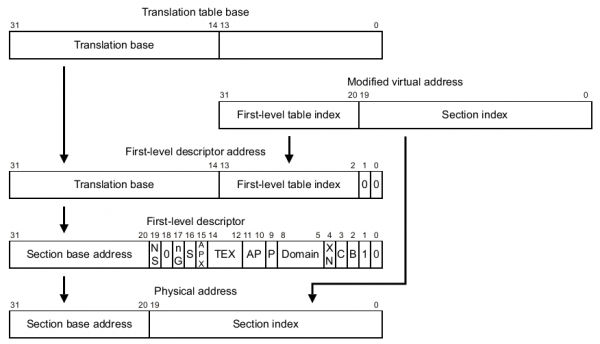

VIRTUAL-PHISICAL ADDRESS TRANSLATION

Translation for a 1MB section, ARMv6 format

Level 2 Translation

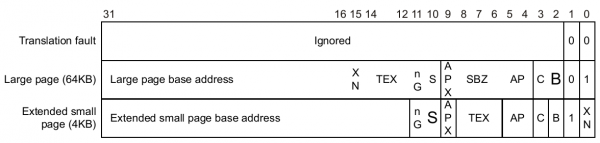

LEVEL 2 DESCRIPTOR FORMAT

Explanation of each bit:

| Bits | Meaning |

| Bits [1:0] == b00 | Translation fault. |

| Bits [1:0] == b01 | The entry points to a 64KB Large page in memory. |

| Bits [1:0] == b1x | The entry points to a 4KB Extended small page in memory.Bit [0] of the entry is the XN bit for the entry. |

VIRTUAL-PHIS%&&&&&%AL ADDRESS TRANSLATION

Large page table walk, ARMv6 format:

4KB extended small page translations, ARMv6 format:

650) this.width=650;” title=”pic06″ src=”http://www.2ndmoon.net/weblog/wp-content/uploads/2013/06/pic06.png” real_src =”http://www.2ndmoon.net/weblog/wp-content/uploads/2013/06/pic06.png” alt=”” width=”791″ height=”671″ data-mce-src=”http://www.2ndmoon.net/weblog/wp-content/uploads/2013/06/pic06.png” style=”color: inherit; font-style: inherit; line-height: 1.625; border: 1px solid rgb(221, 221, 221); cursor: default; padding: 6px; margin-top: 0.4em; height: auto; max-width: 97.5%;” />